Is this a shameful solicitation.

Yes, but in all honesty, I hope it works.

some SS e120r100 is on my wishlist. but, odds are running against me

on the other hand. maybe some other power J-fets can be used.

some that more people can get their hands on.

BTW: i i'm awaiting the new AJ boards before i build

Last edited:

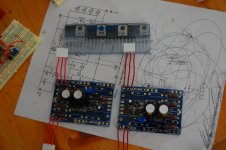

Anybody else using Peter Daniels boards. Just want to confirm J74 pinout. 98% sure, but cant really follow the trace from one of the J74 drains.

TEchinical question:

Since the CCS sets the current through the LTP, what affect does Yfs have on the performance of the FE. Basically, what does doubling up the FE Jfets do? Does the Yfs sum to one larger amount? Lower noise(pretty sure this is true) and distortion?

TEchinical question:

Since the CCS sets the current through the LTP, what affect does Yfs have on the performance of the FE. Basically, what does doubling up the FE Jfets do? Does the Yfs sum to one larger amount? Lower noise(pretty sure this is true) and distortion?

I'm using Peter's boards.

J74 is DGS look here - http://www.datasheetcatalog.org/datasheet/toshiba/1024.pdf

There is an unused hole if you mount a pair of J74 in the place of a J109 (the center hole of the 3-row, I think...)

Also, if you look, you can mount a long trimmer pot in the place of R7. Adjust for zero offset and you are good to go.

Adjust for zero offset and you are good to go.

J74 is DGS look here - http://www.datasheetcatalog.org/datasheet/toshiba/1024.pdf

There is an unused hole if you mount a pair of J74 in the place of a J109 (the center hole of the 3-row, I think...)

Also, if you look, you can mount a long trimmer pot in the place of R7.

....

TEchinical question:

Since the CCS sets the current through the LTP, what affect does Yfs have on the performance of the FE. Basically, what does doubling up the FE Jfets do? Does the Yfs sum to one larger amount? Lower noise(pretty sure this is true) and distortion?

double xconductance means greater OLG

(besides better control of output's gate , which can be desirable ...... or not - if chasing H2/H3)

greater OLG means (with same CLG) more NFB

more NFB means .......... you choose

double xconductance means greater OLG

(besides better control of output's gate , which can be desirable ...... or not - if chasing H2/H3)

greater OLG means (with same CLG) more NFB

more NFB means .......... you choose

This is where I am a little hairy on these things. Am I incorrect in thinking that the IDss of the CCS x Pot setting = needed Vgs for DC bias. If so, Yfs must affect things on the AC side ofthings, correct. Do you measure gain by running sinewave through FE and wacthing what comes out across pot?

This is where I am a little hairy on these things. Am I incorrect in thinking that the IDss of the CCS x Pot setting = needed Vgs for DC bias. If so, Yfs must affect things on the AC side ofthings, correct. Do you measure gain by running sinewave through FE and wacthing what comes out across pot?

take it simple - when using two Jfets in LTP , drain resistor is R

when using 2+2 Jfets in LTP , (common) drain resistor is R/2 (R per drain)

but - xconductance is rising (double ) - think of change in mA/V ( ΔmA per input V) , so you'll having roughly double gain in input LTP

in both cases you'll have and need same Vds for biasing of output

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Pass Labs

- The Aleph Jango

thats a harsh word

thats a harsh word