I need to change 1 ppm to about 10 ppm and 0.000 001 ppm to 0.0001 ppm in section 4.2 and I misspelled PJotr25.

One day I measured Marcel's PWM8 modulator with RTZ and there is also pumping there.

Of course, it is not as visible as in pcm2dsd because Marcel's has less distortion.

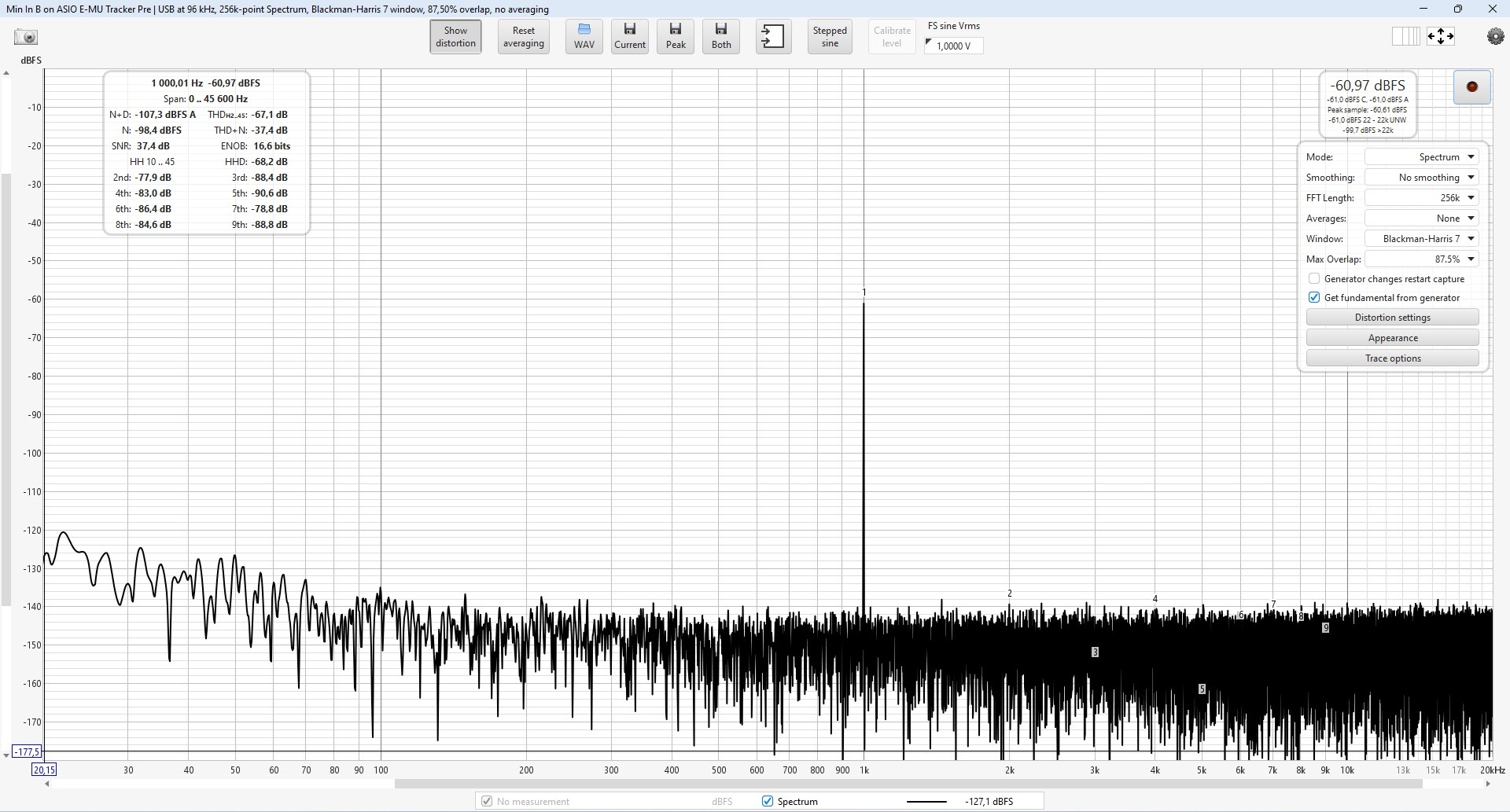

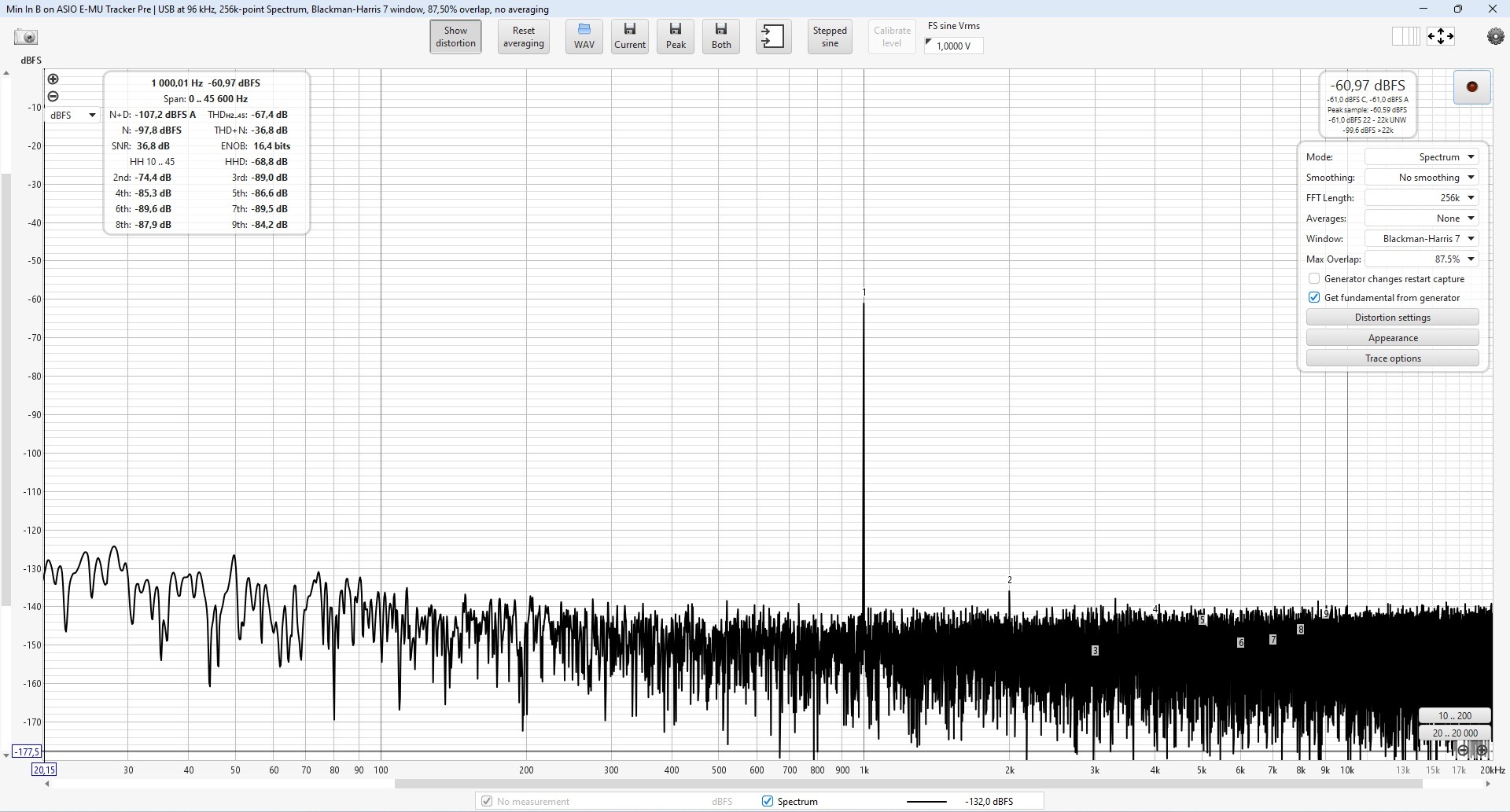

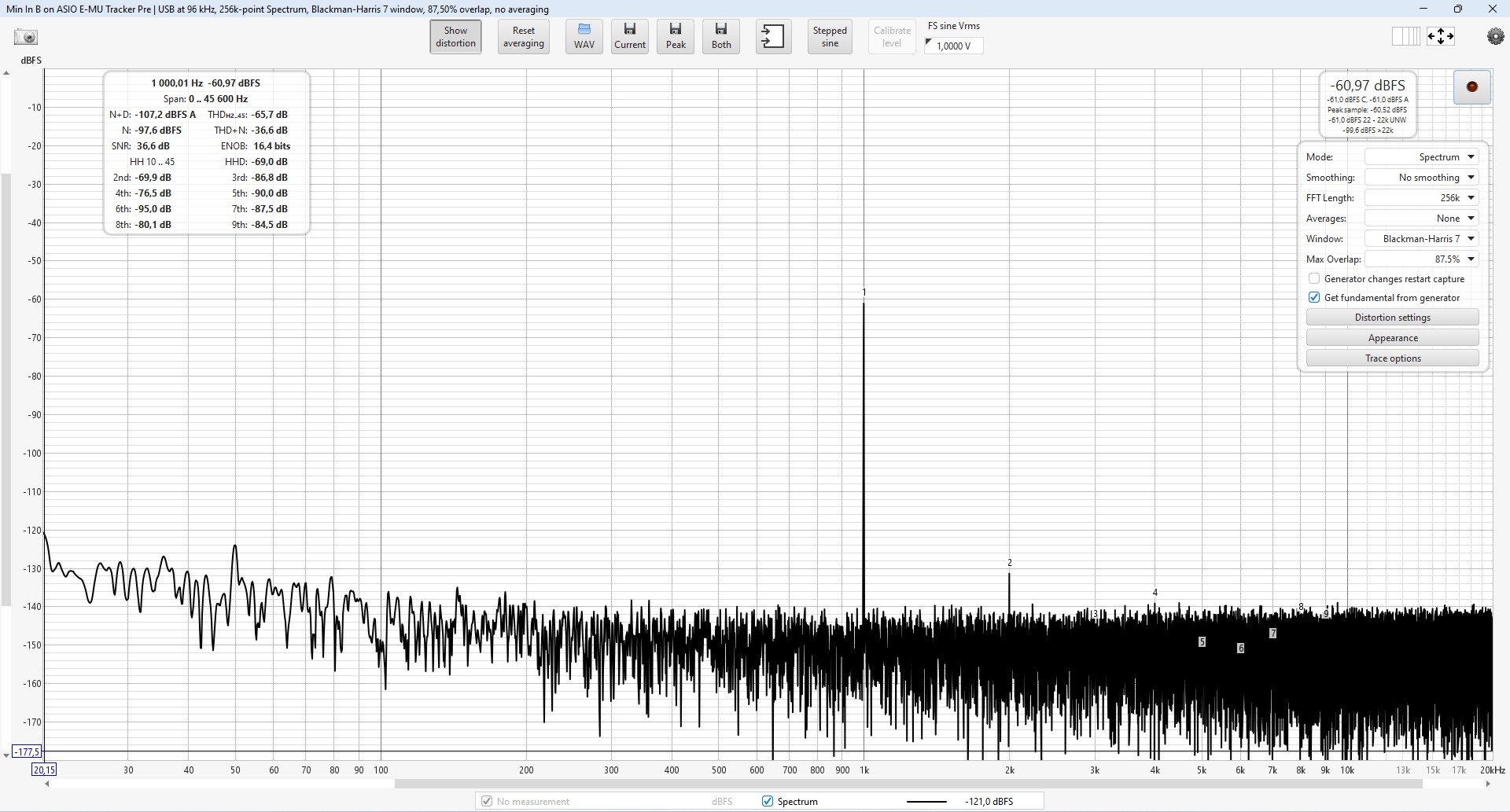

Look at some PWM8 measurements:

Of course, it is not as visible as in pcm2dsd because Marcel's has less distortion.

Look at some PWM8 measurements:

By all means, try it and see. I'm curious to what extent noise folding will affect the noise floor.

There are probably certain other experiments that could also be done, but people with high quality co-clocked DACs and ADCs may not be interested to try some of them. One thing that's cheap and easy to try is to put 120R resistors in parallel with each of the 22uf shift register bypass caps. Another thing that is effective but of greater cost is to use significantly lower phase noise clocking. Things which could be tried but are are more invasive to the dac could include crystal RTZ clocking, and or re-routing of shift register bypass cap current loops.

What standard deviation on the 5nsec shiftregister's delay time should I apply ?By all means, try it and see. I'm curious to what extent noise folding will affect the noise floor.

Hans

I don't know, but when you try it in reality, you don't need to worry about that.

If you want to try it in simulation, you need a simulator that supports transient noise to see the noise folding effects. Does your simulator have a transient noise feature?

A workaround could be to add a random voltage source with the proper density and a bandwidth greater than the reciprocal of the time constant of the track and hold in tracking mode.

https://www.allaboutcircuits.com/te...-transient-analysis-noise-simulation-LTspice/ Another workaround would be to calculate it.

If you want to try it in simulation, you need a simulator that supports transient noise to see the noise folding effects. Does your simulator have a transient noise feature?

A workaround could be to add a random voltage source with the proper density and a bandwidth greater than the reciprocal of the time constant of the track and hold in tracking mode.

https://www.allaboutcircuits.com/te...-transient-analysis-noise-simulation-LTspice/ Another workaround would be to calculate it.

there is also pumping there.

My experience with "pumping" of levels of HD on FFT's has been that it relates to DC instability.

As we involve BOTH ADC and DAC it will be hard to pin down if there is a power supply or reference variation.

It could also be down to the modulator of course. At the orders we need for DSD unconditional stability is unlikely, even in the digital domain.

I guess there is no way to verify either PCM2DSD or PWM8 purely in the digital domain without involving DAC/ADC and or ideally without conversion to PCM (I tried with Weiss Saracon - NDFG).

Is there an FFT Program that works with DSD input?

For @bohrok2610, have you been able to perform a similar test of a commercial IC DAC (ESS, AKM etc) with the same DSD source and got a result without "HD pumping"?

Also, how about using your Cosmos ADC to measure the reference voltage while playing the same test signal?

Thor

There are probably certain other experiments that could also be done

I think at this point, with pumping harmonics we need to ensure we are not stuck up on instrumentation Ghosts.

Thor

Post #2595 has graphs of PCM2DSD with my AK4493 dac. At such low HD levels "pumping" would be difficult to detect.For @bohrok2610, have you been able to perform a similar test of a commercial IC DAC (ESS, AKM etc) with the same DSD source and got a result without "HD pumping"?

Sorry, but I'm not using Cosmos ADC as it is not up to the task (clock syncing not possible).Also, how about using your Cosmos ADC to measure the reference voltage while playing the same test signal?

To sort things out what would we need? I have a basically similar DSD dac here mostly based on Andrea Mori's approach. Its another RTZ FIRDAC. At the moment it still sounds better than Marcel's dac IMHO, which is to say it sounds smoother (while still dynamic), less distorted, and more palatable. What I don't know is whether or not it is "pumping."I think at this point, with pumping harmonics we need to ensure we are not stuck up on instrumentation Ghosts.

OTOH, bohrok2610 has a syncronized DAC/ADC.

Also, one thing that seems pretty clear where I am is that better clocking helps otherwise good DSD dacs significantly. What does that say about the instrumentation clocking, if anything? Is more (close-in) phase noise in the instrumentation system than in the system its trying to measure a possible issue?

Anyway, seems to me with possibly useful devices/resources spread out all over the world, how are we ever going to get some things measured and or sorted out?

If there was, wouldn't still need to have something like Saracon inside it? DSD isn't exactly samples in the time domain, it only is on average. That said it may be possible to remodulate it into mulitibit? Isn't that what ESS and or AKM must be doing to implement digital volume controls? IOW, convert DSD to something like DXD rather than standard PCM.Is there an FFT Program that works with DSD input?

Regarding Saracon in particular, never liked the sound of any of it myself.

Last edited:

Post #2595 has graphs of PCM2DSD with my AK4493 dac. At such low HD levels "pumping" would be difficult to detect.

This was done with the same ADC?

I'm sorry for being so pernickety. I hate it when people do it to me about my own measurements.

But if we can reliably exclude the test setup as contributor to the problems, it helps.

I often enough run into instrument ghosts...

If we can trust our instruments, well, then we can go on bug hunting...

Sorry, but I'm not using Cosmos ADC as it is not up to the task (clock syncing not possible).Also, how about using your Cosmos ADC to measure the reference voltage while playing the same test signal?

Oh, sorry, my bad, I was under the impression measurements were from that. Remind me what you use. Old men are forgetful.

Thor

If there was, wouldn't still need to have something like Saracon inside it?

Hmmm, maybe not?

DSD isn't exactly samples in the time domain, it only is on average.

So is FFT. Funny coindence. I think a kind of FFT can be run on a DSD stream, straight running averages to a given "bin".

Mind you, that level of programming and math is a trifle above my paygrade, I guess we could ask ChatGPT (kidding).

That said it may be possible to remodulate it into mulitibit?

Yes, but that will not I think tell us useful things because we have now multiple conversion domains.

Isn't that what ESS and or AKM must be doing to implement digital volume controls? IOW, convert DSD to something like DXD rather than standard PCM.

Internal data formats are very hush-hush.

There is so much bloody secrecy.

For Fox Sake, for developer seminars Philips gave out transistor level schematics of the TDA1541! What the fudge happened since?

Regarding Saracon in particular, never liked the sound of any of it myself.

I only used it for generating test tones with Wavegene and to do digital domain conversion of FPGA generated and captured DSD Datastreams.

On the test tone side I ended up having much better luck with Mak Sim's (only People who speak Mat AND read the Strugatsky Brothers will get this) ASIO Proxy, doing the DSD test one generation generation on the fly via WaveGene -> AsioProxy -> ASIO....

I do remember throwing hissy fits every time I had to measure DSD, because it was so bleedin' unconvenient.

Thor

My experience with "pumping" of levels of HD on FFT's has been that it relates to DC instability.

As we involve BOTH ADC and DAC it will be hard to pin down if there is a power supply or reference variation.

The ADC and DAC have separate voltage references, so they will drift a bit with respect to each other when the temperature changes. How would that cause pumping?

It could also be down to the modulator of course. At the orders we need for DSD unconditional stability is unlikely, even in the digital domain.

That's correct: the order is typically around five and any normal single-loop sigma-delta modulator of order greater than two is conditionally stable in the control-theoretical sense: reduce its loop gain too much without changing the loop's poles and zeros and it will oscillate. That's true no matter whether the loop filter is analogue or digital.

Why is this relevant?

For PCM2DSD v4, my hypothesis was that there is some extremely small digital offset left, leading to split peaks with a distance well below the resolution bandwidth of the measurement. It sounded plausible until v3 and PWM8 also turned out to have varying distortion levels.

I guess there is no way to verify either PCM2DSD or PWM8 purely in the digital domain without involving DAC/ADC and or ideally without conversion to PCM (I tried with Weiss Saracon - NDFG).

I can and have simulated the spectrum of PWM8 in the digital domain. I can run it longer and do DFTs on several parts of the output waveform.

Mind you, the SRC4392 asynchronous sample rate converter that I use and the interpolation chain are not included. The SRC4392 definitely has something with large time constants on board, namely the sample frequency ratio estimator.

Besides, I usually haven't included the dithered integer arithmetic used in the FPGA code, but rather extended wordlength floating point numbers - except for the quantizer output, of course.

Is there an FFT Program that works with DSD input?

The simulation set-up of Hans can read in a .dsf file and calculate an FFT using LTSpice, if I understand it correctly.

That’s correct.The simulation set-up of Hans can read in a .dsf file and calculate an FFT using LTSpice, if I understand it correctly.

Hans

@PJotr25 With PWM8, did you notice any relation between the pumping frequency and the beat frequency of the input sample clock and the 200 kHz output clock of the SRC4392? For example, does detuning the 27 MHz oscillator by changing the crystal load capacitance make the pumping frequency change?

Yes. These measurements were made with my own ES9822PRO based ADC.This was done with the same ADC?

- Home

- Source & Line

- Digital Line Level

- Return-to-zero shift register FIRDAC