Because we don't the know the audible thresholds - or they differ between individuals so an uncertain and moving target. Those are hard to hit.

I didn't really see anything that suggests that the target's have moved materially in the last 6 decades for things like noise, hd and frequency response.

Maybe I missed the Memo?

This is where we don't agree. For speaker design in normal living room I can accept this stance but I simply see no reason for this in electronics...

I see a reason. It's called TANSTAAFL, aka opportunity cost. By making something better than necessary in one specific metric, usually something else suffers.

I did not even mention speakers... That is a whole 'nother can of slimy wriggly worms, a can I don't' want to open here and now. And don't get me started on microphones.

Thor

Last edited:

Yet, who among us has not been surprised to hear something quite unexpected (sometimes including rather low level effects)?Life is not made easier by the human propensity to hear what we expect. It makes listening tests (including blind and ABX) rather challenging.

A team of neuroscientists of TU Dresden headed by Prof Katharina von Kriegstein presents new findings that show that not only the cerebral cortex, but the entire auditory pathway, represents sounds according to prior expectations.

One such effect was discussed in thread here in the forum: https://www.diyaudio.com/community/threads/paul-frindle-is-this-truth-or-myth.371790/

Also, some findings of audible effects from one of Frindle's AES papers:

https://www.aes.org/e-lib/browse.cfm?elib=7640

Regarding audible thresholds, it should be kept in mind they they are estimates of an average for a population (i.e. an estimate of the center of a bell curve).

That includes the Absolute Threshold of Hearing: https://en.wikipedia.org/wiki/Absolute_threshold_of_hearing

That includes the Absolute Threshold of Hearing: https://en.wikipedia.org/wiki/Absolute_threshold_of_hearing

Mark,

Note, I not suggest that everything sounds the same, but instead that our senses and brain out to fool us and it important to not let ourselves be fooled.

I am familiar with this. And I generally agree on the limits of audibility stated there, where limits are stated.

Noteworthy is (among many others) that distortion below -80dB is not considered audible but DS modulator limit cycles are audible at -100dB.

I would add that H100 of a 20Hz signal is audible at ~ -100dB below the fundamental but that is an extreme case, getting 100dB of H1 of 20Hz is a fair challenge.

It appears we have many very subtle distortion with audibility limits much lower than HD. But that's hardly news and yet it seems to seen by most as an invitation to argue more about lowering HD as if it was a "thing"in itself.

Thor

Yet, who among us has not been surprised to hear something quite unexpected (sometimes including rather low level effects)?

Note, I not suggest that everything sounds the same, but instead that our senses and brain out to fool us and it important to not let ourselves be fooled.

One such effect was discussed in thread here in the forum: https://www.diyaudio.com/community/threads/paul-frindle-is-this-truth-or-myth.371790/

Some findings from one of Frindle's AES papers:

I am familiar with this. And I generally agree on the limits of audibility stated there, where limits are stated.

Noteworthy is (among many others) that distortion below -80dB is not considered audible but DS modulator limit cycles are audible at -100dB.

I would add that H100 of a 20Hz signal is audible at ~ -100dB below the fundamental but that is an extreme case, getting 100dB of H1 of 20Hz is a fair challenge.

It appears we have many very subtle distortion with audibility limits much lower than HD. But that's hardly news and yet it seems to seen by most as an invitation to argue more about lowering HD as if it was a "thing"in itself.

Thor

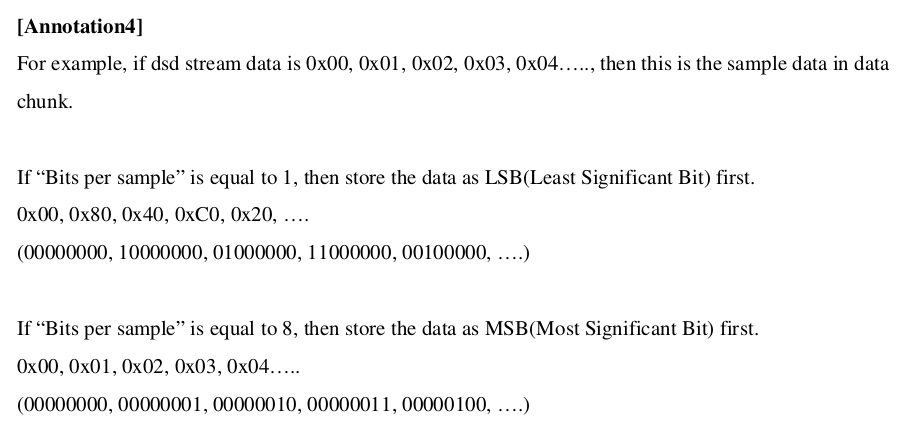

True in what you say, but this image confuses me even more because it does not tell the whether the data bit is 1 or 8.Maybe this picture from DoP specification helps. So oldest bit is stored in MSB. As this data is sent to dac "MSB first", bit processing happens in correct order.

I prefer to stick to the mote explicit white paper.

Why did you mention endianness additionally ?

I’m curious what Marcel can add to the discussion. When I’m wrong, very happy to know before going in great depth with simulations and I will have to correct my routine accordingly.

It could be interesting to see the difference behind reconstruction filter with and without inverted bytes.

Maybe the difference is hardly noticeable because the average value per byte stays the same.

Just another experiment

Hans

I'm not sure what you mean. In that image there are data bits t0-t16 where t0 is the oldest. The data is in 1-bit per sample format.True in what you say, but this image confuses me even more because it does not tell the whether the data bit is 1 or 8.

Assuming the USB-I2S interface is set to 32-bits host sends 4 byte "samples" over USB. Depending on endianness these need to processed in right order at the device. E.g. XMOS expects big endian byte order while ARM MCUs normally expect little endian although some versions of Amanero expect big endian.Why did you mention endianness additionally ?

In Linux this endianness is set in the "DSD quirks" (https://github.com/torvalds/linux/blob/master/sound/usb/quirks.c) for each USB-I2S board based on USB-I2S board's PID/VID. Depending on this setting Linux host sends data either in big endian order or little endian order.

Thx Mark,

The discussion is not concentrated on DoP, this was only referred to showing the huge transfer speed of 66Mhz for DSD 512 over PCM.

For my simulation I just use the straight .dsf file and the question is whether bytes in the .dsf file have to be reversed or not.

Bohrok is convinced this is not the case, but I’m still in doubt.

Hans

The discussion is not concentrated on DoP, this was only referred to showing the huge transfer speed of 66Mhz for DSD 512 over PCM.

For my simulation I just use the straight .dsf file and the question is whether bytes in the .dsf file have to be reversed or not.

Bohrok is convinced this is not the case, but I’m still in doubt.

Hans

My comment referred to the “bits per sample” in the .dsf’s file header which can be 1 or 8.'m not sure what you mean. In that image there are data bits t0-t16 where t0 is the oldest. The data is in 1-bit per sample format.

Hans

Admittedly annotation 4 in post #2552 is indeed misleading as "8 bits per sample" actually just means that MSB is first, not that there are 8 bits per sample. The specification also mentions that LSB first is used (1 bits per sample) so oldest bit is in each byte's MSB.

The specification also mentions that LSB first is used (1 bits per sample) so oldest bit is in each byte's MSB.

When you first put a single-bit sample in the LSB, then the next single-bit sample in bit 1, and so on, then the oldest single-bit sample is in the LSB. The oldest single-bit sample is the single-bit sample that came first.

Not according to annotation 4 in DSF specification.I thought 8 bit per sample just related to the DSD Wide format, also known as PCM Narrow: noise-shaped 8 bit PCM.

Based on annotation 4 LSB first means that oldest bit is stored in byte's MSB.When you first put a single-bit sample in the LSB, then the next single-bit sample in bit 1, and so on, then the oldest single-bit sample is in the LSB. The oldest single-bit sample is the single-bit sample that came first.

Last edited:

I only see that data have to be stored in the LSB first when "Bits per sample" is 1, which implies that the LSB is the oldest sample:

I interpreted the comment about Bits per sample = 8 as that 8 bit signals just have to be stored in the normal way - but I may be wrong, I never tried generating .dsf files with "Bits per sample" = 8.

I interpreted the comment about Bits per sample = 8 as that 8 bit signals just have to be stored in the normal way - but I may be wrong, I never tried generating .dsf files with "Bits per sample" = 8.

In the meantime I have implemented both options, so practice will show what difference it makes.

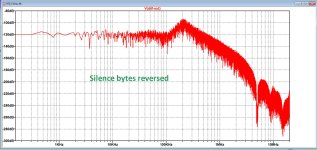

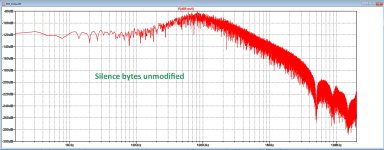

I have made two short runs with silence, first with bytes reversed second unmodified.

Looking at the spectra behind the reconstruction filter, I tend to think that the reversed version, being almost flat up to 100Khz is the right way to process.

I'm surprised how much impact this has.

Hans

P.S. this a file processed with 10Mhz.

I have made two short runs with silence, first with bytes reversed second unmodified.

Looking at the spectra behind the reconstruction filter, I tend to think that the reversed version, being almost flat up to 100Khz is the right way to process.

I'm surprised how much impact this has.

Hans

P.S. this a file processed with 10Mhz.

Attachments

- Home

- Source & Line

- Digital Line Level

- Return-to-zero shift register FIRDAC