Hi,

you need Ian's FIFO and Dual XO. Then you have perfect clock for the DAC.

With the FIFO you do not need change the RPI software.

I do, on the GB, but I would prefer to make it right, rather than correcting it.

Coming back, can someone change the driver or somehow output the sample rate? I understand that it is easy, but I can not make. Not just to decide it is 44.1 or 48k based, but is it 1x, 2x or 4x that. Resolution not needed, I guess we can feed 32clk and the Pi fills according the file resolution.

JG

Coming back, can someone change the driver or somehow output the sample rate? I understand that it is easy, but I can not make. Not just to decide it is 44.1 or 48k based, but is it 1x, 2x or 4x that. Resolution not needed, I guess we can feed 32clk and the Pi fills according the file resolution.

JG

Not sure if this is at all what your after, put a quick google brought a few of these up:

ALSA User — Re: Way to monitor sample rate? Alsaequal.

Not sure if this is at all what your after, put a quick google brought a few of these up:

ALSA User — Re: Way to monitor sample rate? Alsaequal.

Hello,

Thanks,

Do you know if the hifiberry I2S driver use the ALSA driver?

Thanks,

JG

An externally hosted image should be here but it was not working when we last tested it.

Got my raspberry pi dac (diyinhk 5102) working.

I've got to clean it up a bit, put it in a case and use separate power supplies.

Yep. That's what mine's doing

I don't remember off the top of my head, but there is a bit in a register to select the clock source - it's probably in the PCM register block.

There's a thread in the raspberry pi.org forum that's got most of the details - it's a bit long though.

Hi!

Ive searched alot and understand how to change the GPIO18 to input CLK instead of output. But honestly I didnt figure out in which file to do it and what line to change...

Second question. Do I need to recompile after changing to file?

Thanks!

We have been working on this same problem.

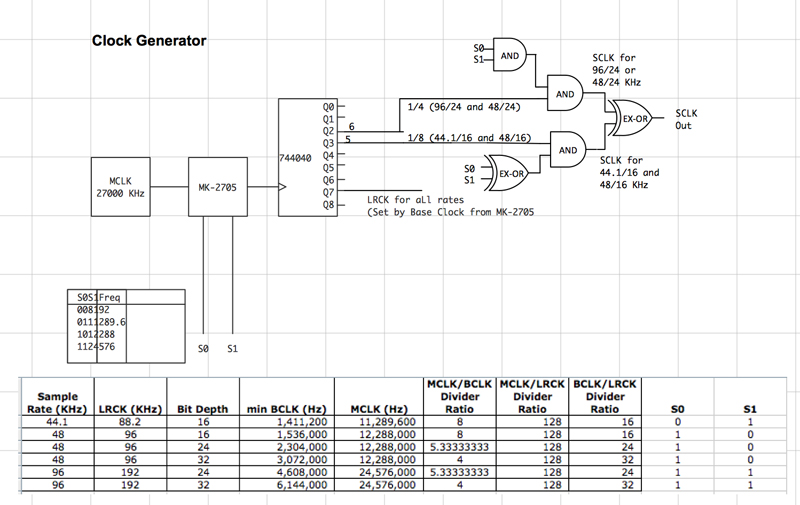

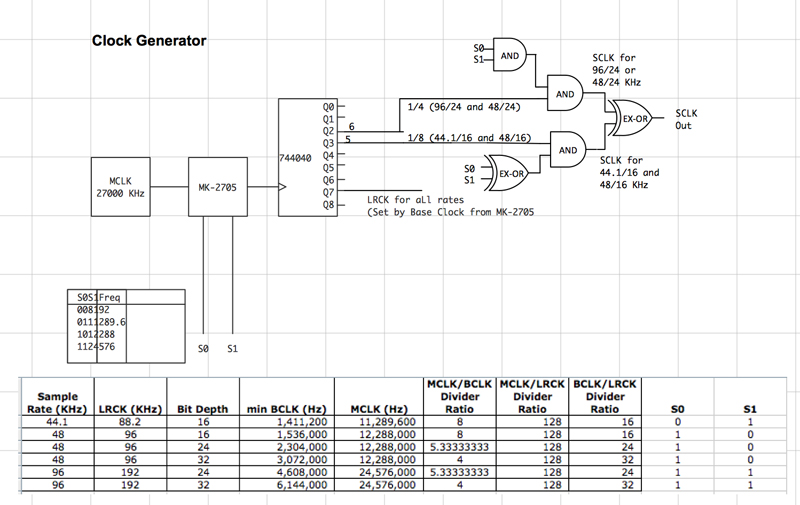

As I understand it, the RPi clocks suck. The RPi can be configured to accept an external I2S BCLK. Apparently the divider in the RPI can be set to various divider ratios (including a fractional divider that dithers the division to to create a crappy version of 44.1 or 48 or 96 from the noisy 19 MHz clock onboard. We didn't want that, since the rest of our system is designed to be bit perfect. The divider is supposed to also be able to generate LRCK from BCLK based on the sample rate of the source. We have allowed for that option, but also generate the proper LRCK from our BCLK, just in case (there is a jumper on our board to set this).

Our system will use the RPi to source a variety of digital content, so we had to generate BCLK for 16/44.1 (1.4112 MHz), 16/48 (1.536 MHz) and 24/96 (6.114 MHz). The 24/96 is problematic, since 24 is not a power of two.. to allow for this most of the components out there use a 32/96 setup, and the lower 8 bits are just ignored.

I used an ASV-24925 27 MHz clock source that drives an IDT MK2705. The MK2705 is a low jitter programmable PLL so you can generate 24.576 MHZ (base clock for 32/96), 12.288 MHz (based clock for 16/48), and 11.2896 (base clock for 16/44.1) by setting combinations of two control lines. I then use a 74HC4040 ripple counter to simply divide these clocks down to get the proper BCLK and LRCK signals. I used some basic logic gates to use these same selector lines to select the various outputs of the ripple counter, so now, simply setting these two lines causes the BCLK and the LRCK to change to the proper values.

The RPI will set these based on the source content, our board will provide the proper clock to the RPI, and we will then clock the data out of the RPi I2S port and into our ASRC, where it gets multiplexed with other external (TOS) and A/D (i.e. LPs) sources and converted to 24/96 for further processing through a MiniSHARC DSP.

The key to this setup, other than some simple logic, is the MK2705.

Here is a screen grab of the basic circuit:

As I understand it, the RPi clocks suck. The RPi can be configured to accept an external I2S BCLK. Apparently the divider in the RPI can be set to various divider ratios (including a fractional divider that dithers the division to to create a crappy version of 44.1 or 48 or 96 from the noisy 19 MHz clock onboard. We didn't want that, since the rest of our system is designed to be bit perfect. The divider is supposed to also be able to generate LRCK from BCLK based on the sample rate of the source. We have allowed for that option, but also generate the proper LRCK from our BCLK, just in case (there is a jumper on our board to set this).

Our system will use the RPi to source a variety of digital content, so we had to generate BCLK for 16/44.1 (1.4112 MHz), 16/48 (1.536 MHz) and 24/96 (6.114 MHz). The 24/96 is problematic, since 24 is not a power of two.. to allow for this most of the components out there use a 32/96 setup, and the lower 8 bits are just ignored.

I used an ASV-24925 27 MHz clock source that drives an IDT MK2705. The MK2705 is a low jitter programmable PLL so you can generate 24.576 MHZ (base clock for 32/96), 12.288 MHz (based clock for 16/48), and 11.2896 (base clock for 16/44.1) by setting combinations of two control lines. I then use a 74HC4040 ripple counter to simply divide these clocks down to get the proper BCLK and LRCK signals. I used some basic logic gates to use these same selector lines to select the various outputs of the ripple counter, so now, simply setting these two lines causes the BCLK and the LRCK to change to the proper values.

The RPI will set these based on the source content, our board will provide the proper clock to the RPI, and we will then clock the data out of the RPi I2S port and into our ASRC, where it gets multiplexed with other external (TOS) and A/D (i.e. LPs) sources and converted to 24/96 for further processing through a MiniSHARC DSP.

The key to this setup, other than some simple logic, is the MK2705.

Here is a screen grab of the basic circuit:

Last edited:

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Digital Source

- Raspberry Pi: external I2S master clock (PCM_MCLK)