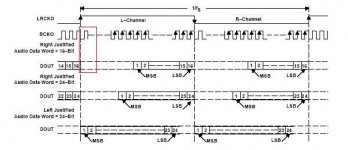

I was thinking to use DIR1703 at 16-bit right just.

so, make a 4-bit counter with bitclock.

with logics, if counter < 1111, DOUT = 0.

if counter >=1111, DOUT = DOUT.

this way, we create a 18bit word and force the 2 MSB to be 0.

does it can work or I realy need to stop bitclock?

DIR1703 is at 8X oversampling. I think the counter + logics will have much delay.

so, make a 4-bit counter with bitclock.

with logics, if counter < 1111, DOUT = 0.

if counter >=1111, DOUT = DOUT.

this way, we create a 18bit word and force the 2 MSB to be 0.

does it can work or I realy need to stop bitclock?

DIR1703 is at 8X oversampling. I think the counter + logics will have much delay.

According to this information from the datasheet of dir1703, I believe these two bits should be zero.

rossl said:can you guarantee that the two bits will always be zero? They are clocked from an unrelated data frame.

😀

Attachments

I disagree. For me, those traces at 0s and 1s suggest an undefined state or a "it doesn't matter" state. That graph doesn't tell those bits are 0s.

People,

I decided to interface de DIR1703 and AD1864 with a SRC4192.

Thanks for your all your help.

I decided to interface de DIR1703 and AD1864 with a SRC4192.

Thanks for your all your help.

Been following a thread elsewhere and it got me thinking about this one. Seems like the don't make 'em like they used to. Sidestepping the contradiction of having a NOS dac with a sample rate converter, might as well use a DF1704 or similar, time was when DIYers were made of tougher, more tenacious stuff not the type to be scared of a little logic.

I'm thinking in some logics again.... without the use of ASRC.

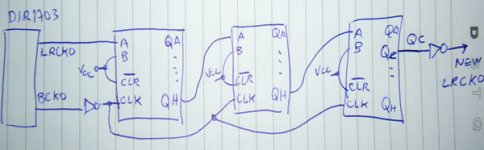

Well, as suggested...

I think to put dir1703 to 24-bit LEFT justif. then generate a new LRCKO from the original. this new LRCKO will change its state after the first 18 bits past.

This will make a 24-bit LEFT to 18-bit RIGHT justif. converter.

The 18 MSB from 24-bit data will be used.

Well, as suggested...

I think to put dir1703 to 24-bit LEFT justif. then generate a new LRCKO from the original. this new LRCKO will change its state after the first 18 bits past.

This will make a 24-bit LEFT to 18-bit RIGHT justif. converter.

The 18 MSB from 24-bit data will be used.

Attachments

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Source

- Question about DIR1703