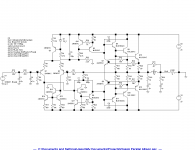

I get the same THD in simulation with one pair or two. My main motivation is the spread the thermal stress out across more devices. I have only ever done class B prior and the extra heat from class A is making me perhaps a little cautious. My simmed 1k THD>8ohm is 0.0000048 and my 20k THD>8 ohm is 0.000846, and it shows it can take an impedance dip to about 5 ohm. In the parallel version I think I'd maybe go with a little more current and do .62 RE just for a little added immunity to impedance variation.

I found it interesting that adding additional outputs in class B designs seems to really improve performance but didn't really change anything in the class A design.

I found it interesting that adding additional outputs in class B designs seems to really improve performance but didn't really change anything in the class A design.

Do you change the emitter resistors when using singles (0.68=> 0.33)?

If so I think the results will not change much. MJL/NJL transistors have such a flat gain characteristic that whether they operate at 1A or 2A will not show so much difference.

I would only parallel them for higher powers.

John

If so I think the results will not change much. MJL/NJL transistors have such a flat gain characteristic that whether they operate at 1A or 2A will not show so much difference.

I would only parallel them for higher powers.

John

John, for the single pair of outputs I was using 0.33 for the emitter resistors. I suppose it makes sense now that you mention the relatively flat gain of these devices that there would be little difference in performance, I just hadn't thought of it.

My notion was to spread the dissipation amongst more silicon. I know the amp will have to dissipate the same amount of heat, I just thought it might be easier on the devices if each was required to dissipate less individually. Maybe the notion is mis-guided. In the end I just wanted to see if I was on the right track for paralleling devices with this type of bias scheme. No one has told me it will explode so it looks like it is worth exploring further. Thanks.

so it looks like it is worth exploring further. Thanks.

My notion was to spread the dissipation amongst more silicon. I know the amp will have to dissipate the same amount of heat, I just thought it might be easier on the devices if each was required to dissipate less individually. Maybe the notion is mis-guided. In the end I just wanted to see if I was on the right track for paralleling devices with this type of bias scheme. No one has told me it will explode

so it looks like it is worth exploring further. Thanks.

so it looks like it is worth exploring further. Thanks.- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Solid State

- Parallel Output with Allison Bias?