Hello

I plan to feed my TDA1545 nos dac direct with eiaj from my cdm12pro2 drive. And here is my problem. Can I feed the drive (clock is 8.4672 MHz) and the TDA1545 in NOS Mode from the same clock?

Maybe use the synchronous reclocking like the swenson schematic published on slimdevices.

I will use a Tent XO

Thank you for help

Toni

I plan to feed my TDA1545 nos dac direct with eiaj from my cdm12pro2 drive. And here is my problem. Can I feed the drive (clock is 8.4672 MHz) and the TDA1545 in NOS Mode from the same clock?

Maybe use the synchronous reclocking like the swenson schematic published on slimdevices.

I will use a Tent XO

Thank you for help

Toni

gochtoni_toni said:I plan to feed my TDA1545 nos dac direct with eiaj from my cdm12pro2 drive. And here is my problem. Can I feed the drive (clock is 8.4672 MHz) and the TDA1545 in NOS Mode from the same clock?

Maybe use the synchronous reclocking like the swenson schematic published on slimdevices.

I will use a Tent XO

Exactly how do you plan to drive the TDA1545 with 8.4672MHz? Typical bit clock for a NOS DAC is 2.8224, 2.1168, or 1.4112 MHz, depending on the frame size.

What’s the purpose of reclocking? The clock outputs from the CDT are derived by dividing the master oscillator using a synchronous counter. A counter is nothing but a collection of latches that are all clocked by the master oscillator. So, if the clocks are the output of a latch clocked by the master oscillator, what is gained by reclocking them with yet another latch clocked by the master oscillator?

The data bits are collected from the CD and assembled in a shift register, which is clocked by the bit clock. A shift register is also a collection of latches and the destination of the data bits is a shift register inside the DAC chip. So, what is gained by reclocking the data bits in between two sets of shift registers (latches); all clocked by the same clock?

The only thing you are likely to gain by reclocking is more jitter, not less? Look at this implementation, for example. http://www.diyaudio.com/forums/showthread.php?threadid=97434

Here the oscillator is driving at least four loads and significant additional trace and wire length. Most oscillators are spec’d for no more than three loads and they perform best with one load and very short traces. More loads and trace length increases the capacitance of the circuit, which slows down the signal transitions. Slow transitions increase the uncertainty as to when the transition crosses the binary threshold and is recognized by the receiving circuit. That results in more jitter. I find it amusing that in your quest to reduce jitter, most of you actually increase it with reclocking.

The received wisdom is that the bitclock signal generated as part of the I2S output of the SAA7324 is a jittter-prone signal, utterly corrupted by the louche activities taking place around it. By contrast, the output of a '163 or a pair of picogate flip-flops is beyond reproach. Or so I am told.

Hello

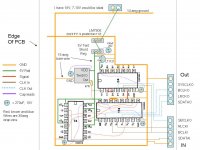

I will use this schematic, its published by John Swenson on slimdevices forum to make synchronous reclocking between a SB3 and an nos dac. I will use 11.xxx mHz on the dac and 33.xxx mHz at the drive. Swenson use a 74hcu04 to fed the clock si´gnal back to the drive. What logic I must use to multiply the 11.xxxmhz to 33.xxxmhz.

Here is the schematic

I will use this schematic, its published by John Swenson on slimdevices forum to make synchronous reclocking between a SB3 and an nos dac. I will use 11.xxx mHz on the dac and 33.xxx mHz at the drive. Swenson use a 74hcu04 to fed the clock si´gnal back to the drive. What logic I must use to multiply the 11.xxxmhz to 33.xxxmhz.

Here is the schematic

Attachments

gochtoni_toni said:Hello

I will use this schematic, its published by John Swenson on slimdevices forum to make synchronous reclocking between a SB3 and an nos dac. I will use 11.xxx mHz on the dac and 33.xxx mHz at the drive. Swenson use a 74hcu04 to fed the clock si´gnal back to the drive. What logic I must use to multiply the 11.xxxmhz to 33.xxxmhz.

Here is the schematic

Where exactly on the dac do you plan to send 11MHz ?

gochtoni_toni said:

I will recklock the bitclock with 11.xxxmHz

I don't think it is a good idea to reclock 2.1168 MHz or 8.4672 MHz with 11.2896 MHz.

Bitclock from the pro2 is 11.xxxMhz same with Cs8414 Receiver

look at datasheet from the SAA7324 Contoller

http://www.daisy-laser.com/products/CD/modules/CDPro2/SAA7324_2.pdf

kind regards

Toni

look at datasheet from the SAA7324 Contoller

http://www.daisy-laser.com/products/CD/modules/CDPro2/SAA7324_2.pdf

kind regards

Toni

gochtoni_toni said:Bitclock from the pro2 is 11.xxxMhz same with Cs8414 Receiver

look at datasheet from the SAA7324 Contoller

http://www.daisy-laser.com/products/CD/modules/CDPro2/SAA7324_2.pdf

kind regards

Toni

I see. Have a look at page 18, not that it matters. The CDM12 PRO2 uses the SAA7345.

vt4c said:Toni,

The CDM12 Pro2 drive puts out I2S in default mode. You'll need to configure the CDM12 Pro2 to put out EIAJ format that the TDA1545 recognise.

Wrong!

It's the TDA1543 which has versions A/non-A with EIAJ/I2S interfaces respectively. The TDA1545 only comes in A version, with i2s only.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Digital Line Level

- One clock for CDM12 Pro2 and Nos Dac TDA1545