Hello everyone,

I'm planning to design a DAC with the ES9033 chip. For this purpose, I read the ES9033 datasheet several times. I want to design a tiny and efficient board, for example I'm considering a low noise ldo like LP5907-33 for supply. The DAC will operate entirely in hardware mode and DSD will not be used.

I have solved all the other issues in my mind, but I am confused about the I2S input. Namely;

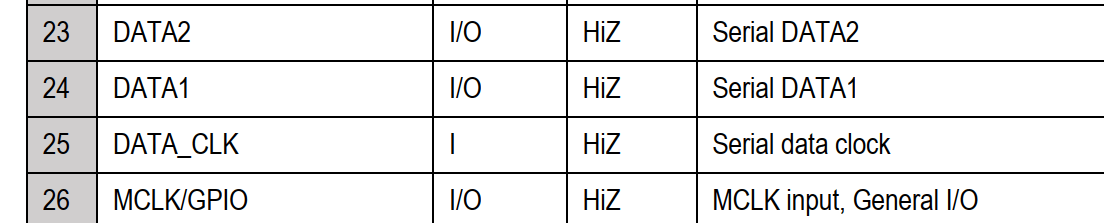

According to the ES9033 datasheet, the chip's I2S inputs for PCM are DATA1-DATA2-DATA_CLK and MCLK. It is clear that DATA_CLK = BCK and MCLK = MCLK. However, as far as I understand, DATA1 is the Left Channel Data, for example, while DATA2 is the Right Channel..

In this case, do I need to separate the DATA line as right and left with a simple logic and LRCK clock at the I2S input and enter these lines?

Or is there a system in the chip to use these two DATA lines with LRCK?

I'm planning to design a DAC with the ES9033 chip. For this purpose, I read the ES9033 datasheet several times. I want to design a tiny and efficient board, for example I'm considering a low noise ldo like LP5907-33 for supply. The DAC will operate entirely in hardware mode and DSD will not be used.

I have solved all the other issues in my mind, but I am confused about the I2S input. Namely;

According to the ES9033 datasheet, the chip's I2S inputs for PCM are DATA1-DATA2-DATA_CLK and MCLK. It is clear that DATA_CLK = BCK and MCLK = MCLK. However, as far as I understand, DATA1 is the Left Channel Data, for example, while DATA2 is the Right Channel..

In this case, do I need to separate the DATA line as right and left with a simple logic and LRCK clock at the I2S input and enter these lines?

Or is there a system in the chip to use these two DATA lines with LRCK?

It's just my guess, the datasheet is incomplete. For confirmation I would recommend to ask ESS techs or their representatives. I always address a very helpful professional from Astute Group (originally ISMOsys), they seem to cover Turkey too https://www.esstech.com/sales-offices/

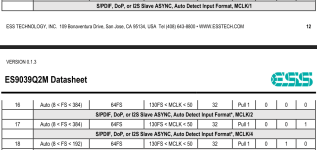

Hi, I have a few questions regarding the ES9039Q2M:

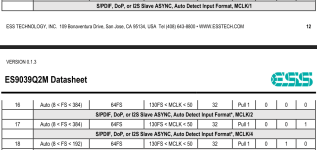

I want to configure it in Hardware Mode, and I will exclusively use the spdif interface, is Harware Mode 18 the most appropriate?

The mode being ASYNC, the oscillator frequency does not have to be a multiple of 44.1 or 44.8? Can I just use a 25MHz oscillator?

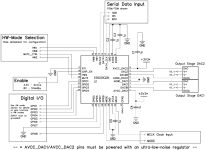

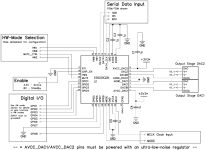

Obviously the reference diagram is wrong regarding the power pins? The AVDD and VCCA pins should be powered and not grounded as in the diagram?

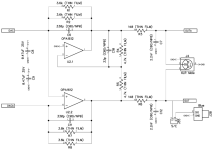

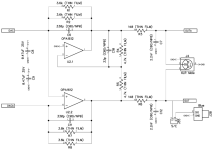

Finally, last question: I don't plan to integrate XLR connectors into my design. Should I keep the output stage the same as the diagram, just removing the XLR connector, or can I remove the net RC filter of the 'OUTb' net, shown at top right?

I want to configure it in Hardware Mode, and I will exclusively use the spdif interface, is Harware Mode 18 the most appropriate?

The mode being ASYNC, the oscillator frequency does not have to be a multiple of 44.1 or 44.8? Can I just use a 25MHz oscillator?

Obviously the reference diagram is wrong regarding the power pins? The AVDD and VCCA pins should be powered and not grounded as in the diagram?

Finally, last question: I don't plan to integrate XLR connectors into my design. Should I keep the output stage the same as the diagram, just removing the XLR connector, or can I remove the net RC filter of the 'OUTb' net, shown at top right?

Hardware modes 16-18 should all work depending on your oscillator frequency.want to configure it in Hardware Mode, and I will exclusively use the spdif interface, is Harware Mode 18 the most appropriate?

Yes. For ASYNC modes non-audio oscillator frequency works best.The mode being ASYNC, the oscillator frequency does not have to be a multiple of 44.1 or 44.8? Can I just use a 25MHz oscillator?

Yes, AVDD and VCCA should be powered by 3.3V. Although they are not grounded in the diagram.Obviously the reference diagram is wrong regarding the power pins? The AVDD and VCCA pins should be powered and not grounded as in the diagram?

Yes, you can leave out the XLR and the RC from OUTb.Finally, last question: I don't plan to integrate XLR connectors into my design. Should I keep the output stage the same as the diagram, just removing the XLR connector, or can I remove the net RC filter of the 'OUTb' net, shown at top right?

- Home

- Source & Line

- Digital Source

- ES9033Q Question...