Hi guys,

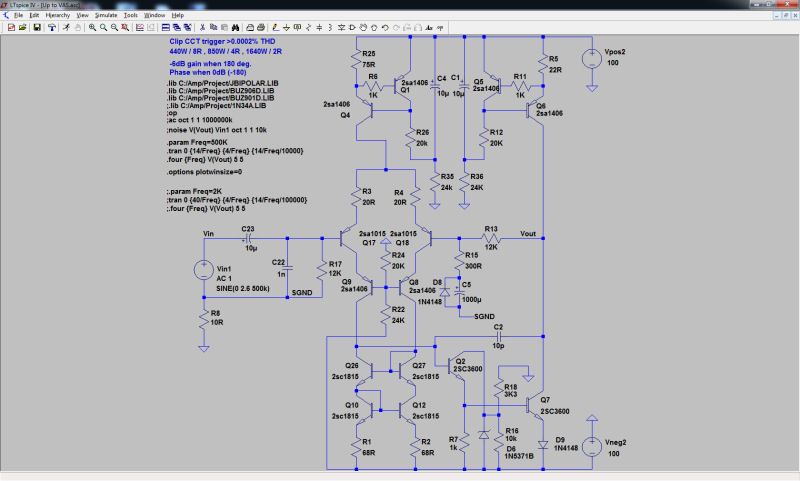

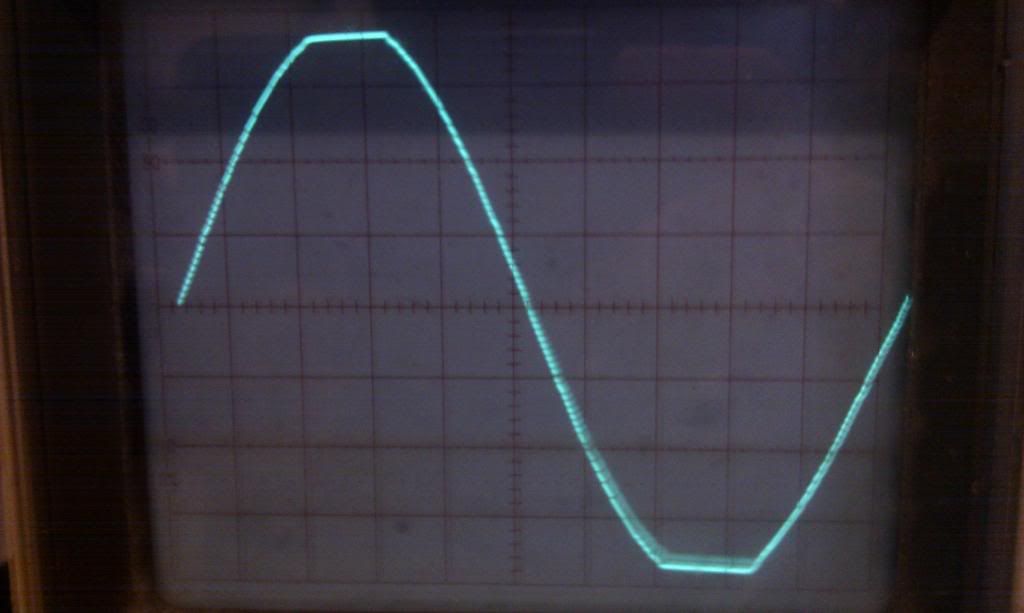

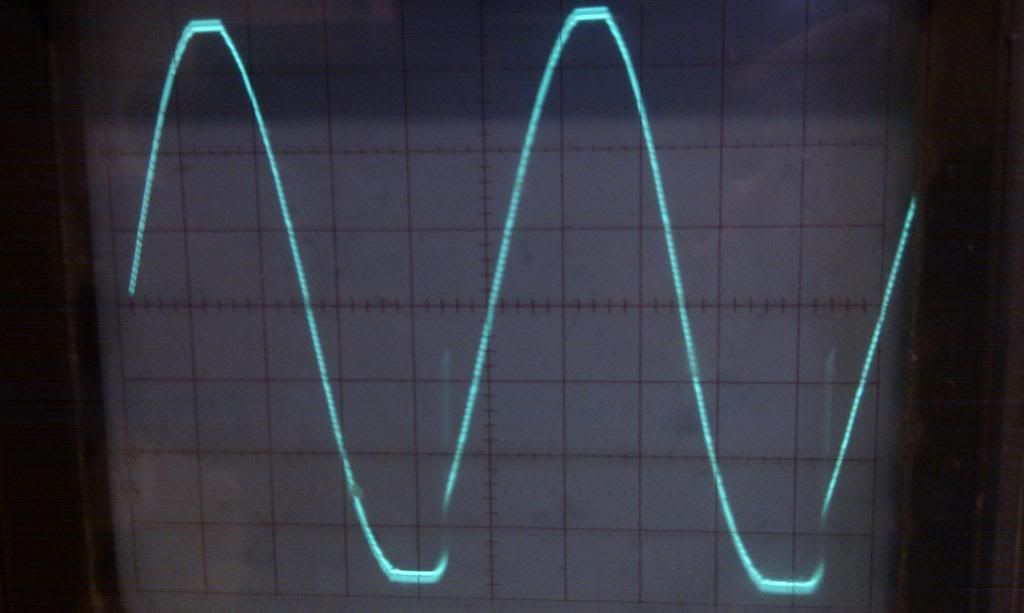

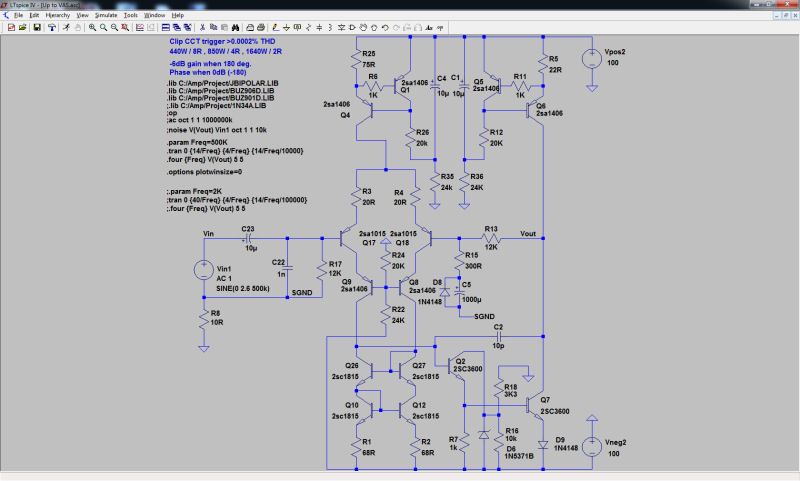

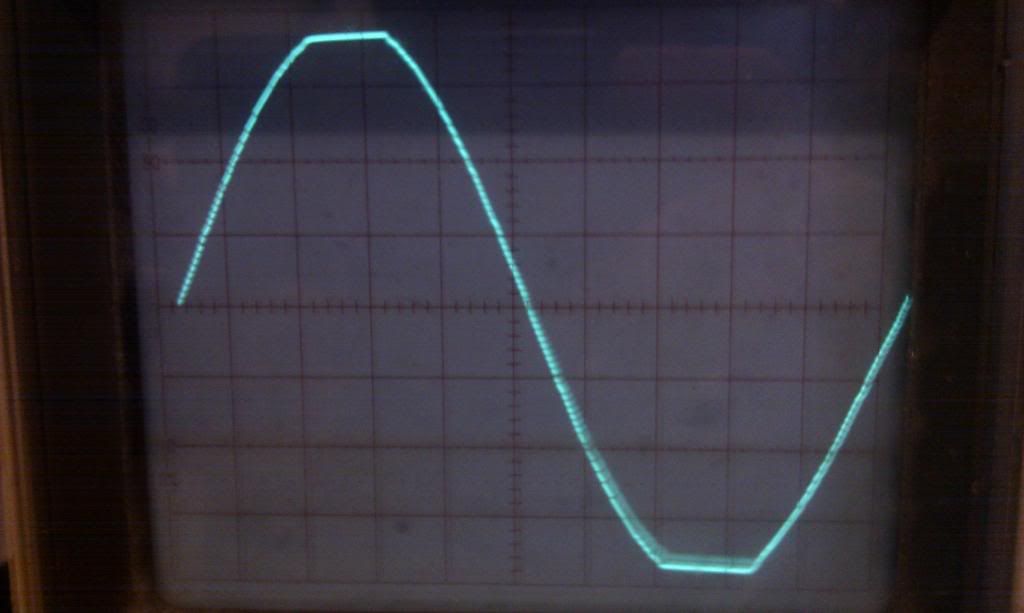

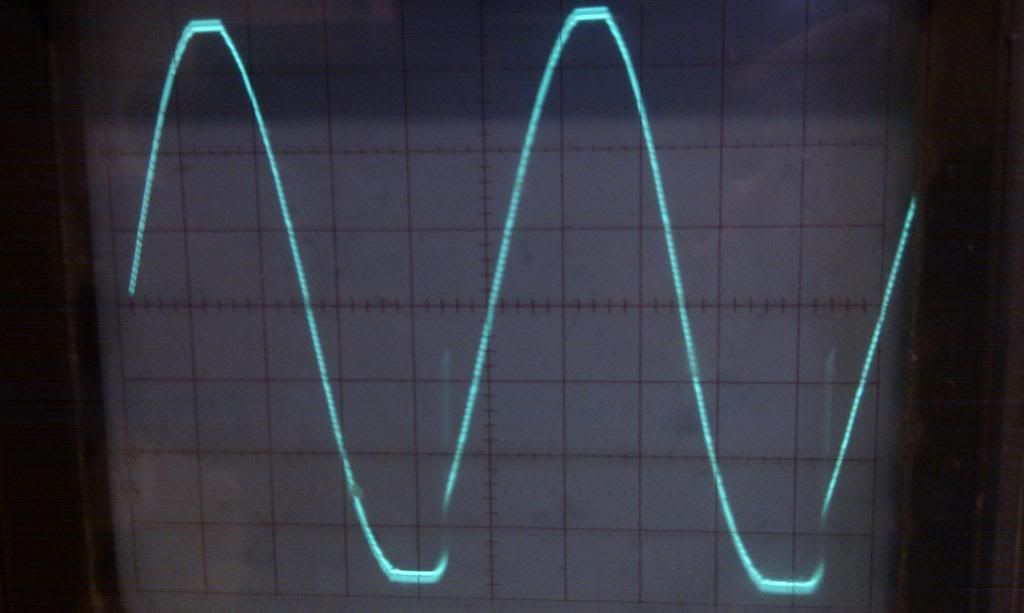

On a power amp I'm designing I have a strange clipping behaviour that does'nt show up on simulation. In the negative half cycle the transistor seems to 'stick' on, followed by a turning off spike. This happens at higher frequencies, and gets worse as frequency increases. I was wondering if someone could point me in the right direction as to what could be causing it. I have attached some oscilloscope pics and a pic of the circuit to help clarify what I mean. The fuzziness in the second pic ( clipping with no spike ) is due to the glass on the CRO.

Thanks.

On a power amp I'm designing I have a strange clipping behaviour that does'nt show up on simulation. In the negative half cycle the transistor seems to 'stick' on, followed by a turning off spike. This happens at higher frequencies, and gets worse as frequency increases. I was wondering if someone could point me in the right direction as to what could be causing it. I have attached some oscilloscope pics and a pic of the circuit to help clarify what I mean. The fuzziness in the second pic ( clipping with no spike ) is due to the glass on the CRO.

Thanks.

you could post the asc - I put the nonstandard lib part's model defs right in the schematic for max portability - use the spice directive tool

"wind up" and saturation can make for bad clipping recovery

output Q saturation can be improved with a Baker Clamp

may need to clamp the mirror too

and I don't think the complication/extra diode drop of the Wilson circuit is very useful with discretes - try just the 2 Q mirror

"wind up" and saturation can make for bad clipping recovery

output Q saturation can be improved with a Baker Clamp

may need to clamp the mirror too

and I don't think the complication/extra diode drop of the Wilson circuit is very useful with discretes - try just the 2 Q mirror

Last edited:

Your lower half of the amp is saturating. Simulator models do not model saturation and charge storage well and in most cases at all, hence you won't see it in the simulation. So, as Bob Pease used to say, in theory there is no difference between theory and practice, but in practice there is. Welcome to the real world

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.