The works of MV audiolab are well know from many of us from time ago , wake up dude 😎

yours instead are unknown 😒

you miss the point , this forum is DiyAudio , the place where people DO , with the help of those who DID and DO and share , no place for lessons givers that you like so much , don't be that hard with yourself , after having done something you'll feel some release 😎

.

yours instead are unknown 😒

you miss the point , this forum is DiyAudio , the place where people DO , with the help of those who DID and DO and share , no place for lessons givers that you like so much , don't be that hard with yourself , after having done something you'll feel some release 😎

.

Last edited:

Well, all the guys whom have an Aya2 and furthers from 2014 tell you'are wrong, but indeed whom am I to told you to land !

All the best 😉 ... waiting myself to read what is your contribution here but lessons given to others !

All the best 😉 ... waiting myself to read what is your contribution here but lessons given to others !

Yourself is roaming around all along telling other people what to do , is this what you came here for 🙄

I came here after having read an article from Nelson about his work , and I found it very interesting, the man and his work , this is it dude , you have no idea how far you are from the spirit of this place ...........

What I share is what I do , in this very real world , and thanks to this forum 👍

you know what , I am listenning my F6 https://www.diyaudio.com/community/threads/liquid-cooled-f6.299312/ , made thanks to the genius of one man who share more than you'll never do .......

.

I came here after having read an article from Nelson about his work , and I found it very interesting, the man and his work , this is it dude , you have no idea how far you are from the spirit of this place ...........

What I share is what I do , in this very real world , and thanks to this forum 👍

you know what , I am listenning my F6 https://www.diyaudio.com/community/threads/liquid-cooled-f6.299312/ , made thanks to the genius of one man who share more than you'll never do .......

.

Last edited:

With all due respect Thorsten, if low jitter is the goal here (its been my goal at least), then removing RFI/EMI noise generated on the same die as sensitive DAC circuits- surely this would be beneficial?

The question is how much of such noise is really generated. Let's see how the outputs work:

(Images from mval)

Now mval argues that the capacitors correct the error of the system and thus once the system is in a stable condition, we can stop the DEM oscillator completely.

I used to have a fat folder with the entiere TDA1541 Schematic at transistor levels - this was from Philips themselves as part of a course for designers about the TDA1541 - the understanding I got was different, however the folder is (sadly) lost to time and my memory ain't what it used to be (hey it never was that anyway), so I will not insist on the absolute rightness of what I did.

I did what I always do, the best I could do, based on the best understanding I had when I did it.

What happens is the signal from the latch (note, it is differential) either turns a transistor on or off.

In on state it will "evacuate" the current of this Bit to +5V (labelled Vref) and the diode connected transistor is reverse biased.

In off state the transistor does not conduct and the diode connected transistor is now forward biased, the bit current flows through a cascode darlington and into another cascode transistor after which we have a resistor and the "DEM" capacitor.

What happens if we disconnect this capacitor? Nothing. As long as the circuit is STABLE.

Now let's switch the bit state from on to off. We are turning OFF a saturated BJT and we are turning on a reverse biased diode. Will the charge being removed from one flow into other and net off exactly? If not, where does that charge go? What completes the AC circuit?

I can understand from your point of view that a 50 Hz modulation will occur and probably other issues, but its so low it doesn't seem likely to be of any concern.

Well, blue is 100kHz (not synchronised to the audio clock I believe) and red is 100Hz. I really don't like what the 100Hz DEM does to the graph. The 100Hz IMD is quite high in level, with the potential for audibility.

It is similar to 100Hz jitter you get from a Clock regulator that isn't actually regulating because it's in dropout and your 100Hz ripple is now providing FM on your master clock. I found it very audible and did not like what I heard.

The fact that machine was sounding "wrong" in fact tipped me off, check on AP2, 100Hz sidebands, but where are they from?

Please forgive my ignorance, im just a diyer trying to learn and have a bit of fun. To my ears at least the trade off seems worth it (if there is any?)

This is in the end what matters, if you like the result, who am I to tell you that you are wrong. You are not.

It would be a very interesting test to measure the 'jitter' at the 1541 analog outputs with 50 Hz DEM, 705khz DEM, and some type of DEM sync with BCK (Grundig DEM sync for example, or CD-77 solution).

I did measure Jitter using AP2 on the CD-77. Or more precisely, I failed to measure anything notable, using a CD with a J-Test signal burned on it.

Given the frequencies DEM operates at and the parasitics involved, I don't really think we gain much by placing the capacitors below the TDA1541, it is more important to have a separate ground island (in a 4 layer PCB) for them that returns the current flowing to the correct "ground".

The CD-77 used 2 layer PCB's (I now routinely do 6 layer, but that was long ago. Here what we did:

Solid ground plane at the bottom, separate plane for DEM capacitors, small islands for power with special "XY" capacitors that have a central terminal and two outer ones.

It is not what I'd do today, but it was on a 2 layer board and nearly 2 decades ago.

Thor

PS, guy's, please relax, it's only audio, not the Ukraine or Gaza war. Let's keep it friendly. No need for hero worship (I am not above criticism) and let respect each others experiences. I find there is always something to learn.

Attachments

Last edited:

@ThorstenL much appreciated for all the info. I've yet to start my tda1541a adventure, and for sure it will be a 4 layer (SIG+PWR/GND/GND/SIG+PWR) design. But with probably just 2 chips (using 10 is quite expensive, but hey, might sway my mind, honestly fpga programing would take me a lot of time to learn atm). As for separate gnd for DEM, you reckon to just utilize one gnd plane only for it? Where would you connect it with agnd?

.... Tit is more important to have a separate ground island (in a 4 layer PCB) for them that returns the current flowing to the correct "ground".

Let's talk about that , I think it is a good matter to talk about 😉

.

I've yet to start my tda1541a adventure, and for sure it will be a 4 layer (SIG+PWR/GND/GND/SIG+PWR) design.

I suggest to first look at signal and power flows and make the physical arrangements of the circuit so that there is a natural flow of signal and power.

Also, read H. Ott on designing for low EMI and generally low digital noise.

For CMOS logic it is recommended to have a signal layer between a Vcc and Vss plane. Top and bottom of the PCB should have ground fill with stitching to the actual GND/Vss plane.

DO NOT put anything to "isolate" the power supplies. CMOS logic is push-pull and current loops for charging/discharging the input capacitance are completed via the shortest route, which can be either Vcc or Vss, depending if the edge goes high/low.

DO NOT use audiophile approved bypassing with multiple values, instead find your dominant frequency, pick ONE capacitor with a resonance near the clock fundamental OR third harmonic.

So if our dominant clock is ~ 12MHz, ideally we use capacitors with a 36MHz resonance and put 4 pcs around each smaller (TSSOP14-24), 2pcs for "popcorn logic" and as many as possible for larger (> 24 pins) IC's.

An 0603 form factor 33nF (0.033uF) has ~ 40MHz minimum impedance with 30mOhm minimum impedance, so that would be the "ideal" choice here.

Often just using 0.1uF/0603 will be fine if you use enough. These have 20mOhm minimum at 23MHz and at 40MHz around 100mOhm impedance. If you have 4pcs around a single small logic IC that gives you 5mOhm @ 23MHz & 25mOhm @ 40MHz locally and once we include the inductance and resistance of the power planes (Vss -> normally called "GND" should be considered a "power" and "signal return" Pin.

Stick some distributed large value Os-Con's around the PCB, like 820uF/6.3V.

NOTE, all the above is for all the CMOS Logic, NOT TDA1541. It also means you possibly want more than 4 Layers.

For a 4-Layer stackup I would go with(top to bottom):

1) Signal/GND-Fill (for "slow signals" and component side)

2) Power Plane (Vcc for CMOS)

3) Signal/GND-Fill (for "fast edge signals", source terminated impedance strip lines)

4) Ground Plane (Vss for CMOS)

Once we transition from high Speed CMOS logic into the EC-Logic/TDA1541 domain (or analogue/clock for CMOS based DAC's), use "islands" for the individual power supply and / or signal return planes.

Do not cut or section the actual ground plane, you can use it to

So I would place the DEM Capacitor "gnd" island onto layer 3 and link to "GND" at AGND Pin of TDA1541. The +5V/-5V & -15V would be Islands, as large as sensible.

With one TDA1541 per channel I'd probably use one loop and one AC winding per channel, the power supplies likely "Sziklai" type Shunts (third circuit on this page https://www.tnt-audio.com/clinica/regulators_noise3_e.html) using BCP53 as PNP and Cascoded Current Sources as series element, I usually put a gyrator on the other end that acts likes a very large value virtual inductor.

I would look at the inputs and use some form of limited swing and slowed edge circuit and I would inject a BCK/MCK linked clock into the DEM oscillator (likely HtP circuit) and make a cascaded divider with options of anything from 705.6/768kHz down to 43.066/46.875Hz so you can try each frequency across the range and pick whatever you like.

For DEM capacitors, up to 1uF in Film (Panasonic ECPU etc.) with a PCB Pattern for 1206/1210 with higher update speeds and for electrolytic options I'd likely put a 2920 PCB pattern so I can use low leakage tantalum types in 100uF/25V for very low DEM frequencies.

Decoupling of the TDA1541, FIM Cap's (same as DEM capacitors) close to the IC package, 820uF Os-Con (or lower value for -15V) and then hand over to the shunt regulator.

Now, this is ONLY "what I would do" not "the only way" and how I would I build in some flexibility to make a few PCB's in different configurations for listening tests to compare things like ~50Hz DEM etc.

Thor

Hi Thorsten,

Thanks for the detailed reply, much appreciated.

I suppose the only thing left on my mind that I ask myself- Is the EMI emitted by the DEM (running at high frequencies) enough to induce a voltage differential at latch enable to alter the timing in some way, maybe even a few femto/pico volts at the right time could influence this perhaps. This theory is the impression I got from the way ECdesign explained his reasoning for the idea, I think its fair to say the theory may have some merit. At least that's how I would describe the reasoning for the change in perceived sound quality. On the other hand I could be way off and just like the sound of the different harmonics produced by the affect. 😆

Thanks for the detailed reply, much appreciated.

I suppose the only thing left on my mind that I ask myself- Is the EMI emitted by the DEM (running at high frequencies) enough to induce a voltage differential at latch enable to alter the timing in some way, maybe even a few femto/pico volts at the right time could influence this perhaps. This theory is the impression I got from the way ECdesign explained his reasoning for the idea, I think its fair to say the theory may have some merit. At least that's how I would describe the reasoning for the change in perceived sound quality. On the other hand I could be way off and just like the sound of the different harmonics produced by the affect. 😆

Ryan,

I think you still do not understand how EC-Logic (ECL) works. And ECL is internal in the TDA1541, even the inputs are actually ECL, but single ended.

ECL is differential, a differential pair on a current source, the transistors normally do not enter saturation. It is in effect a high speed differential analogue circuit.

In the age of TTL and Low Power Schottky TTL with (respectively) 3MHz and 30MHz (appx.) maximum flip-flop clocks, ECL easily got to 300MHz which is impressive for the 1970's, heck, it's impressive today! Even more impressive is that the PSU current only has tiny amounts of what is in effect HD of a linear differential circuit.

I used ECL dual flip flop (Russian mil spec., incredibly hard to get) for the predivider in a frequency counter for a DIY FM Tuner (next divider Schottky TTL, then TTL and finally CMOS) appx. 1979. I tried digital frequency synthesis but could not get it to work without MCU, a simple counter worked great and got me a digital readout with obscenely expensive and hard to get 7 segment LED's.

These days ECL survives mainly as "LVDS" which can be interesting for clock.distribution especially or to "semi-isolate" signals.

All this means all logic inside the TDA1541 REALLY is very low noise.

The only weak points are the inputs because they are single ended input (though the circuit inside the TDA1541is actually differential) and can be overdriven by either excessively fast edges (sleeing the input stage and coupling noise into the IC substrate) from the source or by driving the input outside the linear range.

Technically, the point where we transition from differential, non saturation ECL to saturated single ended bipolar switches and diodes to switch the currents, but that is inherent to making a DAC with SE Outputs.

Had the DAC been made inherently differential it could have used non saturated emitter followers as bit switches and diodes without reverse bias recovery.

As said, all thinking coming from CMOS circuitry is not useful for TDA1541 and only causes one to pursue dead ends.

Most important IME are:

1) DEM synchronisation

1) Soft Inputs (edge speed limited and keeping inputs in the linear operation)

2) PSU loop control, very low PSU Impedance is IMNSO overrated for TDA1541, it is more important to make the current loop follow the correct path

3) DEM capacitor quality (once their leakage is low and the impedance at the DEM frequency and a few octaves up is sufficiently low)

Things like going differential or using simultaneous mode at low speeds give benefits mainly if the list above is not checked off.

Again, I'm no guru nor do I have the (w)holy truth, just my experience with TDA1541. I have not done any work with in the better part of a decade.

Thor

PS, In my earlier post I asked "the stored charge in the bit switches and associated diodes needs to go somewhere, what completes the AC current loop?"

The answer is, the DEM capacitors to output, via ground and the output to +5V.

It might be beneficial to connect the DEM capacitor common to +5V, never got around to trying that though.

I think you still do not understand how EC-Logic (ECL) works. And ECL is internal in the TDA1541, even the inputs are actually ECL, but single ended.

ECL is differential, a differential pair on a current source, the transistors normally do not enter saturation. It is in effect a high speed differential analogue circuit.

In the age of TTL and Low Power Schottky TTL with (respectively) 3MHz and 30MHz (appx.) maximum flip-flop clocks, ECL easily got to 300MHz which is impressive for the 1970's, heck, it's impressive today! Even more impressive is that the PSU current only has tiny amounts of what is in effect HD of a linear differential circuit.

I used ECL dual flip flop (Russian mil spec., incredibly hard to get) for the predivider in a frequency counter for a DIY FM Tuner (next divider Schottky TTL, then TTL and finally CMOS) appx. 1979. I tried digital frequency synthesis but could not get it to work without MCU, a simple counter worked great and got me a digital readout with obscenely expensive and hard to get 7 segment LED's.

These days ECL survives mainly as "LVDS" which can be interesting for clock.distribution especially or to "semi-isolate" signals.

All this means all logic inside the TDA1541 REALLY is very low noise.

The only weak points are the inputs because they are single ended input (though the circuit inside the TDA1541is actually differential) and can be overdriven by either excessively fast edges (sleeing the input stage and coupling noise into the IC substrate) from the source or by driving the input outside the linear range.

Technically, the point where we transition from differential, non saturation ECL to saturated single ended bipolar switches and diodes to switch the currents, but that is inherent to making a DAC with SE Outputs.

Had the DAC been made inherently differential it could have used non saturated emitter followers as bit switches and diodes without reverse bias recovery.

As said, all thinking coming from CMOS circuitry is not useful for TDA1541 and only causes one to pursue dead ends.

Most important IME are:

1) DEM synchronisation

1) Soft Inputs (edge speed limited and keeping inputs in the linear operation)

2) PSU loop control, very low PSU Impedance is IMNSO overrated for TDA1541, it is more important to make the current loop follow the correct path

3) DEM capacitor quality (once their leakage is low and the impedance at the DEM frequency and a few octaves up is sufficiently low)

Things like going differential or using simultaneous mode at low speeds give benefits mainly if the list above is not checked off.

Again, I'm no guru nor do I have the (w)holy truth, just my experience with TDA1541. I have not done any work with in the better part of a decade.

Thor

PS, In my earlier post I asked "the stored charge in the bit switches and associated diodes needs to go somewhere, what completes the AC current loop?"

The answer is, the DEM capacitors to output, via ground and the output to +5V.

It might be beneficial to connect the DEM capacitor common to +5V, never got around to trying that though.

Last edited:

What about this way to connect DEM capacitors output , and if not why 🤔

In this case you tie DEM Capacitors to AGND. This is what I have always done.

However, the AC loop the capacitors are closing does not strictly speaking close with AGND, does it?

Remember, current flows in loops and along the path of least resistance.

If on it's way to close the loop, the current encounters a material series impedance, it will cause a voltage to be dropped across that impedance. If the voltage dropped will be in series with anything that acts as reference for anything, we will have a problem.

So it is important to understand what the DEM capacitors actually do. What AC current is flowing and where does the loop start and finish, the loop that these capacitors complete.

Thor

Hi,

Something for fun. I did consider a DAC using TDA1541 to allow over 16 Bit before. . . . . . . . . . . .

Thor

VERY good to see Thorsten back online here at diyaudio.

Back in the 90's his sharing his designs and comments were very much appreciated by the diy:ers on different forums (as they are today)

Welcome back TL.

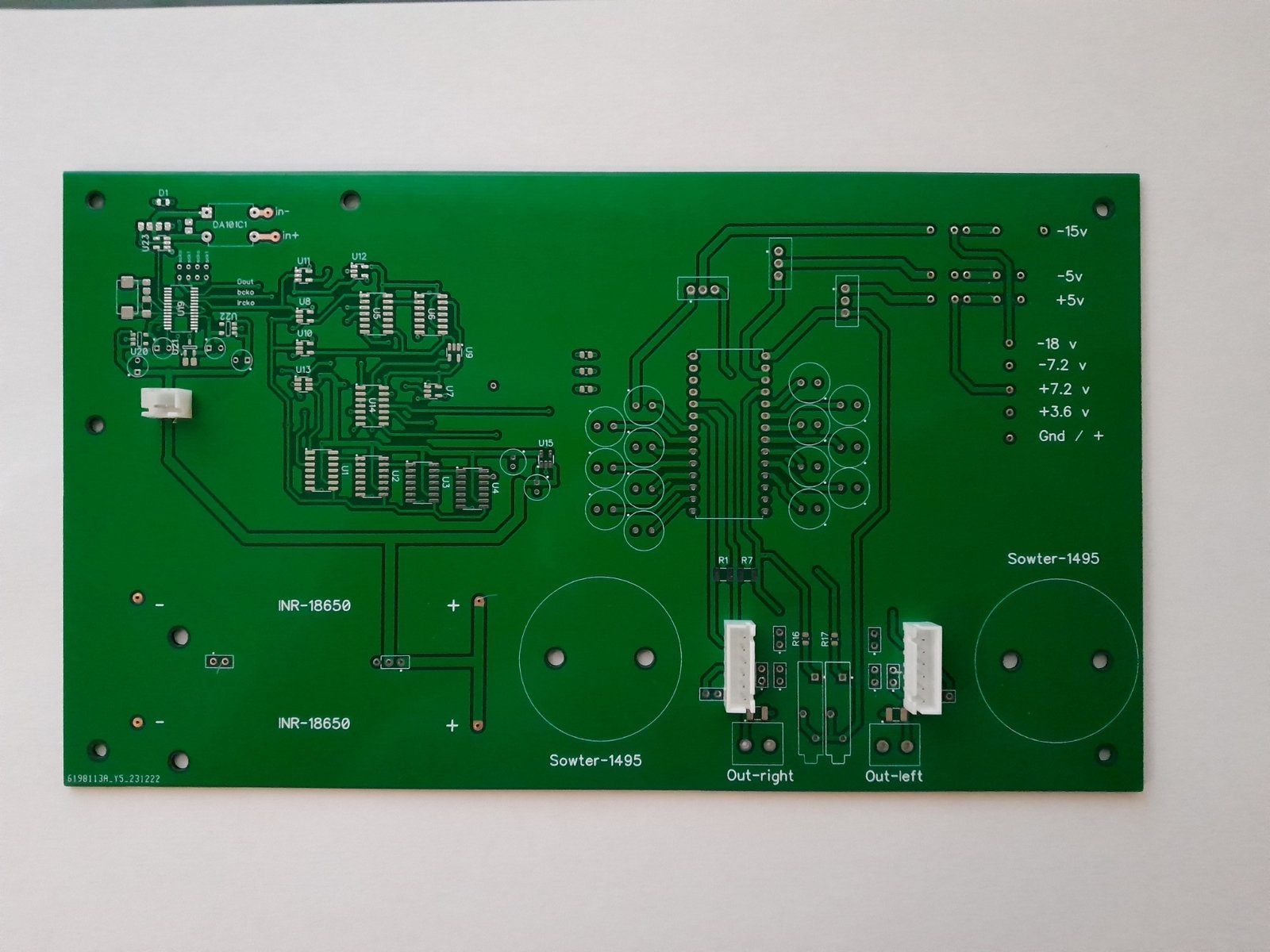

PCB arrived today , it is now time to check it all , desolder components from previous build and fill it 🙂

.

.

Hi Thorsten,Ryan,

...All this means all logic inside the TDA1541 REALLY is very low noise.

Thanks for another detailed response.

Points taken, did some further reading on ECL.

Thanks for taking the time to answer and give your experienced opinion.

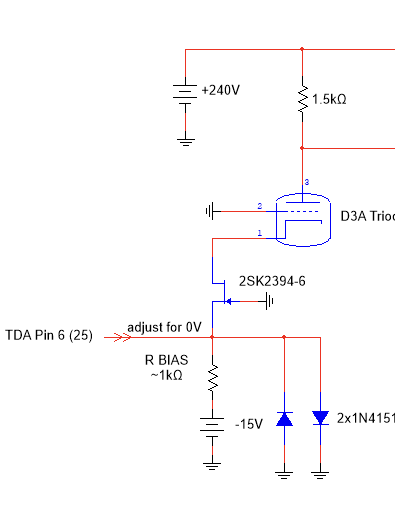

I was looking into impelmenting MVaudiolab's IV stage and I'm having a little trouble understanding the setup:

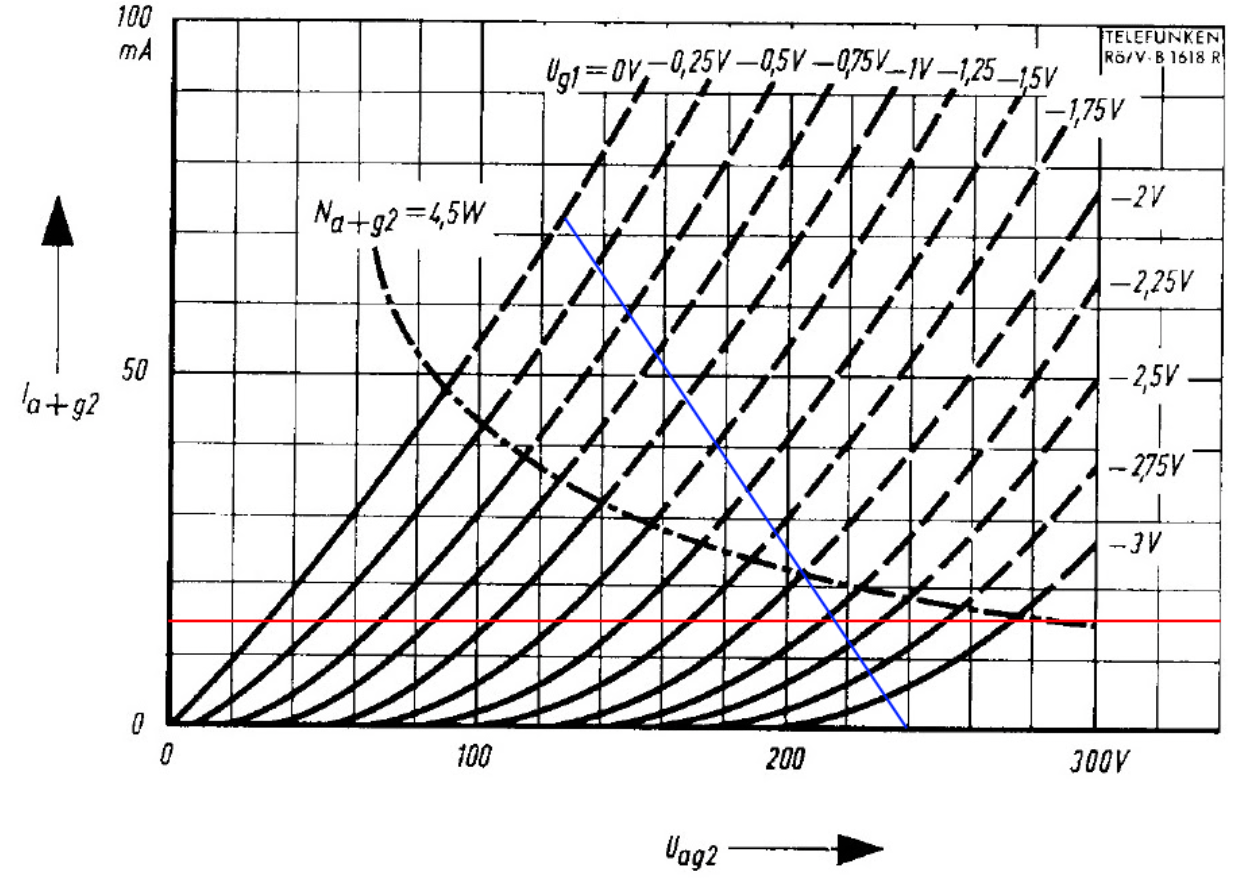

In his writeup he sets the current at 15mA (described elsewhere), resulting in the following approximate lines (I think)- the 1.5k is determined by the current buffering of the grounded-grid stage:

Is this the correct operating point? How is 2.25V at the d3a cathode enforced by the jfet?

In his writeup he sets the current at 15mA (described elsewhere), resulting in the following approximate lines (I think)- the 1.5k is determined by the current buffering of the grounded-grid stage:

Is this the correct operating point? How is 2.25V at the d3a cathode enforced by the jfet?

Last edited:

The D3a acts as cascode for the 2SK2394 J-Fet.

The J-fet is operated near Idss which, according to datasheet is 10 - 20mA, so use 15mA as "design center".

With 15mA flowing in the anode resistor (1.5k) it will drop around 22.5V, so the D3a sees 217.5V On the Anode.

The bias of the D3a at ~220V is around 2.6V. With the grid grounded, the Cathode will come to "rest" at ~2.6V.

Realistically, the D3a is a bit bogus here. The J-Fet is the main active device here, it operates in saturated (Pentode style) condition and not in the "triode region". With 40mA/V transconductance the effective input impedance is ~ 25 Ohm.

Using the D3a as actual common cathode amplifier and using a 20 Ohm I/U conversion resistor will probably work very nicely as well.

If using a tube for cascode, a less rare and expensive option or even a high voltage mosfet will likely do as well. When using a Mosfet as cascode, a +48V Supply voltage will be ok.

Even better, I prefer to use a very low noise BJT as Sziklai with a low noise P-Channel Mosfet (say MMBT4404 & BSS84), for a lot of stuff like I/U conversion. Make the output a folded cascode (P-Channel Mosfet), with 1.5k to ground as I/U conversion resistor.

THEN add the correct sallen key lowpass filter with the correct peaking for either SAA7220 or for non-oversampling using a tube that sounds nice as cathode follower. This way something glows and actually impacts the sound and low noise etc. is guaranteed.

Thor

The J-fet is operated near Idss which, according to datasheet is 10 - 20mA, so use 15mA as "design center".

With 15mA flowing in the anode resistor (1.5k) it will drop around 22.5V, so the D3a sees 217.5V On the Anode.

The bias of the D3a at ~220V is around 2.6V. With the grid grounded, the Cathode will come to "rest" at ~2.6V.

Realistically, the D3a is a bit bogus here. The J-Fet is the main active device here, it operates in saturated (Pentode style) condition and not in the "triode region". With 40mA/V transconductance the effective input impedance is ~ 25 Ohm.

Using the D3a as actual common cathode amplifier and using a 20 Ohm I/U conversion resistor will probably work very nicely as well.

If using a tube for cascode, a less rare and expensive option or even a high voltage mosfet will likely do as well. When using a Mosfet as cascode, a +48V Supply voltage will be ok.

Even better, I prefer to use a very low noise BJT as Sziklai with a low noise P-Channel Mosfet (say MMBT4404 & BSS84), for a lot of stuff like I/U conversion. Make the output a folded cascode (P-Channel Mosfet), with 1.5k to ground as I/U conversion resistor.

THEN add the correct sallen key lowpass filter with the correct peaking for either SAA7220 or for non-oversampling using a tube that sounds nice as cathode follower. This way something glows and actually impacts the sound and low noise etc. is guaranteed.

Thor

Thanks so much for explaining it Thorsten, that certainly wasn't as obvious as I thought. So in this case R_bias is just zeroing out whatever voltage the jfet settles at?

What you're describing seems consistent with some of his more subjective findings- specifically that the sound isn't impacted as much by the choice of tube in this configuration.

I was originally hoping to mimic this design with a c3g (because that's what I have on hand and they seemed like they could do similar work in that spot). Would transformer I/V make more sense if I wanted to pursue a grounded-grid design that "impacts the sound"?

Alternatively a c3g also sounds like it might work as a gain stage following a passive I/V like what you mentioned.

What you're describing seems consistent with some of his more subjective findings- specifically that the sound isn't impacted as much by the choice of tube in this configuration.

I was originally hoping to mimic this design with a c3g (because that's what I have on hand and they seemed like they could do similar work in that spot). Would transformer I/V make more sense if I wanted to pursue a grounded-grid design that "impacts the sound"?

Alternatively a c3g also sounds like it might work as a gain stage following a passive I/V like what you mentioned.

some Spice sims of the circuit (with generic "abstract" Power supply, that is critical because PSs will determinate the noise floor and mask achieved good harmonics resolution):

.

D3A working point is

-Ug=2V cca.

Va=(219.6V-2V)=217.6V

Ia=13.6mA cca. (including 2mA current inj. for TDA1541A)

RL=1.5K

.

Vo=5.87 Vp-p (2.07 Vrms)

THD=0.023% (only for that stage, probably with the rest of the circuit will not change a lot)

.

Phase is INVERTED for +180deg and that should be corrected. One way is to add interstage transformer after already present in the whole circuit, the low impedance buffer...

.

the potential from PS to Anode of D2A is just about +20V, so the most JFETs buffers in classic configuration can be used. Or even low voltage tubes as ECC86, some nuvistors, etc...

cheers

🙂

.

.

D3A working point is

-Ug=2V cca.

Va=(219.6V-2V)=217.6V

Ia=13.6mA cca. (including 2mA current inj. for TDA1541A)

RL=1.5K

.

Vo=5.87 Vp-p (2.07 Vrms)

THD=0.023% (only for that stage, probably with the rest of the circuit will not change a lot)

.

Phase is INVERTED for +180deg and that should be corrected. One way is to add interstage transformer after already present in the whole circuit, the low impedance buffer...

.

the potential from PS to Anode of D2A is just about +20V, so the most JFETs buffers in classic configuration can be used. Or even low voltage tubes as ECC86, some nuvistors, etc...

cheers

🙂

.

Attachments

If I recalled correctly Guido Tent once wrote an article about damping the I2S lines with resistor. Do wonder if it helps etc.Ryan,

I think you still do not understand how EC-Logic (ECL) works. And ECL is internal in the TDA1541, even the inputs are actually ECL, but single ended.

ECL is differential, a differential pair on a current source, the transistors normally do not enter saturation. It is in effect a high speed differential analogue circuit.

In the age of TTL and Low Power Schottky TTL with (respectively) 3MHz and 30MHz (appx.) maximum flip-flop clocks, ECL easily got to 300MHz which is impressive for the 1970's, heck, it's impressive today! Even more impressive is that the PSU current only has tiny amounts of what is in effect HD of a linear differential circuit.

I used ECL dual flip flop (Russian mil spec., incredibly hard to get) for the predivider in a frequency counter for a DIY FM Tuner (next divider Schottky TTL, then TTL and finally CMOS) appx. 1979. I tried digital frequency synthesis but could not get it to work without MCU, a simple counter worked great and got me a digital readout with obscenely expensive and hard to get 7 segment LED's.

These days ECL survives mainly as "LVDS" which can be interesting for clock.distribution especially or to "semi-isolate" signals.

All this means all logic inside the TDA1541 REALLY is very low noise.

The only weak points are the inputs because they are single ended input (though the circuit inside the TDA1541is actually differential) and can be overdriven by either excessively fast edges (sleeing the input stage and coupling noise into the IC substrate) from the source or by driving the input outside the linear range.

Technically, the point where we transition from differential, non saturation ECL to saturated single ended bipolar switches and diodes to switch the currents, but that is inherent to making a DAC with SE Outputs.

Had the DAC been made inherently differential it could have used non saturated emitter followers as bit switches and diodes without reverse bias recovery.

As said, all thinking coming from CMOS circuitry is not useful for TDA1541 and only causes one to pursue dead ends.

Most important IME are:

1) DEM synchronisation

1) Soft Inputs (edge speed limited and keeping inputs in the linear operation)

2) PSU loop control, very low PSU Impedance is IMNSO overrated for TDA1541, it is more important to make the current loop follow the correct path

3) DEM capacitor quality (once their leakage is low and the impedance at the DEM frequency and a few octaves up is sufficiently low)

Things like going differential or using simultaneous mode at low speeds give benefits mainly if the list above is not checked off.

Again, I'm no guru nor do I have the (w)holy truth, just my experience with TDA1541. I have not done any work with in the better part of a decade.

Thor

PS, In my earlier post I asked "the stored charge in the bit switches and associated diodes needs to go somewhere, what completes the AC current loop?"

The answer is, the DEM capacitors to output, via ground and the output to +5V.

It might be beneficial to connect the DEM capacitor common to +5V, never got around to trying that though.

Your Adiago dac was what got me interested in the TDA Thorsten, thank you kindly. First time a heard the Tda was on a Philips

cdp though resolution wasn't that good but wow the bass & that is was in my mind all the time.

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A