LOL, whatever you smoked I like to try as wellDear John has long ago attained the State of Grace so He is not bounded by earthlings' laws, rules, norms and statutes that are imposed (or self/imposed) on us...

I Love You All, Oh so much...

M.

Dear Doede,LOL, whatever you smoked I like to try as well

It is called Pure Unconditional Divine Love...

and it is Free, abundant everywhere and readily available in the Now in the Field of Unlimited Potential (V). Just breathe deeply, let go of all resistance (R) by exhaling slowly and accept the current (I) flow through your system/circuit until the Heart opens up as Big auto-sustained Toroideal Field and charges alike a Super-Capacitor...then radiate all energy that you won't use for the benefit of All that Is...you can imagine a Super-Nova or else...

and it is Free, abundant everywhere and readily available in the Now in the Field of Unlimited Potential (V). Just breathe deeply, let go of all resistance (R) by exhaling slowly and accept the current (I) flow through your system/circuit until the Heart opens up as Big auto-sustained Toroideal Field and charges alike a Super-Capacitor...then radiate all energy that you won't use for the benefit of All that Is...you can imagine a Super-Nova or else...Welcome,

M.

I can answer the question about the powerDAC-B model, based on information send by ECD: it is exactly the same design as the powerDAC-R, but without volume control (so fixed output) and without the integrated bit-perfect testing. In addition the external power supply is now build in but without any changes AFAIK.

Is this the place to talk about commercial products? I don't know, but I do think that it would be interesting to see more discussion somewhere of John's current solutions.

Is this the place to talk about commercial products? I don't know, but I do think that it would be interesting to see more discussion somewhere of John's current solutions.

Last edited:

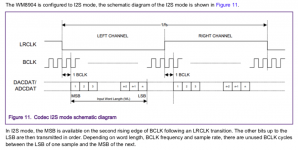

Now I am looking at the EC time I2S diagram and it seems that BCK is inverted from i2S standard? IN all cases of LE, going from 0 to 1 or 1 to 0, BCK is going falling edge. But in I2S standard whwn LE changing states BCK always going from 0 to 1, rising edge. Please check. At EC sch BCK going falling edge when LE changing states...Well, you might as well ask about his latest work because i feel pretty much momentum of thread is concluded, tda interest seems a bit died down, i think (but dont quote me on this) John mentioned he moved on to other things and got out of tda1541 what he wanted...now he just anwsers questions here and there out of generosity and good nature it seems. And questions bump the thread up anyway so it has its positive aspect..

Report from me: I have in front of me currently latest (v3) redesign of signed magnitude PCB, xaled's version of just i2s to signed magnitude logic, and testing this with my JLsounds and xaled's Amanero, together with logic analyzer (i still have to return this stuff to him!). Sadly, though i have implemented about a dozen different dacs at this point, this one is a horse that refuses to be broken. Yes regular i2s and simultaneous work, and yes you can use two tda's and double the currents and all that, but that isn't breaking new ground.

Currently in life i am also very busy and in times of change, so i kind of doubt there will be a v4 if i dont get this to work in a few days. Embarassingly, easily well over 100hrs into this project just reading, researching, designing, revisioning...and that is with all the "blueprints" basically already provided by John...

I plan to send out board to some standing and/or interested thread participants upon request, to mess around with it themselves if they want to, as it should be all correct in theory...

Anyway, more from me later.

P.S i am zbunjen from this thread, just forum name change

Hmm...interesting.. i see what you mean if we're both looking at 7092Now I am looking at the EC time I2S diagram and it seems that BCK is inverted from i2S standard? IN all cases of LE, going from 0 to 1 or 1 to 0, BCK is going falling edge. But in I2S standard whwn LE changing states BCK always going from 0 to 1, rising edge. Please check. At EC sch BCK going falling edge when LE changing states...

Definitely will try to play with BCK and U4

Thank you for alerting me Zoran

I have enjoyed following his work and have no issue with this simply being about what he is designing and commercializing today. I do a double take when I see some members get run out of town for agreeing to sell their stuff and others no worries. All good.Since this is his thread and most people are interested in how his quest is going... why spoil the fun?

HiHmm...interesting.. i see what you mean if we're both looking at 7092

Definitely will try to play with BCK and U4

Thank you for alerting me Zoran

I must correct myself. Double check is always good...

I2S bus presented in the 7092 is correct.

But

it should be verified by measuring I2S coming from receiver spdif-I2S board OR USB-I2S interface.

Also when measuring signals not bad idea is to take a look at master clock MCK line and how it is related with SCK line

in some interfaces I measured is in phase (booth rising edge starts) with SCK like Amanero, but in some XMOS based interfaces it is opposite to SCK

This is good link

https://ez.analog.com/audio/f/q-a/544131/how-to-take-meaningful-screenshots-of-i2s-audio-signals

cheers

Attachments

Hello Zoran,

Thank you for bringing these things to my attention to try.

These days i am very busy, so i barely even have to time to think properly.

So cheers for that 🍻

Edit: When i test, i use Amanero (original, not Ali), and I2SoverUSB which is xmos based but has configurable betweel I2S, left justified, right justified, and some other I2S variations like for ESS dacs.

Thank you for bringing these things to my attention to try.

These days i am very busy, so i barely even have to time to think properly.

So cheers for that 🍻

Edit: When i test, i use Amanero (original, not Ali), and I2SoverUSB which is xmos based but has configurable betweel I2S, left justified, right justified, and some other I2S variations like for ESS dacs.

Hi Zoran,

If I recall correctly, this circuit (post #7092) was designed for simultaneous output (L and R data time aligned) in order to feed both, left and right data into the TDA1541A simultaneously:

DATA L

DATA R

LATCH (WS)

CLK

When you check TDA1541A data sheet & timing diagrams for simultaneous mode (pin 27 connected to -5V), you will see that data is now being latched at the falling edge of BCK.

In I2S mode (pin 27 connected to +5V) data is latched at the rising edge of BCK.

If I recall correctly, this circuit (post #7092) was designed for simultaneous output (L and R data time aligned) in order to feed both, left and right data into the TDA1541A simultaneously:

DATA L

DATA R

LATCH (WS)

CLK

When you check TDA1541A data sheet & timing diagrams for simultaneous mode (pin 27 connected to -5V), you will see that data is now being latched at the falling edge of BCK.

In I2S mode (pin 27 connected to +5V) data is latched at the rising edge of BCK.

Can you post circuit that is suitable for TDA1541A or post a link to a page where it can be viewed?In the active way you could use a choke loaded grounded grid tube I/V stage (DAC output into the cathode circuit).

Thanks,

Can you post circuit that is suitable for TDA1541A or post a link to a page where it can be viewed?

Andrea can't post anything because has been banned on this forum for an unknown reason to me.

Hi ECHi Zoran,

If I recall correctly, this circuit (post #7092) was designed for simultaneous output (L and R data time aligned) in order to feed both, left and right data into the TDA1541A simultaneously:

DATA L

DATA R

LATCH (WS)

CLK

When you check TDA1541A data sheet & timing diagrams for simultaneous mode (pin 27 connected to -5V), you will see that data is now being latched at the falling edge of BCK.

In I2S mode (pin 27 connected to +5V) data is latched at the rising edge of BCK.

If I get right from the I2S standard:

a) SCL is always fallen edge when LE change state.

b) MSB is 1SCK after the LE change state

c) MSB is fallen edge SCK?

.

For time sim :

a) no matter the data value bit starts at rising edge of BCK

b) LE is independent, common for L and R ch, and can trigger the conversion 0sec after LSB loaded or latter. With rising edge. Enough pulse of LE is 1/2 of BCK...

.

From SAAs chip we can see that the data are at the rising edge of SCK too.

.

Last edited:

Folks, almost exactly 10 years ago I had built a dac based on tda1541a using many of john’s tricks. Due to life (kids, international moves) my system was in hibernation for a decade. When I fired her up now, I have horrible distortion in the output. There is no music audible.

Signal comes from a squeezebox built into the dac, which is slaved to a clock on the dac board (bck). WS and DATA(l) come from the squeezebox. I have not changed anything since it last worked, however something may have happened during transport/heat.

Reducing volume digitally on the squeezebox makes the distortion slightly less but any music is still almost indistinguishable against the distortion. On the scope the output signal looks oddly shaped. BCK, WS and DATA look ok on the scope, but I don’t have a logic analyzer. I see no obvious shorts or solder joint issues.

Prime suspects are the i2s attenuators and the dem setup:

1) attenuators - i2s signals seem to easily comply with the 200mVpp treshold, if not the data sheet treshold of 0.8-2.0V. I measured approx 0.7-1.9v.

2) DEM - I dont recall exactly what my DEM frequency is (I think at the very low end, eg 50khz). However, my recollection is that incorrect DEM would create some distortion but not complete and utter noise like I have now. Can somebody confirm pls?

My scope has died yesterday so I’m a bit blind at the moment…. Looking for pointers…(it’s not the tda1541a itself, I’ve swapped for another one in my stash)

Signal comes from a squeezebox built into the dac, which is slaved to a clock on the dac board (bck). WS and DATA(l) come from the squeezebox. I have not changed anything since it last worked, however something may have happened during transport/heat.

Reducing volume digitally on the squeezebox makes the distortion slightly less but any music is still almost indistinguishable against the distortion. On the scope the output signal looks oddly shaped. BCK, WS and DATA look ok on the scope, but I don’t have a logic analyzer. I see no obvious shorts or solder joint issues.

Prime suspects are the i2s attenuators and the dem setup:

1) attenuators - i2s signals seem to easily comply with the 200mVpp treshold, if not the data sheet treshold of 0.8-2.0V. I measured approx 0.7-1.9v.

2) DEM - I dont recall exactly what my DEM frequency is (I think at the very low end, eg 50khz). However, my recollection is that incorrect DEM would create some distortion but not complete and utter noise like I have now. Can somebody confirm pls?

My scope has died yesterday so I’m a bit blind at the moment…. Looking for pointers…(it’s not the tda1541a itself, I’ve swapped for another one in my stash)

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A

....There's a starmaaaaaaaan waiting in the sky....

....There's a starmaaaaaaaan waiting in the sky....