Mr. MR , have you SJDP model , too ?

and , just now , I'm having an idea of trying it with cascoded LU ...... it would allow full blast (meaning regular FW range of PSU voltage ) version of amp

will sim tonight ....... and just dream when I'll have time to try it in vivo

Sorry, ZM. I don't have that one.

Sorry, ZM. I don't have that one.

Silly ZM ...... I have it in my LTSpice , imported in JFet library eons ago

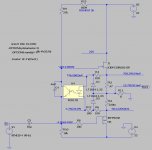

so , here it is , with SJDP

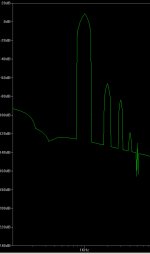

it needs speaker delay relay , having startup peak , about 10V in first 50uS

at least according to sim .... worth checking in vivo , with soft start etc.

Attachments

.subckt SJDP120R085 D G S ; 1200V 100mohm TO-247

Rd D Di 35m tc=9m, 5u ; requires tempco

Rs S Si 35m tc=9m, 5u ; requires tempco

Rg G Gi 500m tc=-3m ; requires negative tempco

Cds S Di 1p ; direct Cds is almost zero

Cgd G Di 2.5p ; Cgd overlap capacitance

Ji Di Gi Si SJDP120R085

.ends SJDP120R085

.model SJDP120R085 njf; Rd, Rs not used (no tempco)

+ Vto=-5 Beta=8 B=0.2 ; dc curves

+ Lambda=.31314 Vk=2k5 Alpha=20u ; voltage influence

+ Is=1e-020 N=3.5 ; sets fwd GS diode curves

+ Isr=1e-020 Nr=1.5 ; sets rev leakage

+ Cgd=500p Cgs=200p Pb=1.6 M=1 ; nonlinear Cs

+ Kf=1f Af=1 ; flicker noise

+ VtoTC=-2m BetaTCe=-0.25 Xti=35 ; tempcos

.ends SJDP120R085

Rd D Di 35m tc=9m, 5u ; requires tempco

Rs S Si 35m tc=9m, 5u ; requires tempco

Rg G Gi 500m tc=-3m ; requires negative tempco

Cds S Di 1p ; direct Cds is almost zero

Cgd G Di 2.5p ; Cgd overlap capacitance

Ji Di Gi Si SJDP120R085

.ends SJDP120R085

.model SJDP120R085 njf; Rd, Rs not used (no tempco)

+ Vto=-5 Beta=8 B=0.2 ; dc curves

+ Lambda=.31314 Vk=2k5 Alpha=20u ; voltage influence

+ Is=1e-020 N=3.5 ; sets fwd GS diode curves

+ Isr=1e-020 Nr=1.5 ; sets rev leakage

+ Cgd=500p Cgs=200p Pb=1.6 M=1 ; nonlinear Cs

+ Kf=1f Af=1 ; flicker noise

+ VtoTC=-2m BetaTCe=-0.25 Xti=35 ; tempcos

.ends SJDP120R085

Can the Lundahl LL1517 trafo be used here or in B1 with gain?

http://www.lundahl.se/wp-content/uploads/datasheets/1517.pdf

http://www.lundahl.se/wp-content/uploads/datasheets/1517.pdf

ZM > anyway , M2 and DEFiSIT - close cousins ..

Similar and different beacause Pass SIT-1 and Cinemag etc.

M2 without input and output capacitors.

Curious about Your first music play with DEFiSIT

M2 has loading on trafo secondary, DEFiSIT has not....due to different trafos?

Silly ZM ...... I have it in my LTSpice , imported in JFet library eons ago

so , here it is , with SJDP

it needs speaker delay relay , having startup peak , about 10V in first 50uS

at least according to sim .... worth checking in vivo , with soft start etc.

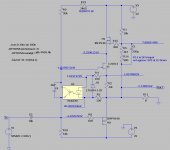

latest iteration of LuDEF sim , much closer to pure DEFiSIT ideal ..... no source degeneration for IRFP9240 , while entire combo consisted of LU. it's source resistor and IRFP240 cascode should be considered as poor man's SIT substitution

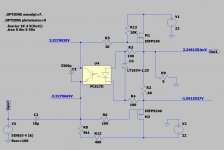

hey , it gnawed just right on me ...... one can try even poorer man's SIT Substitution (as fast & furious taste of Real McKay) ..... using verbatim M2 circuit , but connecting upper mosfet with Shade thingie (1K+10K) ........ will try that sim pronto

mild and slow thump (under 400mV) during startup , most probably even lowered due to action of (commonly used in Papamps) NTC softstart

Attachments

Last edited:

this one is sooooooooo nutz ........ it can be called M2 SEF (M2 Shade Enhanced Follower)

mild negative 450mV thump during startup

I like

O. H. Schade was a German and that's the only (and totally unimportant) fact that connects the subject to Germany, so no need to accentuate the "German" part so loud. Even I'm not a German, it's just the place where I live at the moment.

What really matters is this:

http://www.clarisonus.com/Archives/TubeTheory/Schade 1938 Beam Power Tubes.pdf

What really matters is this:

http://www.clarisonus.com/Archives/TubeTheory/Schade 1938 Beam Power Tubes.pdf

There is no AC signal on the drain of the MOSFET (the drain is grounded AC wise through the PSU) so there can be no feedback that way (nothing to feed back, just a static DC bias conditiion).

The last paragraph on that page speaks only about cathode degeneration as the form of feedback that lowers the distortion and it's irrelevant from the "turn penthode into triode" point of view.

The last paragraph on that page speaks only about cathode degeneration as the form of feedback that lowers the distortion and it's irrelevant from the "turn penthode into triode" point of view.

- Home

- Amplifiers

- Pass Labs

- Most Greedy Boy, of them all... or (there is no) DEFiSIT of Papa's Koans