Problem solved but questions remain. After replacing the I2C isolator on a rig with a 9028, I do indeed have restored access to DAC registers. What confuses me is that I2C only works reliably when a Trident is in place on the VDD_XO during power-up. Apparently, the management chip that holds the reset pin low on startup doesn't successfully activate I2C *without* the XO trident in place. Perhaps a longer 'low-hold' on power up is called-for...

Sounds like the DAC doesn't have a functioning clock in time, I think you are correct to wait longer for the clock to be present.

Sounds like the DAC doesn't have a functioning clock in time, I think you are correct to wait longer for the clock to be present.

Yes, thanks, that was the problem. Instead of using a boot management IC I switched to an isolated GPIO pin, whose timing is easily programmed.

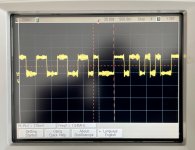

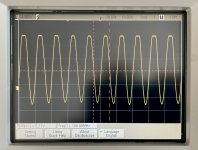

My original design was to be able to use the 100MHz onboard clock with SPDIF, versus an external MCLK with I2S. I'm not succeeding in getting the old 9018s configured via I2C to work with the consumer level SPDIF from the TPA Toslink board. Toslink signal integrity doesn't seem bad (though only 375 mv p-p when connected to the B3, concern?), clock oscillations look good, and I2S is confirmed shut off. Is there still any online info concerning the 9018 register settings from the old B3 stock EPROM?

Many TIA,

Frank

Attachments

Last edited:

2 ways...

You can run it two ways:

1. with the Trident in place for VDD XO, and no u.fl cable for the master clock from the Cronus. This uses the ESS chip in asynchronous mode, and resamples all data asynchronously.

2. Without the Trident in place for VDD XO, and with the u.fl cable in place from the Cronus for the masterclock. This runs the ESS chip in the synchronous mode and resamples data synchronously. My opinion is that synchronous mode sounds better, but of course you can try both methods and decide for yourself what you prefer.

Hello All,

With amanero in slave mode, does VDD_XO need to be omitted and EXT_MCK from Buffalo III SE Pro

connected to U_MCK in Cronus Reclocker (with Rhea modules installed)?

You can run it two ways:

1. with the Trident in place for VDD XO, and no u.fl cable for the master clock from the Cronus. This uses the ESS chip in asynchronous mode, and resamples all data asynchronously.

2. Without the Trident in place for VDD XO, and with the u.fl cable in place from the Cronus for the masterclock. This runs the ESS chip in the synchronous mode and resamples data synchronously. My opinion is that synchronous mode sounds better, but of course you can try both methods and decide for yourself what you prefer.

yes

Yes, I do so all the time. Basically, the DPLL will just "freewheel" as the master clock and bit clock will be synchronous, so the result will be no asynchronous re-sampling. The only drawback is that the ESS chip will no longer "reduce" jitter, but with the Cronus/Amanero this should not be a concern, as this is a very low jitter source.

Yes, I do so all the time. Basically, the DPLL will just "freewheel" as the master clock and bit clock will be synchronous, so the result will be no asynchronous re-sampling. The only drawback is that the ESS chip will no longer "reduce" jitter, but with the Cronus/Amanero this should not be a concern, as this is a very low jitter source.

You can run it two ways:

1. with the Trident in place for VDD XO, and no u.fl cable for the master clock from the Cronus. This uses the ESS chip in asynchronous mode, and resamples all data asynchronously.

2. Without the Trident in place for VDD XO, and with the u.fl cable in place from the Cronus for the masterclock. This runs the ESS chip in the synchronous mode and resamples data synchronously. My opinion is that synchronous mode sounds better, but of course you can try both methods and decide for yourself what you prefer.

Barrows, thank you. It works in both ways.

The reason why I ask is sporadic static-like noise I have in both modes, sync & async with DSD.

With PCM 352800 Hz in sync mode no sound at all. In async mode there is a lot of noise instead of sound.

All other sample rates are good.

Not sure why... maybe I have to get rid of u.fl cables?

My original design was to be able to use the 100MHz onboard clock with SPDIF, versus an external MCLK with I2S. I'm not succeeding in getting the old 9018s configured via I2C to work with the consumer level SPDIF from the TPA Toslink board. Toslink signal integrity doesn't seem bad (though only 375 mv p-p when connected to the B3, concern?), clock oscillations look good, and I2S is confirmed shut off.

Just a followup to say that there was no problem with those Toslink outputs. With a bit of background info from Brian I got everything sorted out. Again, performance of the es9018+Mercury I/V is quite pleasing (we're building with 9018s, a 9028, and a 9038 for family). Also pleasing is the casework done mostly by my son... Aluminum bases & back, 1/4" brass fronts and DIY knobs, granite/acrylic laminated sides, acrylic tops laser-cut for ventilation.

Full disclosure: "Largo" is a family joke meaning "from the minds of imposters".

Attachments

Barrows, thank you. It works in both ways.

The reason why I ask is sporadic static-like noise I have in both modes, sync & async with DSD.

With PCM 352800 Hz in sync mode no sound at all. In async mode there is a lot of noise instead of sound.

All other sample rates are good.

Not sure why... maybe I have to get rid of u.fl cables?

I have no such problems, using u.fl cables at 10 cm or less. 352.8 may require a higher clock speed? It has been awhile before I have tested that. Mine works perfectly for DSD up to DSD 256 with a 45.1584 clock on the Cronus, DSD 512 would require a 90.3168 clock. I will test with PCM 352.8 and let you know for sure (DSD input sounds so much better to me I oversample everything to DSD 256 for playback). I am using amanero firmware 2006be 11 and CPLD 1081 slave for best performance with DSD (will work for native DSD on linux in my case).

I have no such problems

Thank you!

It seems like an amanero module has a problem. I have tried different firmware with same result.

I am in the process is trying a variety of power supplies but have found noticeable improvement with an LT3045 (6x in parallel) powering the DAC. Bass is better and more defined and the background might allow a few more details through.

I am ordering more to try powering the AVCC lines separately as well as the cronus. I'm not sure whether there will be any improvement on the AVCC lines as they're analog, but we will see.

So far, to my ears, the BuffPro9028 with Legato sounds the best. The 9038 with mercury remains somewhat bright, but I do wonder if different power supplies might benefit that combination as well.

I am ordering more to try powering the AVCC lines separately as well as the cronus. I'm not sure whether there will be any improvement on the AVCC lines as they're analog, but we will see.

So far, to my ears, the BuffPro9028 with Legato sounds the best. The 9038 with mercury remains somewhat bright, but I do wonder if different power supplies might benefit that combination as well.

This is an interesting approach and I will be curious about your final configuration and conclusions. I have a few questions.

1. How did you parallel the chips? A purpose-made circuit board, or other surface mount arrangement?

2. Did your circuit include a guard zone for the SET pin (#7)? If so, which board layers?

3. Whoa, 6 chips? That's up to 3 amps, so were they feeding other circuits than just the B3?

I tried a more conservative application of one LT3045 on my most recent project. It supplied the VDD_XO through a relay so that I could remotely switch between synch and asynch DAC operation. At first I set it at 3.3v and used a small passive filter at the B3's VDD_XO input. Not so successful - probably too much wire between the regulator and the B3. I then raised the LT3045 output to about 4.5v and sent that into the VDD_XO trident. In this configuration the SPDIF sources that use the 100MHz onboad clock are sounding very nice. But those are fairly jittery sources so I wouldn't over-sell the experiment and assume that all sources - especially synchronous ones - would benefit as well.

If I'm not mistaken, the LT3045 in an optimal layout should offer about half of the noise of a Trident. I don't have any idea about the PSRR of Trident output. But I would think that with adequate capacitance and enough 3045s for current overhead, the LT3045 could improve the B3Pro performance. But as pages 14 and 15 of the analog devices datasheet suggest, the devil would be in the details.

Please keep us informed if you try the LT3045 for AVCC!

Cheers,

Frank

1. How did you parallel the chips? A purpose-made circuit board, or other surface mount arrangement?

2. Did your circuit include a guard zone for the SET pin (#7)? If so, which board layers?

3. Whoa, 6 chips? That's up to 3 amps, so were they feeding other circuits than just the B3?

I tried a more conservative application of one LT3045 on my most recent project. It supplied the VDD_XO through a relay so that I could remotely switch between synch and asynch DAC operation. At first I set it at 3.3v and used a small passive filter at the B3's VDD_XO input. Not so successful - probably too much wire between the regulator and the B3. I then raised the LT3045 output to about 4.5v and sent that into the VDD_XO trident. In this configuration the SPDIF sources that use the 100MHz onboad clock are sounding very nice. But those are fairly jittery sources so I wouldn't over-sell the experiment and assume that all sources - especially synchronous ones - would benefit as well.

If I'm not mistaken, the LT3045 in an optimal layout should offer about half of the noise of a Trident. I don't have any idea about the PSRR of Trident output. But I would think that with adequate capacitance and enough 3045s for current overhead, the LT3045 could improve the B3Pro performance. But as pages 14 and 15 of the analog devices datasheet suggest, the devil would be in the details.

Please keep us informed if you try the LT3045 for AVCC!

Cheers,

Frank

Hi all,

we would like to try the Buffalo III-se with our new FIFO Lite and our SOTA oscillators.

Is there a way to get the Sabre DAC working in pure sync mode (PLL stopped) with the Buffalo?

If so, what items have I to get (including power supply)?

Good morning,

Yes, you can fully control all of the configuration registers of the ESS DACs on the Buffalo III. While the onboard firmware is efficient and effective, you may bypass that and use the I2C connection to more completely control the chip. In this case you need a clean 3.3 volt TTL source to control DAC reset. A description of the registers is here. When supplying an external master clock you can simply remove power to the onboard oscillator. In that case, it is my understanding that the DPLL is without digital effect, whether running or not. However, it can be disabled by setting bit 4 of register 10 for 128fs_mode. I run this way in my highest-resolving system and the sound is 'very slightly' different from leaving the DPLL running - not necessarily better.

Twisted Pear offers everything you need to successfully implement the Buffalo - 5v power, Trident & AVCC local voltage regulators, and a choice of current->voltage converters, all of which double as very capable drivers to headphones. The 9038Pro requires the Mercury I/V, while the 9028Pro can use any of the I/V choices. If you are interested in innovating toward the very highest performance, the Buffalo offers many possibilities with respect to power and I/V.

Very best regards in pursuit of "SOTA"!

Frank

Good morning,

Yes, you can fully control all of the configuration registers of the ESS DACs on the Buffalo III. While the onboard firmware is efficient and effective, you may bypass that and use the I2C connection to more completely control the chip. In this case you need a clean 3.3 volt TTL source to control DAC reset. A description of the registers is here. When supplying an external master clock you can simply remove power to the onboard oscillator. In that case, it is my understanding that the DPLL is without digital effect, whether running or not. However, it can be disabled by setting bit 4 of register 10 for 128fs_mode. I run this way in my highest-resolving system and the sound is 'very slightly' different from leaving the DPLL running - not necessarily better.

Twisted Pear offers everything you need to successfully implement the Buffalo - 5v power, Trident & AVCC local voltage regulators, and a choice of current->voltage converters, all of which double as very capable drivers to headphones. The 9038Pro requires the Mercury I/V, while the 9028Pro can use any of the I/V choices. If you are interested in innovating toward the very highest performance, the Buffalo offers many possibilities with respect to power and I/V.

Very best regards in pursuit of "SOTA"!

Frank

Hi Frank,

thanks for the reply.

So isn't possible to disable the DPLL in hardware by using one of the provided jumpers?

I'm asking this because I'm looking for a definitive solution to disable the DPLL. I wouldn't repeat the reset every startup.

I don't need the I to V converter, so I should get:

- Buffalo-IIIsePro38 2-Channel DAC w/Full Series Regulator Set

- Placid HD 2.1 Power Supply Kit

- 9V+9V (30VA) Power Transformer

Is it right?

Andrea

- Home

- More Vendors...

- Twisted Pear

- Introducing the Buffalo III-SE-Pro 9028/9038