For now I'm trying to determine what is going on with FA2, and indeed all the other power amps ive tried simulating recently. I've a vested interest in FA2 because a) it's pretty similar to a design I had in mind anyway and b) I've done a PCB layout for it to fit my needs

I'm coming to the conclusion that LTSpiceIV is broken somehow. There has been some major changes in this version in order to support threaded use (IE, for multi-core CPUs), and I just don't think it works right. Take a look at this for example:

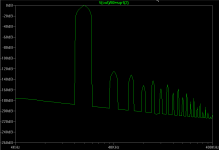

That is a transient analysis of the FA2 file you sent me. The .tran params are 10m with a max timestep of 0.01u, and the input source voltage set to zero. The circuit is biased for approx 32mA in each output.

That line should be dead flat - instead, there are these random spikes, and it takes LTSpiceIV *ages* to run even the short 54us pictured. If I reduce the timestep to 0.5u I get this:

I'm going to post this on the LTSpice newsgroup. I'm damn sure the original LTSpiceIII didn't do this. Unfortunately I have no way to check as I can no longer get LTSpiceIII!

I'm coming to the conclusion that LTSpiceIV is broken somehow. There has been some major changes in this version in order to support threaded use (IE, for multi-core CPUs), and I just don't think it works right. Take a look at this for example:

An externally hosted image should be here but it was not working when we last tested it.

That is a transient analysis of the FA2 file you sent me. The .tran params are 10m with a max timestep of 0.01u, and the input source voltage set to zero. The circuit is biased for approx 32mA in each output.

That line should be dead flat - instead, there are these random spikes, and it takes LTSpiceIV *ages* to run even the short 54us pictured. If I reduce the timestep to 0.5u I get this:

An externally hosted image should be here but it was not working when we last tested it.

I'm going to post this on the LTSpice newsgroup. I'm damn sure the original LTSpiceIII didn't do this. Unfortunately I have no way to check as I can no longer get LTSpiceIII!

and it takes LTSpiceIV *ages* to run even the short 54us pictured

That is the same thing I got

ran the same sim on Orcad Pspice and had different results.

When you replace 1381's with mpsaXX's, BDxx's, or 340/50's

errata dissappears .. so you tell me..??

Andy c. had me do the tran test and it did not look like that

what proccessor do you have.. could be errata on certain

processors..AMD bug, Intel P3 bug,..etc

OS

I think LT is optimized for C2d or AMD 64 CPU's ,on my sons

P4 it "crashes"..(exhibits your symptoms)

there is a

thread adjustment in "control panel"/spice.. try setting 10+ threads and in "compression" try reducing values. (this

helped on the P4).

also try reinstalling it..

OS

P4 it "crashes"..(exhibits your symptoms)

there is a

thread adjustment in "control panel"/spice.. try setting 10+ threads and in "compression" try reducing values. (this

helped on the P4).

also try reinstalling it..

OS

ostripper said:and in "compression" try reducing values.

OS

No compression!

I set plotwinsize=0 to disable compression. Also, I'm using a Core2Duo (E8400) with 2G of ram.

I did a clean install to verify it was not a problem with having automatically updated from LTSpiceIII.

If anyone here has an older version theyd be willing to zip up and send to me, I'd be very grateful. Just the executables will do - I won't need the examples or lib folder.

The way I have used to test THD before is to write a .tran statement with a short period (10m), and a very small timestep (0.001u usually). I then do .four <freq> I(load). I ensure the circuit is set up and biased prior to this.

I did a clean install to verify it was not a problem with having automatically updated from LTSpiceIII.

If anyone here has an older version theyd be willing to zip up and send to me, I'd be very grateful. Just the executables will do - I won't need the examples or lib folder.

The way I have used to test THD before is to write a .tran statement with a short period (10m), and a very small timestep (0.001u usually). I then do .four <freq> I(load). I ensure the circuit is set up and biased prior to this.

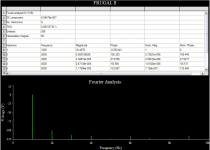

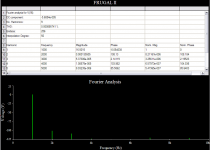

Now that I learned real good, I will show some FFT's..

(that is 1K/1W- FA2/3 .001% H2 -90db.. H3 .0005% -93db)

and hard clipping..

at 150W

at 150W

FA2 showed much worse distortion than 3 in this FFT.

OS

An externally hosted image should be here but it was not working when we last tested it.

(that is 1K/1W- FA2/3 .001% H2 -90db.. H3 .0005% -93db)

and hard clipping..

An externally hosted image should be here but it was not working when we last tested it.

FA2 showed much worse distortion than 3 in this FFT.

OS

OS, you should be able to get the residual junk of the FFT about 180 dB below the main signal. I'm not sure how you're doing your FFT, but one must not start the FFT at the beginning of a simulation. It's important to let any transients settle out before beginning the FFT. This means taking the FFT over an integer number of cycles starting near the end of the sim and going to the end.

got rid of "herringbone"HF

You mean "grab" the last .1m from the plot and .four that??

(how would you do that??) BTW , a cascode topology

change got rid of a lot of that "herringbone' plot at HF..

[see above]

Now I can see fully how all the compensations affect the

plot and the harmonics.

-180 is indeed impressive, I haven't even seen that on

curls thread. how would you do that??

OS

An externally hosted image should be here but it was not working when we last tested it.

You mean "grab" the last .1m from the plot and .four that??

(how would you do that??) BTW , a cascode topology

change got rid of a lot of that "herringbone' plot at HF..

[see above]

Now I can see fully how all the compensations affect the

plot and the harmonics.

BY andy C - you should be able to get the residual junk of the FFT about 180 dB below the main signal

-180 is indeed impressive, I haven't even seen that on

curls thread. how would you do that??

OS

When I did at simulation of 100ms and sampled the last 10ms

of it, the results were horrible but when doing a fourier of

only 10ms everything was acceptable....strange.

Jaycee was having this problem too..

To compare I used a blameless design (known to give -90db H2)

as a reference with standard models (bd139/140)....same results..

perhaps I will try LT 3 as well.

of it, the results were horrible but when doing a fourier of

only 10ms everything was acceptable....strange.

Jaycee was having this problem too..

To compare I used a blameless design (known to give -90db H2)

as a reference with standard models (bd139/140)....same results..

perhaps I will try LT 3 as well.

What i've been doing is doing a very detailed .tran, 10ms with 0.01u step time, operating point resolved first. What i've also tried is doing 12ms and starting capture at 2ms, but i still get a poor THD reading and large 2nd and 3rd harmonics.

However, I've simmed some headphone amps I designed on LTSpice ages ago, and they read nice and low. Call me confused!!

For example:

However, I've simmed some headphone amps I designed on LTSpice ages ago, and they read nice and low. Call me confused!!

For example:

An externally hosted image should be here but it was not working when we last tested it.

An externally hosted image should be here but it was not working when we last tested it.

I can sim it, but I get lousy THD results no matter what I do, which I know isnt right.

I must be doing something wrong, or have bad models.. but they are all from Fairchild or OnSemi, so they should be right.

edit: Here's a schematic I've been tinkering with. It's not FA2 exactly, but it's very similar. I can only get 0.01% THD out of this at full power at 1KHz (no it isnt clipping) no matter what I do. It's biased for 40mA per pair but changing that doesn't do much. I've also included the models I'm using.

www.darkmatter.myby.co.uk/FA2.rar

I must be doing something wrong, or have bad models.. but they are all from Fairchild or OnSemi, so they should be right.

edit: Here's a schematic I've been tinkering with. It's not FA2 exactly, but it's very similar. I can only get 0.01% THD out of this at full power at 1KHz (no it isnt clipping) no matter what I do. It's biased for 40mA per pair but changing that doesn't do much. I've also included the models I'm using.

www.darkmatter.myby.co.uk/FA2.rar

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Solid State

- The Frugalamp by OS