I can only use what I have, or can build simply.

This was my attempt.

It gave a Ciss of ~20pF, which is obviously too low.

Can you spot anything wrong ?

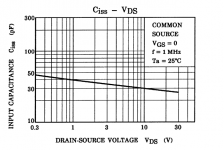

It's OK from my reading of the datasheet and you are saying 20pF at -2V bias. The first graph on the second last page of the original Toshiba datasheet shows 30pF at 9V Vds and Vgs = 0. The second graph shows a drop of about 10pF with -2V bias, which would give 20pF or so. It's a pain to de-embed Cgs and Cgd from the industry standard definitions of Ciss and Crss, SPICE uses Cgs and Cgd which as you can see are on a straight line when plotted log/log vs. V so it is a simple power law the slope can be read off of the graphs.

We have a lab station set up right near my cube to measure the photodiodes we are making, I could do a NOS SK170 next Friday when I'm there.

So I changed a few things to emulate the datasheet conditions.

The DUT is running at Idss with Vgs (DC) = 0V.

The gate current and voltage are measured to determine Zin.

The maths returns a Ciss of 28.5p.

So close enough to the 30p of the datasheet.

Less successful with Crss.

I have 4p (compared to 6p of DS) at Vgd of -10V and Id=0.

But then the small value makes it diffcult to tell whether it is a result of the model,

or that of the method.

Patrick

.

The DUT is running at Idss with Vgs (DC) = 0V.

The gate current and voltage are measured to determine Zin.

The maths returns a Ciss of 28.5p.

So close enough to the 30p of the datasheet.

Less successful with Crss.

I have 4p (compared to 6p of DS) at Vgd of -10V and Id=0.

But then the small value makes it diffcult to tell whether it is a result of the model,

or that of the method.

Patrick

.

Attachments

Less successful with Crss.

I have 4p (compared to 6p of DS) at Vgd of -10V and Id=0.

But then the small value makes it diffcult to tell whether it is a result of the model,

or that of the method.

In slightly skeptical of the model, Cgd 20pf even while Cgs has (false resolution IMO) 25.48pF. The layout seems too symmetrical to me for that much difference so I usually make Cgs and Cgd closer to equal. As mentioned before the JFET level 1 model is not that accurate. I don't know of any free simulators that do the full Curtice model.

You could blow up the two graphs of the Toshiba datasheet and measure M (the log/log slope) and see if it is right and compute Cgs and Cgd with a little algebra. I think it's safe to say they used the standard test jigs back in the day which are on the web somewhere.

Last edited:

I shall try to do a real measurement to verify.

I know the models are not accurate representation of real devices.

It just gives me a easy check to see if I am thinking in the right direction.

Strange enough, the measurement method people recommend do not always corresponds to the test conditions in datasheets.

http://www.nxp.com/assets/documents/data/en/application-notes/AN211A.pdf

But I do believe the latest version can be a good and simple way to measure Ciss.

Patrick

I know the models are not accurate representation of real devices.

It just gives me a easy check to see if I am thinking in the right direction.

Strange enough, the measurement method people recommend do not always corresponds to the test conditions in datasheets.

http://www.nxp.com/assets/documents/data/en/application-notes/AN211A.pdf

But I do believe the latest version can be a good and simple way to measure Ciss.

Patrick

So I did 2 measurements today using the circuit in #64.

Vg needed a high Zin buffer (OPA192).

Stray capacitance of the setup was pre-calibrated (0.8pF) and substracted.

With Vds = 10V, Vgs = 0V, driving signal 100mV 10kHz (not 1MHz as in datasheets), Ciss for

2SK170BL = 22.4p

2SK222E = 10.2p

So the measured values are some 25% lower than datasheet.

But it gives a good indication for such a simple setup.

Patrick

Vg needed a high Zin buffer (OPA192).

Stray capacitance of the setup was pre-calibrated (0.8pF) and substracted.

With Vds = 10V, Vgs = 0V, driving signal 100mV 10kHz (not 1MHz as in datasheets), Ciss for

2SK170BL = 22.4p

2SK222E = 10.2p

So the measured values are some 25% lower than datasheet.

But it gives a good indication for such a simple setup.

Patrick

Last edited:

Scott pointed to Dimitri's lately published, new article on SMD JFET noise.

https://www.diyaudio.com/forums/hea...ltra-low-noise-suggestions-3.html#post5606660

I thought this is a more relevant thread to discuss his findings further.

I am of course eager to know what his new findings are, and managed to gain access for a quick read.

Amongst the newly measured devices, the OnSemi CPH3910 and 2SK2394 have the lowest noise.

These are devices On Semi took over from Sanyo in around 2011.

So they ar enot totally new, and I knew them also from before.

They both unfortunately havce rather low Vds ratings, and at the same time high Idss.

Being SMD devices, dissipation is also limited.

So they are more useful when cascoded and heavily degenerated to reduce the bias current.

Transconductance is about the same as a 2SK170 at the same current.

The surprise candidates are actually MMBF5103 and BSR58, which are not designed for analogue use.

So there are no noise specifications in the datasheets, and are probably not guaranteed.

But the noise level is compariable to the above two.

The only problem with them is the very high Idss (up to 80mA) and no grading.

They will be super though as self-biasing cascodes.

The Linear System devices are OK for noise, considering their low transconductances.

But precisely the latter is my problem with them.

Hopefully Dimitri will add his comments.

Patrick

https://www.diyaudio.com/forums/hea...ltra-low-noise-suggestions-3.html#post5606660

I thought this is a more relevant thread to discuss his findings further.

I am of course eager to know what his new findings are, and managed to gain access for a quick read.

Amongst the newly measured devices, the OnSemi CPH3910 and 2SK2394 have the lowest noise.

These are devices On Semi took over from Sanyo in around 2011.

So they ar enot totally new, and I knew them also from before.

They both unfortunately havce rather low Vds ratings, and at the same time high Idss.

Being SMD devices, dissipation is also limited.

So they are more useful when cascoded and heavily degenerated to reduce the bias current.

Transconductance is about the same as a 2SK170 at the same current.

The surprise candidates are actually MMBF5103 and BSR58, which are not designed for analogue use.

So there are no noise specifications in the datasheets, and are probably not guaranteed.

But the noise level is compariable to the above two.

The only problem with them is the very high Idss (up to 80mA) and no grading.

They will be super though as self-biasing cascodes.

The Linear System devices are OK for noise, considering their low transconductances.

But precisely the latter is my problem with them.

Hopefully Dimitri will add his comments.

Patrick

The Process 51 isn't very quiet but the devices can still be quiet useful.

Some of the old Fairchild FET's are surprising like the J305 (SMT only now?). BTW I assume some here recycle the classic FET's, you can only use one or two preamp/linestages at once anyway. They do have at least 9 lives.

Interesting. Two devices from process 51 are used in an example of very low noise amplifier in this application note from Fairchild (now OnSemi): https://www.onsemi.com/pub/Collateral/AN-6602.pdf.pdf

Fairchild no longer exists.

Does that AN not look like a re-issue of a very old one ?

Low noise without numbers is a very vague definition.

We measured J111s before and they are not bad, but not 2SK170 level.

I do not understand why people only keep looking for 2SK170 when the likes of 2SK369 or 2SK372 can still be found.

Patrick

Does that AN not look like a re-issue of a very old one ?

Low noise without numbers is a very vague definition.

We measured J111s before and they are not bad, but not 2SK170 level.

I do not understand why people only keep looking for 2SK170 when the likes of 2SK369 or 2SK372 can still be found.

Patrick

See also here for noise of J110 :

https://www.diyaudio.com/forums/equ...000-measurement-preamplifier.html#post5667320

Patrick

https://www.diyaudio.com/forums/equ...000-measurement-preamplifier.html#post5667320

Patrick

- Home

- Amplifiers

- Pass Labs

- More FET noise measurements (for EUVL)