Like many, I have used Ian's PCB with the 1541a for several years. It works and to my ear sounds great at 44k to 192k without issue. But if I understand correctly that does not mean it is as good as it could be. If I am not mistaken, getting 15 bit depth vs 16 does not mean it does not work. It means we are running with a lower signal to noise ratio than the rated performance of the 1541a.

The way I see it is:

Losing the LSB is not that important as it is 1/65536th of the original resolution which won't affect the SNR or be audible. (Its not that the bits have all been shifted right resulting in 15bit data which would half the resolution to 32768)

All 16bits are processed by the board, but just that the 16th is (apparently) not clocked in - i.e. its missed so presumably its latch content will not change but all other 15 will be correct. The dac accuracy is only 0.5 - 1 LSB anyway so the LSB could be wrong by chance.

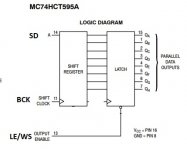

I have attached what I think is functionally equivalent of the 1541's input, register & latch (only 8 bits shown).

The data appears at the output of the register and is available to the latch when LE goes high according to the data sheet.

But according to Ian, the latch does not actually freeze the data until LE goes low, hence he says the LSB is not missed.

However, only in the multiplexed modes does the falling edge of LE latch the data so is Ian wrong, or is the datasheet not explicit or does it not actually matter?

Attachments

Last edited:

S/N Limits of …

a CD is 96dB.

the TDA1541A is 98 - 110dB.

the Human auditory system is approximately 21 bits or 123dB.

I believe 15 bit audio is around 90dB. I suspect most of us will hear it. It may fall into the territory of do you hear difference in cables, but at least this one has a measurement.

a CD is 96dB.

the TDA1541A is 98 - 110dB.

the Human auditory system is approximately 21 bits or 123dB.

I believe 15 bit audio is around 90dB. I suspect most of us will hear it. It may fall into the territory of do you hear difference in cables, but at least this one has a measurement.

Undithered bit-depth reduction from 16-bits to 15 should be audible to at least some people.

Given that no one seems to hear the missing 1 in a balanced dac, I have serious doubts about that.

"Please go ahead. I confirmed many times that my timing has no problem. it's just a new synchronized way to design that different from transitional TDA1541 driver.

The guy's issue was that the Japanese CD player outputs Sony format (left justified) rather than standard I2S(Phillips format) which will cause wrong on MSB.

I'm focusing on the LifePO4 /ultra capacitor power supply now. So I don't think I have time for now to discuss this issue on the thread.

Thank you so much.

Ian" _______________

The guy's issue was that the Japanese CD player outputs Sony format (left justified) rather than standard I2S(Phillips format) which will cause wrong on MSB.

I'm focusing on the LifePO4 /ultra capacitor power supply now. So I don't think I have time for now to discuss this issue on the thread.

Thank you so much.

Ian" _______________

.

But according to Ian, the latch does not actually freeze the data until LE goes low, hence he says the LSB is not missed.

However, only in the multiplexed modes does the falling edge of LE latch the data so is Ian wrong, or is the datasheet not explicit or does it not actually matter?

I think this really is the crux of it. Does it, or does it not drop the LSB. And if it does, does it really matter?.

I think this really is the crux of it. Does it, or does it not drop the LSB. And if it does, does it really matter?.

It seems that both EC Designs and Ian's both work with the TDA1541 but does it lose the LSB, if it does, its probably not audible, but if ECD's sounds marginally better, could this be why?

So still unanswered questions, but let's move on unless someone has the definitive answer.

It seems that both EC Designs and Ian's both work with the TDA1541 but does it lose the LSB, if it does, its probably not audible, but if ECD's sounds marginally better, could this be why?

So still unanswered questions, but let's move on unless someone has the definitive answer.

IIRC the assertion that EC's 'sounds better' was a subjective finding from a person who happens to sell a PCB of the circuit?.

I would like to know if it does indeed drop the LSB. Ian has said more than once that it does not, yet others say it does. As one of the few (only?) I2S to PCM which is plug and play, and this being the 'ultimate 1541A' thread, I think it should stay open for investigation/comment. I am sure there are others who might be looking to purchase his board for use with 1541A, which is why I'm a little surprised that Ian does not make some effort to clear this up, either here where most of the discussion has been held, or at his own thread where the same question was asked a couple of weeks ago.

Last edited:

Playing undithered -78 dBFS tone on 15 bit DACs will result in LSB bit toggling. If you go lower than that (-79 dBFS and so on, in -1 dBFS steps) the FFT and the signal amplitude should stay the same since DAC will lack resolution to play it. If it changes up to around -84 dBFS it means that the DAC has 16 bits of resolution.

IIRC the assertion that EC's 'sounds better' was a subjective finding from a person who happens to sell a PCB of the circuit?.

I would like to know if it does indeed drop the LSB. Ian says it does not, others say it does. As one of the few (only?) I2S to PCM which is plug and play, and this being the 'ultimate 1541A' thread, I think it should stay open for investigation/comment.

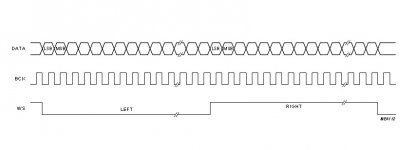

I found this timing diagram on the TDA1543 datasheet which shows I2S format.

You can see that the LSB is clocked in after WS changes. This also explains why there is a one cycle delay before the MSB of the next word is sent.

So the TDA1541 in I2S mode can clearly handle this no problem, but maybe it can also handle it in simultaneous mode and Ian has discovered this. (He hints at this in his reply). So hence he would be correct in saying the LSB is not lost.

It also could explain the distortion I've heard if his board has not been fed with I2S but with standard PCM data format.

With this, apart from WS being inverted, the MSB is sent immediately WS changes. In other words, all the data fits in the WS window and there is no over lap.

In my case, the MSB must be missed but this doesn't matter provided its zero - ie the audio is below 1/2 of full scale.

Is the dac receiving 15bits + the MSB from the next word, which if zero, has no effect? But on louder passages it becomes '1' then it causes a drastic change in the data, heard as the distortion.

Attachments

I found this timing diagram on the TDA1543 datasheet which shows I2S format.

You can see that the LSB is clocked in after WS changes. This also explains why there is a one cycle delay before the MSB of the next word is sent.

So the TDA1541 in I2S mode can clearly handle this no problem, but maybe it can also handle it in simultaneous mode and Ian has discovered this. (He hints at this in his reply). So hence he would be correct in saying the LSB is not lost.

.

Ian remains adamant that the LSB is indeed included.

@3lite - I think to understand what you are suggesting, a conclusive method to settle all. Great !!. Unfortunately, I have neither the broader understanding nor the means in which to conduct the test.

Someone?. (Ian, yeah that'd be good).

Last edited:

LSB test

Try what I suggested here.Ian remains adamant that the LSB is indeed included.

@3lite - I think to understand what you are suggesting, a conclusive method to settle all. Great !!. Unfortunately, I have neither the broader understanding nor the means in which to conduct the test.

Someone?.

Reviewing the track list, Track_15 in post #48 is to be used for MSB adjustment. Sorry for the wrong information.

Track_11 to Track_15

Track_11 to Track_15

Reviewing the track list, Track_15 in post #48 is to be used for MSB adjustment. Sorry for the wrong information.

Track_11 to Track_15

Thanks.

I will try it

.

So what is the algorythm if we want to check and adjust for example diskrete unit

1. track 15 to adjust MSB

2. track 14 to adjust MSB-1]

3. ....

Or something else?

pcb file

Very impressive work as usual! Any chance of you sharing this pcb file as I like to try the process of pcb diy.

For those who are interested in getting a PCB, click here.

Very impressive work as usual! Any chance of you sharing this pcb file as I like to try the process of pcb diy.

Very impressive work as usual! Any chance of you sharing this pcb file as I like to try the process of pcb diy.

Thanks very much.

I assume you mean the gerber files.

Gerbers- use at your own risk.

Last edited:

Thank you very much!!

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A