The one shown at post 6315 powered in 2.5 v , routed on 4 layers , I tried it on 2 layers it works but it is very noisyWhat exact EC schematic You use for I2S to Time Simoultaneous format?

Thanks ?

.

Thanks Zoran.

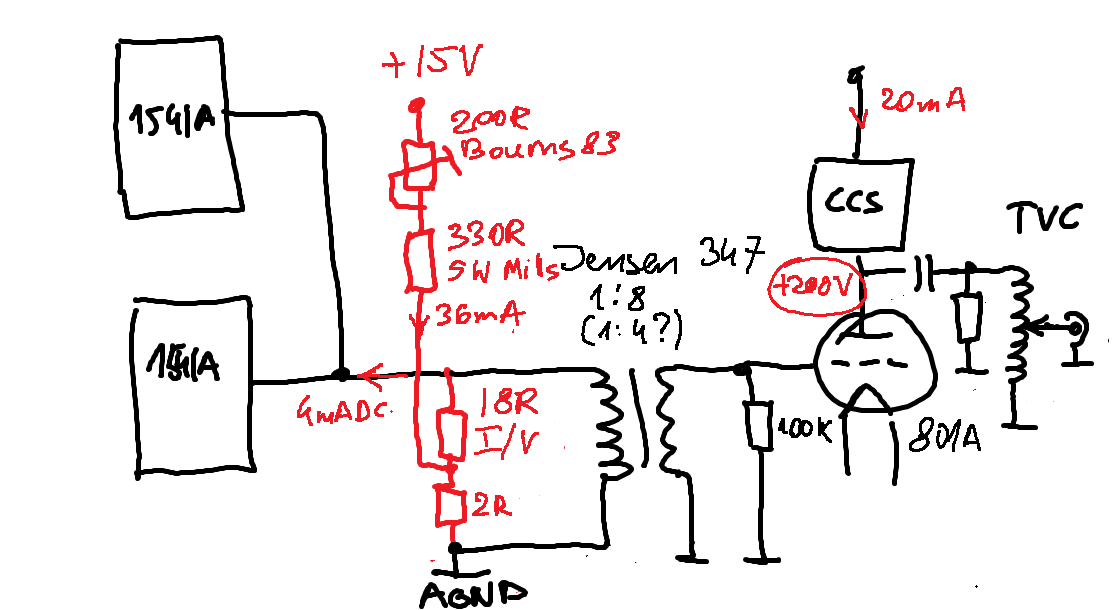

I think I have finally figured out what I want to do:

The tube stage is Bartola 801A that has been up and running (wonderfully!) as a preamp since last summer.

1) Parallel TDA1541A; motivated by findings of audio enthusiasts from early 2000's, e.g. Andrea Galavotti or AquaBlue TDA1541A

Balancing would not give the DC cancellation, my Jensen SUT unfortunately is not bifilar wound so balancing would just require extra circuitry in the digital domain with own problems and uncertain reward. I already have the PSU ready for 2 chips so why not try paralleling.

2) Passive I/V with John's DC cancellation scheme from post #7981 adopted to the situation, coupled to Jensen 347. My first guess is about 18R, giving

72mVmax before the transformer and 0,576Vmax at the grid. Although SUT should stand it (specs say -10dBu=0.35Vmax@20Hz), this may be too much gain but the parallel connection allows to experiment with very low I/V values, below 10R, which give low harmonics: MVLabs IV selection I can also try connecting SUT secondaries in parallel to make it 1:4.

3) I need raw voltage for the +15V and this is my headache now as I don't seem to have a free line anywhere and -15V line is wher the offset current sinks to so cannot use it, right?

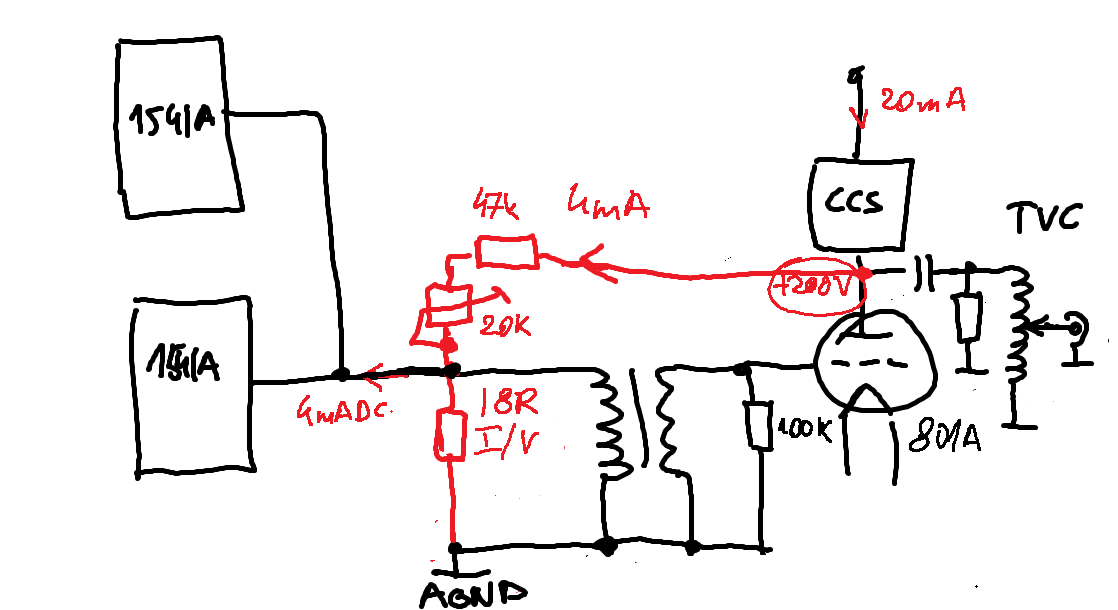

4) Another, more crazy idea is to follow John from #7981 and make use of the +200V that I already have at the output tube:

We discussed it also here #7574. I guess what John ment with CCS being grainy was using just CCS to output pin, while here I'd have both CCS and 50k resistor. For some unknown to me reason in the previous discussion in 2020 I opposed connecting the DAC AGND to the tube ground, which killed the HV bias idea, but I can't find any good reason why I did so. Both DAC and 801A stage will share the same housing, all the connections are short, internal runs so connecting the grounds shall not be a problem.

Comments welcome

I think I have finally figured out what I want to do:

The tube stage is Bartola 801A that has been up and running (wonderfully!) as a preamp since last summer.

1) Parallel TDA1541A; motivated by findings of audio enthusiasts from early 2000's, e.g. Andrea Galavotti or AquaBlue TDA1541A

Balancing would not give the DC cancellation, my Jensen SUT unfortunately is not bifilar wound so balancing would just require extra circuitry in the digital domain with own problems and uncertain reward. I already have the PSU ready for 2 chips so why not try paralleling.

2) Passive I/V with John's DC cancellation scheme from post #7981 adopted to the situation, coupled to Jensen 347. My first guess is about 18R, giving

72mVmax before the transformer and 0,576Vmax at the grid. Although SUT should stand it (specs say -10dBu=0.35Vmax@20Hz), this may be too much gain but the parallel connection allows to experiment with very low I/V values, below 10R, which give low harmonics: MVLabs IV selection I can also try connecting SUT secondaries in parallel to make it 1:4.

3) I need raw voltage for the +15V and this is my headache now as I don't seem to have a free line anywhere and -15V line is wher the offset current sinks to so cannot use it, right?

4) Another, more crazy idea is to follow John from #7981 and make use of the +200V that I already have at the output tube:

We discussed it also here #7574. I guess what John ment with CCS being grainy was using just CCS to output pin, while here I'd have both CCS and 50k resistor. For some unknown to me reason in the previous discussion in 2020 I opposed connecting the DAC AGND to the tube ground, which killed the HV bias idea, but I can't find any good reason why I did so. Both DAC and 801A stage will share the same housing, all the connections are short, internal runs so connecting the grounds shall not be a problem.

Comments welcome

The DC nulling device must be separate for every TDA output , that means 4 output in your schematic , all TDA output are different ( +/- 15 % ) , you should consider that fact in drawing your schematic

and when in parallel , because of that fact they interact each other if you don't solve this "problem" , paralleling device is not as simple as its seems

making measurements shows it very precisely

.

and when in parallel , because of that fact they interact each other if you don't solve this "problem" , paralleling device is not as simple as its seems

making measurements shows it very precisely

.

Last edited:

the first way of biasing is OK.I think I have finally figured out what I want to do

I will post formulas for this EC design concept of 2mA biasing.

But You should adopt sch for each dac unit to be adjusted separately after temperature stabilization.

Or You can use simple JFET CSS for EACH dac unit, as @Icsaszar referred.

.

Second with taking DC voltage from HV part, after isolation transformer, is NOT a good way to go.

About total gain after dacs units:

Gain of the 10Y stage is stated as +18db, that is gain of about abs(-A)=8 X.

You have 2x TDA1541A in parallel that will be 2 x 4mAp-p = 8mAp-p

total Riv @18ohms will give 0,144Vp-p

After the step-up transformer 1:4 will be around 4 x 0.144Vp-p=0.576Vp-p,

and after Tube stage will be 4 x 0.576Vp-p=2.3Vp-p.

little less with losses...

(For my opinion that is good output level better than 4.6Vp-p, with 1:8 step-up connection.)

.

The question is where to put the Volume POT?

And What is the right value of the POT?

Is the transformer and tube stage mounted in the same box in DAC part?

And so...

That is pretty much depend on what You have after 10Y stage and deserves a own post.

.

Also You can manage phase in proper way:

@Riv voltage is out of phase (phase shift of 180deg)

@tube stage voltage also is out of phase (another phase shift of 180deg)

That will bring the voltage output phase to 0deg...

So the transformer should be connected in phase. Black dots on prim and sec should be connected to signal and unmarked to grounds.

This is the right formula to calculate this @ecdesigns biasing and Riv concept

img_5902-jpg.1004599

from post

#7,993

Ra<Riv

but not commented how smaller, for Riv=18R 10% value is Ra=1.8R or 2.2R standard value...

Mind the currents in Rs could be higher.

Best way is to simulate.

.

Example for each DAC unit sch

Vb=+5Vdc

Ra=3.3ohm

Riv=36ohms (in parallel 18ohms)

Rx=206.9 ohm (total to adjust)

img_5902-jpg.1004599

from post

#7,993

Ra<Riv

but not commented how smaller, for Riv=18R 10% value is Ra=1.8R or 2.2R standard value...

Mind the currents in Rs could be higher.

Best way is to simulate.

.

Example for each DAC unit sch

Vb=+5Vdc

Ra=3.3ohm

Riv=36ohms (in parallel 18ohms)

Rx=206.9 ohm (total to adjust)

Last edited:

Note about direct connection of the transformer as reactive load to DACs output:

This is a good transformer.

But maybe it is not godd idea to load DACs Iout with reactive load?

Mainly hughe capacitive load in thos case.

from

https://www.jensen-transformers.com/wp-content/uploads/2014/10/jt-347-axt-18.pdf

Capacitances are given to shield and case only, not coils capacitances. That is why the secondary capacitance is lower than primary inspire to have 8 times more turns and should be higher capacitance than primary...

it has 1000pF of primaries in series

and 245pF in series of secondary (this will be significantly lower in parallel connection of Sec. for 1:4 step-up)

But still even if its halfs a double that will be about 120pF and that is huge in mind of reverse transfotmation ratio back to the prim.

.

Capacitances from secondary reflecting to the primary side AND DAC Iout for 16 times or 64 times (square of the transformation ratio 1:4 or 1:8 times)

.

The same is about inductace. inductace also reflecting AND adding to the primmary...

.

That could be an issue, and because of that matter people using non-inductive and low capacitive Riv

.

One of the solutions can be a buffer between DAC Riv and Transformer. That has no additional inductive component and capacitive component is a much much lower in range of G-D-S capacitances about 10-20pF (without amplification there is no Miller effect)

compared to 1000-2000pF or more with the transformer...

And simple JFET Buffer can be with very low output resistance in range of specified 27 to 47ohms for driving transformer in LF domain that determine by Rds-on value...

...

Another thing is huge deferent in signal levels:

This trafo is for MC usage it is about 0.3mV probably more in the peak range

But You will have about 144mV of signal @xfrm...

Maybe this transformer can stand this much higher level than designed for, but in general transformers of this type is less "happy" with increasing signal level?

.

This is a good transformer.

But maybe it is not godd idea to load DACs Iout with reactive load?

Mainly hughe capacitive load in thos case.

from

https://www.jensen-transformers.com/wp-content/uploads/2014/10/jt-347-axt-18.pdf

Capacitances are given to shield and case only, not coils capacitances. That is why the secondary capacitance is lower than primary inspire to have 8 times more turns and should be higher capacitance than primary...

it has 1000pF of primaries in series

and 245pF in series of secondary (this will be significantly lower in parallel connection of Sec. for 1:4 step-up)

But still even if its halfs a double that will be about 120pF and that is huge in mind of reverse transfotmation ratio back to the prim.

.

Capacitances from secondary reflecting to the primary side AND DAC Iout for 16 times or 64 times (square of the transformation ratio 1:4 or 1:8 times)

.

The same is about inductace. inductace also reflecting AND adding to the primmary...

.

That could be an issue, and because of that matter people using non-inductive and low capacitive Riv

.

One of the solutions can be a buffer between DAC Riv and Transformer. That has no additional inductive component and capacitive component is a much much lower in range of G-D-S capacitances about 10-20pF (without amplification there is no Miller effect)

compared to 1000-2000pF or more with the transformer...

And simple JFET Buffer can be with very low output resistance in range of specified 27 to 47ohms for driving transformer in LF domain that determine by Rds-on value...

...

Another thing is huge deferent in signal levels:

This trafo is for MC usage it is about 0.3mV probably more in the peak range

But You will have about 144mV of signal @xfrm...

Maybe this transformer can stand this much higher level than designed for, but in general transformers of this type is less "happy" with increasing signal level?

.

For my opinion best way is to add a buffer after Riv

Suply can be only addtional +15V (that can be used for biasing DAC)

-15V is already present in some form.

It will be combined Digital and Analog power supply (there is no pure Analog part in DAC)

In that way there are a minimum reactive transfer to the DAC chip and after the transformer is pure Analog side

with galvanic isolation if the grounds are not connected and if separate power supply are used...

Suply can be only addtional +15V (that can be used for biasing DAC)

-15V is already present in some form.

It will be combined Digital and Analog power supply (there is no pure Analog part in DAC)

In that way there are a minimum reactive transfer to the DAC chip and after the transformer is pure Analog side

with galvanic isolation if the grounds are not connected and if separate power supply are used...

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A