Don’t worry about me, I just had some stuff to get through. It stayed on topic more or less, so no sweat.

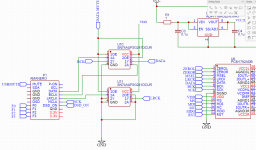

I would like to route all the controls and flags from Amanero to uC and then the uC will control muting (soft and output relay), setup the D/A chip into proper mode etc.

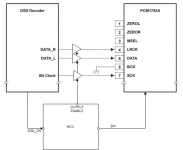

My biggest concern is the requirement of setting up DSD mode before applying DSD signal to PCM1792.

Thanks to Jesper for recommending books, gonna dive into it.

Regarding output stage im the final revision I think about using tubes. Two circuits come to mind: one that I’ve drawn as a line preamp: two stage, differential, Dual triode ltp with CCS and MOSFET follower stage with CCS.

Other one is differential mu-follower.

Just to keep you interested

I’m open to changing USB interface in future, but now Amanero stays, just because I can borrow one from a friend

Guess It’s time to start drawing schematics.

I would like to route all the controls and flags from Amanero to uC and then the uC will control muting (soft and output relay), setup the D/A chip into proper mode etc.

My biggest concern is the requirement of setting up DSD mode before applying DSD signal to PCM1792.

Thanks to Jesper for recommending books, gonna dive into it.

Regarding output stage im the final revision I think about using tubes. Two circuits come to mind: one that I’ve drawn as a line preamp: two stage, differential, Dual triode ltp with CCS and MOSFET follower stage with CCS.

Other one is differential mu-follower.

Just to keep you interested

I’m open to changing USB interface in future, but now Amanero stays, just because I can borrow one from a friend

Guess It’s time to start drawing schematics.

I have found that this solution may not be fast enough, so I successfully used 2 better solutions in 2 different projects:[...]

I would like to route all the controls and flags from Amanero to uC and then the uC will control muting (soft and output relay), setup the D/A chip into proper mode etc.

My biggest concern is the requirement of setting up DSD mode before applying DSD signal to PCM1792.

[...]

- MUTE pin from Amanero board set the output relay directly, but it is also read from the MCU, which keep soft mute active a few ms more than Mute pin. Meantime, all DAC registries are set.

- MCU controls both, HW and SW mute, but I used dual core ESP32 Wroom, so the sketch has 2 loops - one high speed loop for critical processes, including reading Mute pin, on core #0; other one, on core #1, for display, IR, rotary encoder, reading buttons (not so critical actions).

Will sw muting stop PCM1792 from locking up when DSD comes before DSD setup is ready?

Doesn't look like there would be any reason to expect that from looking at the data sheet.

Kind of looks like the dac chip was designed with the expectation that if DSD was going to be played that an SACD would be put in an associated transport and there would be lots of time to know that DSD would be playing soon and would continue for so long as the SACD was present.

Now that DSD and PCM streaming can be mixed either there will be enough time between DSD_ON being asserted and DSD playback start to allow a mode change or else some other solution would have to be found (e.g. manual PCM/DSD mode switching by the user, probably the worst case fix).

Way you might find out what works and what doesn't would be to measure and or experiment as needed. If you really want to know for sure now you could borrow the Amanero sooner rather than later and measure the DSD_ON timing with a scope. Otherwise, what is there to do but plan to deal with it later?

Last edited:

I presume the answer is no, but a hw mute will make this timing issue silent. This time, MCU can read Amanero flag pins, so it properly set the DAC chip. Don't forget to assign an I/O MCU pin to RTS pin of PCM1792, jus in case.Will sw muting stop PCM1792 from locking up when DSD comes before DSD setup is ready?

In case of AD1955 chip, a software reset is enough.

Here it is an interesting thing about timing:

Amanero board has a very good implementation of Mute flag on its pin. If it directly send a command to a high quality signal relay, there will not be clicks and pops in the speakers during PCM-DSD changes.

XMOS does not have such an implementation. I refer to my own designs and I have no any experience with commercial ones. The XMOS reference design doesn't include a mute function, but a stream on/off function can be used. Basically, an assigned I/O XMOS pin to the stream function will act as mute pin, since it is low until a new SR is setup. It works, but it is not fast and long enough, so a small pop noise can still be heard in the speakers. I have managed to increase the command duration, using a timer in audio.xc file, but i didn't find a way to start it sooner.

Fortunately, this issue was solved unintentionally: isolating i2s signals and reclocking them (using flip-flops) induced a short delay of data arriving to DAC chip, which perfectly matches the assertion of stream_of pin.

Sorry for delay in my replies. We are preparing polish RSD drops and it takes a lot of time. I've recieved support from TI forums, see attached. They recommended using a tri-state buffer, e.g. SN74AUP2G241. I think I'll try that approach plus sw muting, plus hw muting (mix of Amanero and uC for PCM inputs).

Attachments

How about that?

Up to you. If that's what you want to try, then try it. If it doesn't work maybe try what Thorp described.

Remember, it may be you are planning to use the chip in circumstances not envisioned by its designers so you may have to experiment a little at some point to get the project working the way you want.

Up to you. If that's what you want to try, then try it. If it doesn't work maybe try what Thorp described.

Remember, it may be you are planning to use the chip in circumstances not envisioned by its designers so you may have to experiment a little at some point to get the project working the way you want.

I borrowed the idea of uC controlled reset from Thorp.

You say it’s not the perfect chip for the job? What else would you see in this place from this series? Mamy said that some of them have additional TDMC input eg. PCM1792, how is that a con? DSD1792 seems to be easier to implement, but is more expensive and harder to get.

I borrowed the idea of uC controlled reset from Thorp.

You say it’s not the perfect chip for the job?

No, not what I meant.

IIRC what Thorp found that was Amanero (or XMOS) MUTE (and or maybe DSD_ON) should directly gate off LRCK,etc., to the dac chip, and MUTE (and or DSD_ON) should also be read by the MCU. The MCU should then have the option continue to gate off LRCK, etc., a bit longer after Amanero resets its MUTE signal, if found to be necessary.

The reason for MUTE/DSD_ON to gate off LRCK directly in hardware is to make the gating happen as quickly as possible, which even then may not be fast enough to prevent a pop noise or some other problem such as lockup. Going through the MCU to start the gating will definitely be slower.

EDIT:Obviously, if DSD-ON were used to start hardware gating, then the MCU would need to be able to override that gating after dac registers are programmed to accept DSD.

If hardware gating is not fast enough, then LRCK and the other I2S signals may need to be delayed in a D-Type Flip-Flop (or maybe a two-stage FF delay) so that gating-off can take effect before DSD gets to the dac chip on LRCK pin.

Rather than build it first then fix/redo it if it doesn't work right, still seems to me that getting possession of the Amanero and measuring its MUTE timing, and DSD_ON timing, relative to the start of DSD streaming call tell you right now how the hardware will need to be designed to avoid lockups.

Last edited:

On the other hand, DSD1792 only saves what, around $5, at Mouser as compared to choosing one of the other DSD capable chips in the same family that doesn't support TDM. That $5 might be a cheap price to pay in order to guarantee lockup into TDM mode won't be a problem.

Doesn't mean you won't have to deal with pops and clicks, of course. Hard to say at this point.

Bottom line for me is that this is your project. We who are observing and or making suggestions don't have to do all the work

Doesn't mean you won't have to deal with pops and clicks, of course. Hard to say at this point.

Bottom line for me is that this is your project. We who are observing and or making suggestions don't have to do all the work

Last edited:

On the other hand, DSD1792 only saves what, around $5, at Mouser as compared to choosing one of the other DSD capable chips in the same family that doesn't support TDM. That $5 might be a cheap price to pay in order to guarantee lockup into TDM mode won't be a problem.

This is a very good point. From PCM1792/DSD1792 and DSD1794, they all have this problem. So it's either me dealing with it, or different chip manufacturer.

I think I have an algorithm ready to go:

Amanero gives MUTE flag everytime it changes format or sampling

Everytime MUTE flag from Amanero forces tri-state buffers into high Z state and mutes the output

uC recognizes audio format with Amanero flags and DSD flag, sets PCM1792A into proper mode

Tri-state buffers are released and data reaches PCM1792A

I just hope it will be fast enough to be impossible to notice when playing.

Amanero gives MUTE flag everytime it changes format or sampling

Everytime MUTE flag from Amanero forces tri-state buffers into high Z state and mutes the output

uC recognizes audio format with Amanero flags and DSD flag, sets PCM1792A into proper mode

Tri-state buffers are released and data reaches PCM1792A

I just hope it will be fast enough to be impossible to notice when playing.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Digital Line Level

- DSD1794/2 + Amanero DIY DAC - how to start?