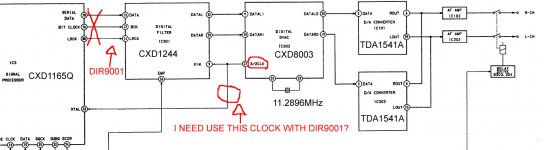

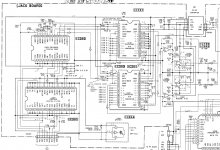

Hello, i have one DAC board with 2 TDA1541A S1 (1crown) with one CXD8003 and one CXD1244. (from old Sony cd player CDX-A2001).

I will like to recyle this dac, i will like add one SPDIF receiver on this board; With one DIR9001, wm8804, cs8414, or one IC compatible with this circuit:

I need reclock the CXD1244 chip with the same clock of the DIR9001?

Or i can use the same 3/2 clock pin from cxd8003 chip?

Please i will like reuse this board with one spdif input to the CXD1244 chip.

I sorry for my bad English.

Thank you.

I will like to recyle this dac, i will like add one SPDIF receiver on this board; With one DIR9001, wm8804, cs8414, or one IC compatible with this circuit:

I need reclock the CXD1244 chip with the same clock of the DIR9001?

Or i can use the same 3/2 clock pin from cxd8003 chip?

Please i will like reuse this board with one spdif input to the CXD1244 chip.

I sorry for my bad English.

Thank you.

Attachments

You might find this thread useful : NonOversampling HELP 16 to 18 Bit Sony CDP-228ESD

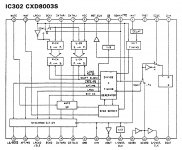

Seeing as data isn't available for CXD8003 it looks like your question isn't answerable. But we can make educated guesses. Using an S/PDIF input means the data source will be the the clock master but your schematic shows the CXD8003 as clock master (as it has an XTAL oscillator). Thus the CXD8003 feeds the clock to both CXD1244 and CXD1165 so the latter's datastream will then be in-sync with the CXD8003's clock. Feeding the CXD1124's inputs from a DIR9001 won't preserve the synchronization.

A solution (mentioned on the linked thread) is to use an MCU (as clock slave) to accept the DIR9001's output and perform the oversampling and feed the DACs. I have a project underway to do this : Cheap ARM MCUs for RBCD audio

Seeing as data isn't available for CXD8003 it looks like your question isn't answerable. But we can make educated guesses. Using an S/PDIF input means the data source will be the the clock master but your schematic shows the CXD8003 as clock master (as it has an XTAL oscillator). Thus the CXD8003 feeds the clock to both CXD1244 and CXD1165 so the latter's datastream will then be in-sync with the CXD8003's clock. Feeding the CXD1124's inputs from a DIR9001 won't preserve the synchronization.

A solution (mentioned on the linked thread) is to use an MCU (as clock slave) to accept the DIR9001's output and perform the oversampling and feed the DACs. I have a project underway to do this : Cheap ARM MCUs for RBCD audio

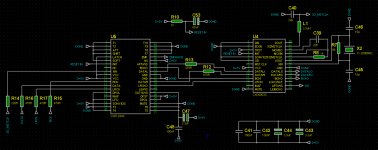

Hello, i try design this reclock for the DIR9001 for connect in the CXD1244 and CXD8003, in the output Pin 3/2 Masterclock from cxd8003:

I have configured the DIR9001 to output: 16 bit MSB Right Justified, data and a 256fs.

And reclocked with one 74hc175.

This configuration are correct?

Please anybody Help me.

Thank You!

I have configured the DIR9001 to output: 16 bit MSB Right Justified, data and a 256fs.

And reclocked with one 74hc175.

This configuration are correct?

Please anybody Help me.

Thank You!

Attachments

If you still have CXD8003's crystal generating the master clock then you'll not be in sync with DIR9001's SCKO. To have any hope of working you'll need to feed SCKO from DIR9001 into CXD8003's master clock input and delete your XTAL. But then there's no guarantee that CXD8003 will work correctly when the SCKO isn't locked to incoming S/PDIF.

Or this second option are more correct?

The 3/2 masterclock pin of CXD8003 have 8... Mhz correct?

Probably the correct config of DIR9001 are 128fs, not 256fs?

Have you read the CXD1244 datasheet ?

There seems to be a good bit more to this than you understand  -- but this is a tall challenge, even for an expert.

-- but this is a tall challenge, even for an expert.

Forget the HC175 -- it won't solve any of these issues.

You have DIR9001's CKSEL (pin 28) tied low. That selects the internal PLL, but you have nothing connected to XTI (pin 8) or XTO (pin 7).

Since the 9001 appears to provide much of the 8003 and 1244's functionality, how about ignoring those parts if possible? Consider these factors:

- the CXD parts may only be capable of playing properly at 44.1 kHz

- without complete documentation, you could damage the parts with trial and error experimentation before finding the right combination; likely you'll then simply continue working through every binary possibility (that you can think of) with NO chance of success - a complete waste of time (I have done this ...) ; a block diagram and application example are just not enough

- from the CXD1244 block diagram it looks like a good bit of silicon is devoted to reversing the bit order -- are you sure you need that capability? or can tolerate it?

- the DIR9001 is a 3.3V part, while the CXD's run on 5V; it usually isn't too hard to accommodate the difference, but ignoring it could make trouble -- 3.3V signals driving 5Vcc inputs can work initially, only to cause excessive dissipation or intermittent behavior in the 5V part; in any case, placing a 470R in series is not a good idea

That's about the limit of my (alleged) brains, but I'm sure gonna keep studying the DIR9001. And thanks a bunch for introducing me to it -- it may just solve a BIG problem that recently turned up in my TV room!

Cheers

Forget the HC175 -- it won't solve any of these issues.

You have DIR9001's CKSEL (pin 28) tied low. That selects the internal PLL, but you have nothing connected to XTI (pin 8) or XTO (pin 7).

Since the 9001 appears to provide much of the 8003 and 1244's functionality, how about ignoring those parts if possible? Consider these factors:

- the CXD parts may only be capable of playing properly at 44.1 kHz

- without complete documentation, you could damage the parts with trial and error experimentation before finding the right combination; likely you'll then simply continue working through every binary possibility (that you can think of) with NO chance of success - a complete waste of time (I have done this ...) ; a block diagram and application example are just not enough

- from the CXD1244 block diagram it looks like a good bit of silicon is devoted to reversing the bit order -- are you sure you need that capability? or can tolerate it?

- the DIR9001 is a 3.3V part, while the CXD's run on 5V; it usually isn't too hard to accommodate the difference, but ignoring it could make trouble -- 3.3V signals driving 5Vcc inputs can work initially, only to cause excessive dissipation or intermittent behavior in the 5V part; in any case, placing a 470R in series is not a good idea

That's about the limit of my (alleged) brains, but I'm sure gonna keep studying the DIR9001. And thanks a bunch for introducing me to it -- it may just solve a BIG problem that recently turned up in my TV room!

Cheers

Last edited:

Гереро, подключите вывод SCKO(4) DIR9001 вместо кварца 112896 на вывод 22(XIN) микросхемы CXD8003. Кварц отключить от выводов XIN, XOUT. Настроить DIR9001 для вывода: 16-битный MSB Right Justified, data и 256fs! Соединения между CXD 1244 и CXD 8003 не трогать! Соединить DIR9001-CXD1244:

вывод 10(LRCKO) с выводом 14(LRCK IN)

вывод 11(BCKO) с выводом 12(BCK IN)

вывод 12 (DOUT) с выводом 13(DATA)

DIR9001 работает с CXD1244 очень хорошо, но больше , чем 44,1 и 48,0 Кгц Вы не получите.

вывод 10(LRCKO) с выводом 14(LRCK IN)

вывод 11(BCKO) с выводом 12(BCK IN)

вывод 12 (DOUT) с выводом 13(DATA)

DIR9001 работает с CXD1244 очень хорошо, но больше , чем 44,1 и 48,0 Кгц Вы не получите.

Гереро, подключите вывод SCKO(4) DIR9001 вместо кварца 112896 на вывод 22(XIN) микросхемы CXD8003. Кварц отключить от выводов XIN, XOUT. Настроить DIR9001 для вывода: 16-битный MSB Right Justified, data и 256fs! Соединения между CXD 1244 и CXD 8003 не трогать! Соединить DIR9001-CXD1244:

вывод 10(LRCKO) с выводом 14(LRCK IN)

вывод 11(BCKO) с выводом 12(BCK IN)

вывод 12 (DOUT) с выводом 13(DATA)

DIR9001 работает с CXD1244 очень хорошо, но больше , чем 44,1 и 48,0 Кгц Вы не получите.

English only please:

English only please:Guerrero, plug in the SCKO (4) DIR9001 output instead of quartz 112896 to output 22 (XIN) chips CXD8003. Quartz disconnect from xIN findings, XOUT. Tune DIR9001 for output: 16-bit MSB Right Justified, data and 256fs! The connections between CXD 1244 and CXD 8003 don't touch! Connect DIR9001-CXD1244:

Conclusion 10 (LRCKO) with Output 14 (LRCK IN)

Conclusion 11 (BCKO) with Output 12 (BCK IN)

Conclusion 12 (DOUT) with Output 13 (DATA)

DIR9001 works with CXD1244 very well, but more than 44.1 and 48.0 kHz you don't get.

Thanks a lot for all answers!!!!!

I have too, other dac in construction with 2 BB DAC729KH for installation with 6DJ8 tubes outputs, and i have a lot of doubts with the VOut of this DAC729KH chip for connect with the tubes.

In other page for the forum opinions/sugestions and critics too.

Thanks a lot for all help!!! For make this old Sony CDX- A2001 DAC block with/dir9001/CXD1244/CXD8003/dual TDA1541AS1 (DAC block only) live again!!

I have too, other dac in construction with 2 BB DAC729KH for installation with 6DJ8 tubes outputs, and i have a lot of doubts with the VOut of this DAC729KH chip for connect with the tubes.

In other page for the forum opinions/sugestions and critics too.

Thanks a lot for all help!!! For make this old Sony CDX- A2001 DAC block with/dir9001/CXD1244/CXD8003/dual TDA1541AS1 (DAC block only) live again!!

- Home

- Source & Line

- Digital Line Level

- Please Help for SPDIF interface on TDA1541 dac