I tend to have some trouble with hash noise with USB on my Linux based pc so I decided to buy the DIYinHK optical receiver just to try for more connection options, its a single wire directly feeding the DAM about 20cm long, plus of course the 3.3v pins to power it, to me it sounds better maybe its because its much simpler than the Xmos which costs a lot more compared to $10 and just as good if not better than Xmos in my opinion.

What is the optical source?

Sounds like it's not the XMOS interface, but if it has SPDIF output then feeding it to the dam via optical transmitter would get even better performance I think.

TNT do you know what frequency the si570 outputs when playing from the i2s input?

The reason I’m asking: I’m thinking about sourcing the dam1121 with Andreas master clocks. The idea is to attach a si570 to the dam1121 via i2c which will in turn power off the on board si570 and accepts the incoming lvds signal. But instead of feeding the lvds from the external si570 I will feed a lvds signal that I derived from TWTMC converted though an e.g. an idt 8t39204.

As I always know the SR of the incoming i2s signal it should be no problem to select between 44/48. As I don’t need spdif input I should not need other frequencies. The only quenstions here is what frequency does the dam1121 need when playing 44khz respectively 48khz i2s signals.

Greetings,

I also think at same approach, it works. Si514 delivers 45/49 mhz lvds clock signal to U2 (lvds to cmos). Dam1121 must have control of the time when 45<>49 switch occurs. As you know, dam sets aud out to low at every fs change for aprox 10ms, so i took this moment as reference, and in 1.4 ms a i2c burst occurs containing new freq parameters, si514 disables output for 2.4 ms, then aud out becomes high after 6.2ms.

So far i runed two experiments:

1. jlsounds v3 feeding dam1121, but dam hadn't control of the time at which clock selection occured, so fs was diplayed incorrectly and maybe neither the filters were proper selected, still, NO unlock condition

2. dam selected clock source from his own pair of crysteks 950 at 1.4 ms after aud out turned low, and jlsounds switched from his onboard ndk's....fs properly displayed but unlock condition occured after 30-45 min ,probably because fifo runed empty/full due to Fcrystek<>Fndk.

best regards,

Bogdan

PM if interested.

Hi bogdandascalu87, (and TNT, I think we will keep the discussion in this thread, but I needed a "good to go" from Soeren)

what lvcmos to lvds buffer/converter did you use?

I can think of to ways. One is the fairly large, "old" and difficult to handle TI LMK01801. this IC incorporates an:

The other way would be to disable the output bank of the lvds buffer/converter, so there is no clock input to the dam1121, for a short time to give the dam1121 time to "think" and than turn it on again.

One could also hijack the i2c connection to the external si570 and monitor it with a uC to turn the lvds buffer/converter outputs on and off.

Yes, TNT the idea is of course also to clock the i2s source with the ne master clock.

I found an IC (not the best specs..) that outputs max 5 lvds signals on two banks and a separate lvcmos output that can be also divided. So I'll get 44/49MHz for the dam1121 lvds and 22/24MHz lvcmos for the i2s source. (Microsemi ZL40235)

what lvcmos to lvds buffer/converter did you use?

I can think of to ways. One is the fairly large, "old" and difficult to handle TI LMK01801. this IC incorporates an:

But, I'm not sure this works...Clock Output Synchronization (SYNC)

The purpose of the SYNC function is to synchronize the clock outputs with a fixed and known phase relationship between each clock output selected for SYNC. SYNC can also be used to hold the outputs in a low or 0 state. The NO_SYNC_CLKoutX_Y bits can be set to disable synchronization for a clock group.

The other way would be to disable the output bank of the lvds buffer/converter, so there is no clock input to the dam1121, for a short time to give the dam1121 time to "think" and than turn it on again.

One could also hijack the i2c connection to the external si570 and monitor it with a uC to turn the lvds buffer/converter outputs on and off.

Yes, TNT the idea is of course also to clock the i2s source with the ne master clock.

I found an IC (not the best specs..) that outputs max 5 lvds signals on two banks and a separate lvcmos output that can be also divided. So I'll get 44/49MHz for the dam1121 lvds and 22/24MHz lvcmos for the i2s source. (Microsemi ZL40235)

Last edited:

Bogdan, did you feedback the new clocks to the jlsound for synchronisation? Did it still break after 30-45 min?

//

No, didn't try.

Hi Bogdan,

I think I misunderstood. You did not feed the dam1121 with an lvds clock, but with an lvcmos clock to U2 right?

As far as I understood, the dam1121 needs the lvds signal input, to do the reclocking inside the fpga. So I understand, that it didn't work. BUT I might be mistaken I don't know the insights of the circuit.

Greetings,

Jan

I think I misunderstood. You did not feed the dam1121 with an lvds clock, but with an lvcmos clock to U2 right?

As far as I understood, the dam1121 needs the lvds signal input, to do the reclocking inside the fpga. So I understand, that it didn't work. BUT I might be mistaken I don't know the insights of the circuit.

Greetings,

Jan

Hi bogdandascalu87, (and TNT, I think we will keep the discussion in this thread, but I needed a "good to go" from Soeren)

what lvcmos to lvds buffer/converter did you use?

Fin1001 for cmos to lvds in the first experiement. Then i removed u2 and sticked to lvcmos.

One could also hijack the i2c connection to the external si570 and monitor it with a uC to turn the lvds buffer/converter outputs on and off.

i2c way would require a noisy uC always on. I abandoned this approach in favour of a uC with deep sleep and interrupts on dam's audio enable and source Fsel.

The other way would be to disable the output bank of the lvds buffer/converter, so there is no clock input to the dam1121, for a short time to give the dam1121 time to "think" and than turn it on again.

dam fsel doesn't rely on signal clock disable, but it makes calculation on i2s input at a known clock, this results are misinterpreted if before fsel detection, source is changeing master clock from ,say, 45 to 49.

My sugestion would be 2 dual latching rf relays, 1 to switch clock for source, and one to switch dam's clock, with delay between and stick to lvcmos only. Both relays would be feeded by same pair of clock source.

Don't know if Andrea clocks could feed two sine to cmos converter. If yes, clock, dam and source would be in separate enclosurer, 1m of coax between dam and clock, 1m of coax between clock and source, and 2m of toslink between dam and source.

Hi Bogdan,

I think I misunderstood. You did not feed the dam1121 with an lvds clock, but with an lvcmos clock to U2 right?

As far as I understood, the dam1121 needs the lvds signal input, to do the reclocking inside the fpga. So I understand, that it didn't work. BUT I might be mistaken I don't know the insights of the circuit.

Greetings,

Jan

fpga and flip flops take cmos from u2, which is lvds to cmos receiver. i removed u2.

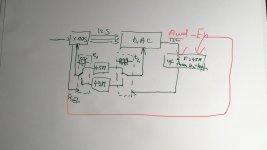

Attachments

Last edited:

Did this work?Fin1001 for cmos to lvds in the first experiement.

Then i removed u2 and sticked to lvcmos.

fpga and flip flops take cmos from u2, which is lvds to cmos receiver. i removed u2.

Now that is a really good idea!

i2c way would require a noisy uC always on. I abandoned this approach in favour of a uC with deep sleep and interrupts on dam's audio enable and source Fsel.

the dam1121 has an uC already on board, did you power this down also?

dam fsel doesn't rely on signal clock disable, but it makes calculation on i2s input at a known clock, this results are misinterpreted if before fsel detection, source is changeing master clock from ,say, 45 to 49.

My sugestion would be 2 dual latching rf relays, 1 to switch clock for source, and one to switch dam's clock, with delay between and stick to lvcmos only. Both relays would be feeded by same pair of clock source.

Don't know if Andrea clocks could feed two sine to cmos converter. If yes, clock, dam and source would be in separate enclosurer, 1m of coax between dam and clock, 1m of coax between clock and source, and 2m of toslink between dam and source.

I don't know about toslink because - isn't that the reason for the programmable si570, with different spdif sample rates different MCKL are needed in Soerens kind of implementation?

Last edited:

How do you know, that the incoming lvds signal is not used for something inside the fpga?

Maybe the lvds incoming signal is necessary for synchronization of multiple dam1121s? I want to keep the dual mono design. Why would Soeren even use lvds from the si570 instead of lvcmos?

Maybe the lvds incoming signal is necessary for synchronization of multiple dam1121s? I want to keep the dual mono design. Why would Soeren even use lvds from the si570 instead of lvcmos?

How do you know, that the incoming lvds signal is not used for something inside the fpga?

Maybe the lvds incoming signal is necessary for synchronization of multiple dam1121s? I want to keep the dual mono design. Why would Soeren even use lvds from the si570 instead of lvcmos?

Datasheet and xray of the pcb.

the dam1121 has an uC already on board, did you power this down also?

no, didn't checked...but should sleep.

I don't know about toslink because - isn't that the reason for the programmable si570, with different spdif sample rates different MCKL are needed in Soerens kind of implementation?

Either 45 or 49, fpga via si514 makes small frequency adjustments just to keep fifo buffer half full. After dam selects clock, it fills the buffer, then starts playing, buffer gets emptied at same clock rate , both determined by a sigle source clock.

This was the behaviour of your test?

It emptied because the clocks was still not really synchronous - if they where it would not have happened?

It seems you are close to a solution except the 45 min breakdown..?

//

yes.

Looking at the dam1941 that has a si570 with cmos out, the only reason for the lvds version on the dam1121 was an ease of multi system integration?

Correct.

- Home

- Source & Line

- Digital Line Level

- Building with the Soekris dam1121