Joseph:

What are you referring to ? Just curious

"Applying Your fantastic analysis software"

What are you referring to ? Just curious

Originally Posted by andrea_mori

You`re absolutely right Andrea.

I`m convinced and wanted to argue, that a properly configured Sabre or comparable newer DAC design will surely benefit from your SOTA clocks too.

Sorry, but I have to say again that the comparison between DACs technology is a little off topic in this thread, so please keep the discussion limited to the implementation of these oscillators with the various DAC architectures.

You`re absolutely right Andrea.

I`m convinced and wanted to argue, that a properly configured Sabre or comparable newer DAC design will surely benefit from your SOTA clocks too.

What are you referring to ?

Look at the web signature for more

I have quickly tried Your idea about mixing the two, 10kHz shifted signals.. I had to use my HP3336 synthetizer, it has the lowest 'skirts' that I have.. But still they are at - 110dBc.

Then I did put the resulting 10kHz signal on the RTX6001..

Doh. I got back all the dirt and skirt from my synthetizer.

Spurs from power supply residuals, the skirts from the PLL. Even higher than - 80dB spurs.

Not used to it. On my Mirand dac I'm used to - 170dBc or lower floor with very few 'features'. Applying Your fantastic analysis software, 4M or 8M point FFT. It's like an electronmicroscope into the jitter world of a dac..

But the mixing procedure works, in all case.

The question on mixer is: Does Andera use miniComponents mixer's?

While mixing the source should be sine alike and will try with some SMD 7 * 5 using 16.368 & 16.369 farnel gear.

I go far deeper with up to 33Mio FFT as 1.4milli Herz Bin width to get the beef. But shows the limitations of the used clock oscillators.

I need a 24.576 or an 2 * 12.288 solution with ultimate low PN.

May same issues about the used xco on RTX and having a accurate sine source as fs/4 or 10kHz to validate

While measure jitter with a 10G/s DSO, you will get 100ps sample intervals, so no deal to measure with a histogram a 1 ps jitter

Hp

Joseph:

What are you referring to ? Just curious

Yes, I am a happy HPW-Works user..

"The question on mixer is: Does Andera use miniComponents mixer's"

It's on the board - MCL ASK-1...

But I'm afraid that it would be complicated to 'abuse' that doubler board. All connections are fixed, the whole thing is very specialized.

What regards RTX, Jens had put NDK SD clocks in it, as far as I know.

It's on the board - MCL ASK-1...

But I'm afraid that it would be complicated to 'abuse' that doubler board. All connections are fixed, the whole thing is very specialized.

What regards RTX, Jens had put NDK SD clocks in it, as far as I know.

While measure jitter with a 10G/s DSO, you will get 100ps sample intervals, so no deal to measure with a histogram a 1 ps jitter

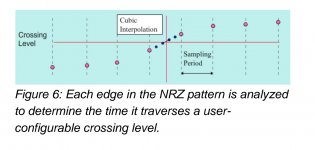

I think this figure explains in much less words that I could..

Attachments

First of all, it is not just one transition that the polynomial fit is executed on.. Then, we are talking 20/30k€ / k$ machines and above. A lot of pain was put in that adc precision, linearity, and sampling jitter.

Also true, though, that properly the use of GHz sampling rate guarantees a very high close-in phase noise floor.

So definitely these are not good tools to use for looking at these applications we are talking about here.

But perfectly usable above say, the kHz zone. And the jitter analysis packets will say a world more about problem sources (like we have seen with deterministic jitter). And there are so much fine differentiations even inside the deterministic jitter family..

So I continue not to understand the 'looking down' attitude toward these things.

Would also add, that getting used to these algorithms can give some intuitive experience in how to tune the performance, trick the procedure, sharpen the view finder..

Reassuming: not good tools for low noise oscillator design. Invaluable tools for system clock debugging, (also audio..), communications links debugging etc.

Ciao, George

Also true, though, that properly the use of GHz sampling rate guarantees a very high close-in phase noise floor.

So definitely these are not good tools to use for looking at these applications we are talking about here.

But perfectly usable above say, the kHz zone. And the jitter analysis packets will say a world more about problem sources (like we have seen with deterministic jitter). And there are so much fine differentiations even inside the deterministic jitter family..

So I continue not to understand the 'looking down' attitude toward these things.

Would also add, that getting used to these algorithms can give some intuitive experience in how to tune the performance, trick the procedure, sharpen the view finder..

Reassuming: not good tools for low noise oscillator design. Invaluable tools for system clock debugging, (also audio..), communications links debugging etc.

Ciao, George

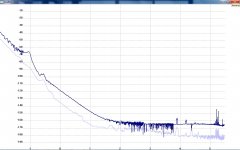

In the meantime, I am trying my best to get a working phase noise setup. This is a result with which I am quite happy, it proved to be more difficult than I had thought of..

It's a direct measurement of a Crystek CCHD950, 80MHz XO as implemented in a Buffalo II board.

The setup is the Holme analyser. I am using a 148MHz Valpey Fisher oscillator az ADC clock, that turned out to be fundamental.

Actually I like these Crystek products, one can use them as yardstick in searching for a reference performance..

It's a direct measurement of a Crystek CCHD950, 80MHz XO as implemented in a Buffalo II board.

The setup is the Holme analyser. I am using a 148MHz Valpey Fisher oscillator az ADC clock, that turned out to be fundamental.

Actually I like these Crystek products, one can use them as yardstick in searching for a reference performance..

Attachments

Last edited:

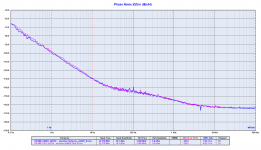

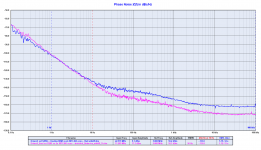

Just to show that it is not only good at - 65dBc/10Hz..

This is the other extremity, one of mine better measuring 5MHz MTI260 OCXO, against two brothers of it.

This is the other extremity, one of mine better measuring 5MHz MTI260 OCXO, against two brothers of it.

Attachments

Last edited:

Yes, I am a happy HPW-Works user..

Look at the web signature for more

Thank you ! Sorry HpW, must have been half asleep when reading Joseph K's post

In the meantime, I am trying my best to get a working phase noise setup. This is a result with which I am quite happy, it proved to be more difficult than I had thought of..

It's a direct measurement of a Crystek CCHD950, 80MHz XO as implemented in a Buffalo II board.

The setup is the Holme analyser. I am using a 148MHz Valpey Fisher oscillator az ADC clock, that turned out to be fundamental.

Actually I like these Crystek products, one can use them as yardstick in searching for a reference performance.. View attachment 886094

what is this scale -1 to 5? is it the power of 10 in (Hz) ? so 0,1Hz to 10kHz ?

Yes, the mininum shown x-axis is 10^-1= 0,1Hz, the maximum signed x-axis is 10^5= 100kHz, but the graph extends to ~500kHz.

Also do not stop at 0,1Hz, continues downwards toward the 0.01Hz. In case of a sufficiently long run. Such a run takes several hours.

Also do not stop at 0,1Hz, continues downwards toward the 0.01Hz. In case of a sufficiently long run. Such a run takes several hours.

Last edited:

In the meantime, I am trying my best to get a working phase noise setup. This is a result with which I am quite happy, it proved to be more difficult than I had thought of..

It's a direct measurement of a Crystek CCHD950, 80MHz XO as implemented in a Buffalo II board.

The setup is the Holme analyser. I am using a 148MHz Valpey Fisher oscillator az ADC clock, that turned out to be fundamental.

Actually I like these Crystek products, one can use them as yardstick in searching for a reference performance.. View attachment 886094

Just for fun, take the new Driscoll or Differential oscillators at 22 MHz and add a couple of frequency doublers, then add 6dB for each duplication.

The phase noise at 10 Hz from the carrier will be around -118dBc for 90 MHz output, only 50dB better than the Crystek at 80 MHz.

Moreover, since the duplication does not add phase noise very close to the carrier one could expect -67dBC at 0.1 Hz from the carrier, like the base 22MHz oscillator.

Maybe the Crystek is not just the best oscillator to drive the Buffalo.

Attachments

Last edited:

From the above plot we can see that in the real world the frequency duplication adds less than 3 db (-135.8 to -133), then we can expect even -124dBc at 10 Hz from the carrier for a 90 MHz oscillator, so almost 60 dB better than the Crystek.

Maybe the Buffalo could sounds better, I hope someone try it and report the impressions.

Maybe the Buffalo could sounds better, I hope someone try it and report the impressions.

So I continue not to understand the 'looking down' attitude toward these things.

Ciao, George

Did you build the phase noise measurement instrument to measure the noise floor?

If so I believe it was better if you saved 1000 Euro.

Or else you could use this money to buy a Lecroy real time digital oscilloscope since you trust more the oscilloscope than a phase noise measurement system ("Without a picosecond time of hesitation.

The instrument which is telling me the truth.

In this specific case, the oscilloscope.").

From the above plot we can see that in the real world the frequency duplication adds less than 3 db (-135.8 to -133), then we can expect even -124dBc at 10 Hz from the carrier for a 90 MHz oscillator, so almost 60 dB better than the Crystek.

When something seems to be too good to be true, it usually is.

That begins with the alleged 3 dB per duplication, the real world cannot

be unphysical.

Nobody can rightfully expect -124 dBc / 10Hz / 90MHz.

Even Pascall is 20 dB worse, and the _entry_ level subtypes

did cost quite a few K€ when I asked their German distributor

some years ago.

And the Holmes design is in the very same league as the timepod,

main difference is the missing integration into timelab.

A good starting point with a Spartan-6 eval board and a quad LT ADC.

cheers, Gerhard.

Attachments

Last edited:

Thanks Joseph, good work

and sorry I made thing more confusing by typing 10kHz in stead of 100kHz (of course I know what 10 to the power of 5 means)

I have just seen you own LP12/EKOS/KANDID, the best choice!

Is this Klaus' audio system?

I was in Koeln in 2019 May and I met Klaus and Hans to listen to Klaus' system.

Attachments

When something seems to be too good to be true, it usually is.

That begins with the alleged 3 dB per duplication, the real world cannot

be unphysical.

Nobody can rightfully expect -124 dBc / 10Hz / 90MHz.

Even Pascall is 20 dB worse, and the _entry_ level subtypes

did cost quite a few K€ when I asked their German distributor

some years ago.

And the Holmes design is in the very same league as the timepod,

main difference is the missing integration into timelab.

A good starting point with a Spartan-6 eval board and a quad LT ADC.

cheers, Gerhard.

Gerhard,

I agree with you in principle but the above phase noise plot (11 to 22 MHz) shows clearly 3dB worse at 10 Hz and almost no difference at 1 Hz and 0.1 Hz from the carrier.

This is the real world by real measurements, the 1/F3 phase noise is not affected by the frequency doubler, the 1/f noise is around 3 dB worse, while the noise floor increases by 6 dB or just a little more.

I'm not surprised because the 1/f3 is driven by the crystal (random walk of the crystal), so IMHO the physics is confirmed.

Anyway as soon as we have built the down converter we will measure the real phase noise of the duplicated 90 MHz.

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Line Level

- The Well Tempered Master Clock - Building a low phase noise/jitter crystal oscillator