Hi Thom.

Where do you see that there is just missing 5 of each?

In the TWTMC_Summary of Orders I can see there is 3 orders at a SC 25MHz crystal and zero at a AT25MHz crystal. I don`t need 7 SC 25MHz or else I have ordered it ;o) maybe 2-3...

Hi Bassilus,

I added the 3 SC with the 2 AIO 6.00/6.25 (because they will also be used for 24/25). So in the end we can agree on the same alternative so 3+2 = 5

I think there is a good chance we will reach at least 10..I might order an extra 24/25 if we are at 9..

Hi euro21. Who do you ask ;0)

The problem with SC6.25, AT6.25, AT6.00 is that the way to reach MOQ are longer, because theirs MOQ is 15. So in this moment I just see that SC25MHz with MOQ 10 is possible to reach, because there just need 7 more to order.

If there haven’t got a MOQ at the crystals, I have ordered the best solution a SC6.25MHz, the TWTMC-DRIXO-SF board, the TWTMC-DRIXO-XFMR 22-24 MHz and the TWTMC-SFDO.

Just a clarification, the TWTMC-PXO-AIO works with AT-Cut crystals only (5.6448, 6.00, 6.144, 6.25 and 6.75 MHz).

So if you would use SC-Cut to get 25MHz the only chance is the base oscillator with the crystal at 25MHz (MOQ is 10 pcs).

Unless you would use a couple of frequency doubler with crystal at 6.00 or 6.25MHz, but the MOQ is 15 pcs.

I am using different dacs TDA1541, Es9038 by Ian, DSC1 (and AK4499 or DDDAC next year) clocking with JLsounds board with NDK 45/49. BBB as the source.

My audio files are mainly 44.1, 96 and 192. Normally I try to upsample to 192 or dsd 256 with HQplayer as it works really well this way.

I fell out of my projects for quite some time. So I need to reread quite a lot of the threads as I feel to miss something.

I guess Andrea needs to complete the GB so I would really appreciate some advice.

1.

I understand that to play files up to 192 I need 22/24 Mhz SC-cut.

If I am correct from the graphs it seems that 11.2896 with doubler is very close to the 5.6448 x2 x2

If not 5/6 with or without doubler is the best.

Or 5.56448 for 44.1 and 12.2880 for 96/192?

2.

ES9038 is sensitive to MCLK, DSD to BCLK and pcm1704 to WCLK… Feel a bit confused here…

3.

I also heard that big companies use different frequencies to get certain sound signature. Is it just a yellow button?

4.

2x TWTMC-DRIXO-SF (the board)

5.6448 / 12.2880 SC-cut

TWTMC-DBM-SF (doubler )

TWTMC-STS-SX OR DX (yet do define)

TWRPS-pp to power everything

Do I miss something?

Will I be able to get some stuff in January or it is better to take options now as the new GB is unknown?

Thanks a lot!

My audio files are mainly 44.1, 96 and 192. Normally I try to upsample to 192 or dsd 256 with HQplayer as it works really well this way.

I fell out of my projects for quite some time. So I need to reread quite a lot of the threads as I feel to miss something.

I guess Andrea needs to complete the GB so I would really appreciate some advice.

1.

I understand that to play files up to 192 I need 22/24 Mhz SC-cut.

If I am correct from the graphs it seems that 11.2896 with doubler is very close to the 5.6448 x2 x2

If not 5/6 with or without doubler is the best.

Or 5.56448 for 44.1 and 12.2880 for 96/192?

2.

ES9038 is sensitive to MCLK, DSD to BCLK and pcm1704 to WCLK… Feel a bit confused here…

3.

I also heard that big companies use different frequencies to get certain sound signature. Is it just a yellow button?

4.

2x TWTMC-DRIXO-SF (the board)

5.6448 / 12.2880 SC-cut

TWTMC-DBM-SF (doubler )

TWTMC-STS-SX OR DX (yet do define)

TWRPS-pp to power everything

Do I miss something?

Will I be able to get some stuff in January or it is better to take options now as the new GB is unknown?

Thanks a lot!

1) To get 22/24 MHz the New Driscoll oscillator TWTMC-DRIXO with crystals at 5/6 MHz followed by a couple of frequency doublers TWTMC-DBM is the best option but also the most expensive. The New Driscoll oscillator TWTMC-DRIXO with crystals at 11/12 MHz followed by one frequency doubler TWTMC-DBM is very close. The New Driscoll oscillator TWTMC-DRIXO with crystals at 22/24 MHz without any frequency doubler is the cheapest option and performs very well (-130dBc at 10Hz from the carrier while the Crystek for example is -97dBc)

2) It's true that different kind of DAC are sensitive to different clock signals, but this has not much to do with the oscillators, the XOs are the base timing devices but the clock signals for the DAC are generated via the front-end (or a FIFO). For example with our new FIFO Lite (as soon as it will be ready) you can play 176/192 KHz materials with the TDA1541A using 5/6 MHz master clock (the best oscillators available) and the WCLK (the most crucial signal for this DAC) is generated outside the FPGA logic, it comes directly from the master clock. The Sabre is another thing, it should be sensitive to the MCLK but I have not yet understood if you can disable the DPLL that could vanish the performance of the XOs.

3) You could try different frequencies, I cannot say about the results, but of course it becomes very very expensive.

4) The items you have listed are right, I believe the choice is between XOs at base frequencies (22/24 MHz) and XOs at lower frequencies (5/6 or 11/12 MHz) followed by one or two doublers.

I would close the GB as soon as possible, next week I will start collecting the payments.

2) It's true that different kind of DAC are sensitive to different clock signals, but this has not much to do with the oscillators, the XOs are the base timing devices but the clock signals for the DAC are generated via the front-end (or a FIFO). For example with our new FIFO Lite (as soon as it will be ready) you can play 176/192 KHz materials with the TDA1541A using 5/6 MHz master clock (the best oscillators available) and the WCLK (the most crucial signal for this DAC) is generated outside the FPGA logic, it comes directly from the master clock. The Sabre is another thing, it should be sensitive to the MCLK but I have not yet understood if you can disable the DPLL that could vanish the performance of the XOs.

3) You could try different frequencies, I cannot say about the results, but of course it becomes very very expensive.

4) The items you have listed are right, I believe the choice is between XOs at base frequencies (22/24 MHz) and XOs at lower frequencies (5/6 or 11/12 MHz) followed by one or two doublers.

I would close the GB as soon as possible, next week I will start collecting the payments.

With AC family CMOS synchronous binary counter in the FIFO Lite while for the top version we are experimenting several ways for the best phase noise performance (ECL, regenerative dividers and mixed topology).

But the most important key is that the WCLK is well isolated from the crap coming from the FPGA logic, this avoids crosstalk and any other modulation between clock signals.

But the most important key is that the WCLK is well isolated from the crap coming from the FPGA logic, this avoids crosstalk and any other modulation between clock signals.

...For example with our new FIFO Lite (as soon as it will be ready) you can play 176/192 KHz materials with the TDA1541A using 5/6 MHz master clock ...

Hello Andrea,

will it be possible to play 352/384 kHz with your FIFO at 11/12MHz master clock (question relates to TDA1541A) as well? Thanks!

Thanks for answers! Another question relates to input data format. Right now I am using Ian's fifopi and experiencing problems with 11 MHz clock - it does not accept my I2S 32fs (16+16 bit) for the 352.8kHz stream as it needs 22MHz of master clock instead.

Just curious will the I2S_32fs be OK input format instead of (as which fifopi wants) 64fs for your FIFO project? Thank you!

Just curious will the I2S_32fs be OK input format instead of (as which fifopi wants) 64fs for your FIFO project? Thank you!

The inputs and the outputs of the FIFO Lite are different time domains and then there is no restriction.

The input accepts I2S with any bit depth from 16 up to 32 bit with sample rate from 44.1 up to 384 kHz.

The output sample rate depends on the master clock frequency, on the format (I2S or PCM) and on the bit depth (16 to 24 bit).

I will publish a table with the supported outputs.

The input accepts I2S with any bit depth from 16 up to 32 bit with sample rate from 44.1 up to 384 kHz.

The output sample rate depends on the master clock frequency, on the format (I2S or PCM) and on the bit depth (16 to 24 bit).

I will publish a table with the supported outputs.

TWTMC-STS-FSDO

The new double sine to square converter with fanout and switched output is ready, pictures attached.

The first board is the TWTMC-STS-FSDO-F, it has 2 inputs, one for each sample rate family (sine wave or CMOS) and 4 outputs, 2 for each sample rate family.

The second board is the TWTMC-STS-FSDO-S, it has 2 inputs, one for each sample rate family (sine wave or CMOS) and 2 switched outputs between the two sample rate families.

The new double sine to square converter with fanout and switched output is ready, pictures attached.

The first board is the TWTMC-STS-FSDO-F, it has 2 inputs, one for each sample rate family (sine wave or CMOS) and 4 outputs, 2 for each sample rate family.

The second board is the TWTMC-STS-FSDO-S, it has 2 inputs, one for each sample rate family (sine wave or CMOS) and 2 switched outputs between the two sample rate families.

Attachments

The new double sine to square converter with fanout and switched output is ready, pictures attached.

The first board is the TWTMC-STS-FSDO-F, it has 2 inputs, one for each sample rate family (sine wave or CMOS) and 4 outputs, 2 for each sample rate family.

The second board is the TWTMC-STS-FSDO-S, it has 2 inputs, one for each sample rate family (sine wave or CMOS) and 2 switched outputs between the two sample rate families.

Can the One TWTMC-STS-FSDO-F 2 inputs be connected to 2 TWTMC-PXO-AIO with the AT 6.25MHz, so each output 2x 25MHz, totally 2x2=4 25MHz outputs?

Is a TWTMC-STS-FSDO-F much better than a TWTMC-STS-SX?

Is the TWTMC-PXO-AIO with the AT 6.25MHz crystal, better than

a TWTMC-DRIXO-SF with the 25.000 MHz SC-cut crystal?

Ask because the Drixo is a little bit cheaper and It`s looked like that Us there need the 25MHz frequence, just have to choose one of these two(drixo or AIO), so the MOQ 10 hopefully can be reach.

Yes, you can connect 2 x TWTMC-PXO-AIO with the AT 6.25MHz to one TWTMC-STS-FSDO-F so the output is 25MHz x 4.

The TWTMC-STS-FSDO theoretically has better phase noise than the TWTMC-STS, at least from the plots in the datasheet of the LTC6957. We will measure it soon.

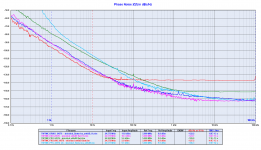

The comparison plots I have published seem to confirm that the TWTMC-PXO-AIO is around 5 dBc better than the Driscoll at the same output frequency (see the attached plot at 24.576 MHz, very close to 24 and 25 MHz).

The TWTMC-STS-FSDO theoretically has better phase noise than the TWTMC-STS, at least from the plots in the datasheet of the LTC6957. We will measure it soon.

The comparison plots I have published seem to confirm that the TWTMC-PXO-AIO is around 5 dBc better than the Driscoll at the same output frequency (see the attached plot at 24.576 MHz, very close to 24 and 25 MHz).

Attachments

Thanks, great.

I will then ordre 2 x TWTMC-PXO-AIO with the AT 6.25MHz, 2x AIO XO transformer kits and 1 TWTMC-STS-FSDO-F to my 4 Buffalo BS-GS2016. I will send the TWTMC OrderForm to You and hope someone do the same, so the MOQ at the AT6.25MHZ, AIO XO transformerkit and TWTMC-PXO-AIO can be reach...

I will then ordre 2 x TWTMC-PXO-AIO with the AT 6.25MHz, 2x AIO XO transformer kits and 1 TWTMC-STS-FSDO-F to my 4 Buffalo BS-GS2016. I will send the TWTMC OrderForm to You and hope someone do the same, so the MOQ at the AT6.25MHZ, AIO XO transformerkit and TWTMC-PXO-AIO can be reach...

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Line Level

- The Well Tempered Master Clock - Building a low phase noise/jitter crystal oscillator