Ok, what is the Problem?

Power supplies are important -- what do you propose to use? Batteries? May not be practical

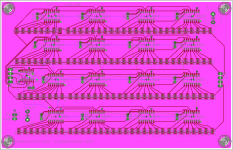

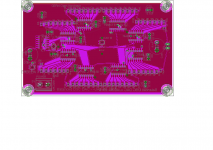

here the different schematics:

- 8-bit tap (8x 15k),

- discrete I/V-converter (500R; +2.5V bias --> thanks Patrick),

- and the two Sallen-Key filter (94kHz and 166kHz).

Do I forget something, I mean principally, coupling capacitors? Open for sinnfull modifications...

Jean-Paul

- 8-bit tap (8x 15k),

- discrete I/V-converter (500R; +2.5V bias --> thanks Patrick),

- and the two Sallen-Key filter (94kHz and 166kHz).

Do I forget something, I mean principally, coupling capacitors? Open for sinnfull modifications...

Jean-Paul

Attachments

here the different schematics:

- 8-bit tap (8x 15k),

- discrete I/V-converter (500R; +2.5V bias --> thanks Patrick),

- and the two Sallen-Key filter (94kHz and 166kHz).

Do I forget something, I mean principally, coupling capacitors? Open for sinnfull modifications...

Jean-Paul

I very much like the approach. For the Sallen Key filters, I am inclined to go with a B1 buffer as the basis -- not too different from what you have, really very close. I am suggesting this because this already exists, essentially but with diifferent values, as the B-4 active crossover.

Now interestingly, both of these can readily be made balanced as the SEN, so from the point of view of what DSC2 might look like, and assuming we use this approach for the discrete IV and filters, what would the digital input look like? ... would it be as simple as placing an inverter on the DSD input line?

Hello,

I reiterate my question about coupling between the different stages to know if I can go completly DC and only place a coupling cap at the output of the last Sallen-Key filter?

I´ve asking Patrick (EUVL) for helping to built a last version of his simplistic OPAMP to use as output buffer.

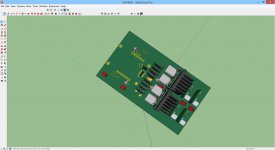

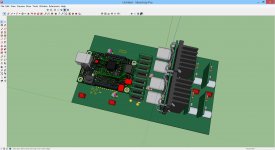

JLSOUNDS give me 3D datas for the I2SOVERUSB converter: I´m working on some missing components but the results are today quiet good, please see the attachment...

Jean-Paul

I reiterate my question about coupling between the different stages to know if I can go completly DC and only place a coupling cap at the output of the last Sallen-Key filter?

I´ve asking Patrick (EUVL) for helping to built a last version of his simplistic OPAMP to use as output buffer.

JLSOUNDS give me 3D datas for the I2SOVERUSB converter: I´m working on some missing components but the results are today quiet good, please see the attachment...

Jean-Paul

Attachments

ARM/FPGA SFP optical input, I2S output NAA

I've been looking at SFP input and I2S output with networkaudiod running on a low powered CPU. sm31 pointed this out: Optical Network Configurations - Page 16

This product will use the Xilinx 7010/7020: krtkl

So a driver would need to be written/modified to get I2S output on the pins ... doable?

I am thinking this would be a terrific platform to create a direct Ethernet input for the "DSC2".

I've been looking at SFP input and I2S output with networkaudiod running on a low powered CPU. sm31 pointed this out: Optical Network Configurations - Page 16

This product will use the Xilinx 7010/7020: krtkl

So a driver would need to be written/modified to get I2S output on the pins ... doable?

I am thinking this would be a terrific platform to create a direct Ethernet input for the "DSC2".

Balanced DSC

So balanced DSC is as easy as:

View attachment DSC1b.pdf

And then dual I-V Sen and filters.

So balanced DSC is as easy as:

View attachment DSC1b.pdf

And then dual I-V Sen and filters.

Not just transformer I'm thinking relays to switch between discrete SK filter eg B1 buffer based vs. M2 "enhanced" transformer -- the M2 sounds so good in real life that it might be a good option, but it would be good to be able to test side by side

I'm thinking relays to switch between discrete SK filter eg B1 buffer based vs. M2 "enhanced" transformer -- the M2 sounds so good in real life that it might be a good option, but it would be good to be able to test side by side

Sent from my iPhone using Tapatalk

Sent from my iPhone using Tapatalk

- Home

- Source & Line

- Digital Line Level

- Signalyst DSC1