I2S Left-first or Right-first

A Japanese DAC designer recently pointed out a peculiar I2S signal requirement in the case of ES9018 DAC chip.

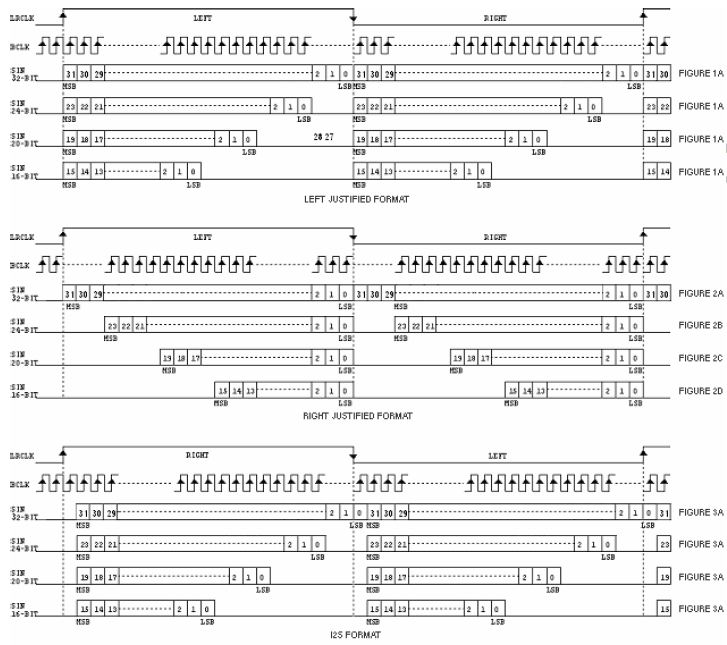

According to a diagram in its datasheet, ES9018 requires a serial data in "Right-first" way while the original specification document of I2S and the most of other DAC chips require a "Left-first" way format.

As a result, he says a L-R data pair of the same sampling timing which complies with a standard I2S format will be output in two different timings.

Has anyone confirmed this issue?

A Japanese DAC designer recently pointed out a peculiar I2S signal requirement in the case of ES9018 DAC chip.

According to a diagram in its datasheet, ES9018 requires a serial data in "Right-first" way while the original specification document of I2S and the most of other DAC chips require a "Left-first" way format.

As a result, he says a L-R data pair of the same sampling timing which complies with a standard I2S format will be output in two different timings.

Has anyone confirmed this issue?

A Japanese DAC designer recently pointed out a peculiar I2S signal requirement in the case of ES9018 DAC chip.

According to a diagram in its datasheet, ES9018 requires a serial data in "Right-first" way while the original specification document of I2S and the most of other DAC chips require a "Left-first" way format.

As a result, he says a L-R data pair of the same sampling timing which complies with a standard I2S format will be output in two different timings.

Has anyone confirmed this issue?

There are 6 different PCM formats that ES9018 can accept, according to its datasheet. If you use left-justified MSB-first mode (mode 0) then it's a normal left-right arrangement.

If you use left-justified MSB-first mode (mode 0) then it's a normal left-right arrangement.

Hi, Promixe,

Thank you very much for your immediate reply!

I wanted to know how we could deal with a standard "left-first" I2S format.

May I ask you the following two points?

1. Have you considered the well-known MSB timing difference between Left-justified and I2S?

2. Have you applied the possible work-around you proposed to a standard I2S signal actually?

Bunpei

You're right, LJ mode wouldn't work with I2S data input. But if you look at the above picture, the way I interpret it, the I2S data is perpetual, therefore it doesn't matter which particular channel goes first. If LRCLK is LOW at any given point in time it is then Left channel, if it's HIGH then it's the Right channel.

If you ask me, it seems that confusion is due to someone making drawing for the ES9018 datasheet not taking its time to invert the LRCLK drawing, but simply copy-pasting the graphic from Left/Right Justified figures above it and renaming the logic level captions in accordance with the I2S standard. =)))

Another question would be - why the hell ESS would go through the trouble of modifying I2S protocol when their chip is primarily targeted at consumer applications with nothing but standard I2S expected at its input? =)

PS: A bit off-topic, but have you started any work with the AT1201's yet?

Hi, Promixe,

Thank you very much for your immediate reply!

I wanted to know how we could deal with a standard "left-first" I2S format.

May I ask you the following two points?

1. Have you considered the well-known MSB timing difference between Left-justified and I2S?

2. Have you applied the possible work-around you proposed to a standard I2S signal actually?

Bunpei

I agree with you. I am going to check an actual output for a standard I2S input.Another question would be - why the hell ESS would go through the trouble of modifying I2S protocol when their chip is primarily targeted at consumer applications with nothing but standard I2S expected at its input? =)

I forwarded those chips to my friend in Japan who can design a prototyping board for the ADC and an associated recorder. I have not received his update yet. But, I will keep in touch with you!PS: A bit off-topic, but have you started any work with the AT1201's yet?

I'm testing with two sources: a common DVD player and a PC's on-board sound.

I also have a Behringer SRC2496, perhaps I should try with that as well, since it supports a number of output options.

I can confirm that with the Behringer as s/pdif source and configured for aes/ebu output, the register that displays operating mode switches from consumer (0) to professional (1) and the other relevant registers actually give meaningful info (sampling rate & word length). So that is solved.

I agree with you. I am going to check an actual output for a standard I2S input.

I forwarded those chips to my friend in Japan who can design a prototyping board for the ADC and an associated recorder. I have not received his update yet. But, I will keep in touch with you!

so it was you!!

hehe, I procrastinated about buying them due to the non-existent support from the company for any kind of prototyping etc, but came back to buy them anyway and they were gone!!

hehe, I procrastinated about buying them due to the non-existent support from the company for any kind of prototyping etc, but came back to buy them anyway and they were gone!!

Isn't it a nice thing for you that you need to take no risk on developing a board for the LSI? When we have a good result, we will offer an evaluation opportunity to acko & you.

By the way, I made my experiments and found ES9018 can play DSD256 and DSD512 also. AT1201 is one of a few ADC devices that may provide DSD256 output.

yes, but the company has been disolved, so to buy these chips will not be easy. its possible that profusion has stock, but they also said they had stock of the semelab lateral mosfets all the way through the period where they had none. I suppose I can email and ask if they are real

yep, as I thought, I just loaded some in my cart and its out of stock, so they are not available anywhere, you may have the last ones. looks like i'll go with the ESS, I wanted to try something else, but I suppose the ESS ADC is best for ESS DAC interface, but no DSD

so in answer to your question, no i'm not glad someone else is taking the risk for R&D. i'm mad at the corporate company that bought them up and stopped their products from getting to market for diy, not you... its my fault for hesitating, at the time i thought it was possible i could get some elsewhere, but that has since proven impossible. I hate thesde companies like profusionplc and farnell/element14 that list products they dont actually have and dont show you till youve decided you want to buy them

so in answer to your question, no i'm not glad someone else is taking the risk for R&D. i'm mad at the corporate company that bought them up and stopped their products from getting to market for diy, not you... its my fault for hesitating, at the time i thought it was possible i could get some elsewhere, but that has since proven impossible. I hate thesde companies like profusionplc and farnell/element14 that list products they dont actually have and dont show you till youve decided you want to buy them

Attachments

Last edited:

According to "FUNCTIONAL BLOCK DIAGRAM" in data sheet of ES9018, DSD signal is processed in "OVERSAMPLING FILTER" block.

1. My interpretation is "no oversampling is applied to DSD data signals in this block".

Do you think it is correct?

I am trying DSD plays these days. I found my previous guess was wrong.

When we play DSD sources, we must use OSF.

I understand the OSF converts 1 bit stream into 6 bit Delta-Sigma modulation format that is acceptable by a DAC segment.

By the way, I made my experiments and found ES9018 can play DSD256 and DSD512 also. AT1201 is one of a few ADC devices that may provide DSD256 output.

What do you mean DSD256 and DSD512? As far as I'm aware there are only two DSD formats available at this time DSD64Fs and DSD128Fs with sampling rate of 2.8224 MHz and 5.6444 MHz accordingly with equivalent data rates.

Last edited:

Hi, AndriyOL,

As you pointed out, the term neither "DSD256" nor "DSD512" is a formal one. However, I found them in the following pages;

Impulse response: analog, PCM and DSD

http://www.diyaudio.com/forums/exadevices/183374-exau2i-multi-channel-asynchronous-usb-i2s-interface-64.html#post2641612

Bunpei

As you pointed out, the term neither "DSD256" nor "DSD512" is a formal one. However, I found them in the following pages;

Impulse response: analog, PCM and DSD

http://www.diyaudio.com/forums/exadevices/183374-exau2i-multi-channel-asynchronous-usb-i2s-interface-64.html#post2641612

Bunpei

I am recently concentrating in playing upsampled DSD256 sources on ES9018 DACs.

Totally six SDTrans384 users in Japan those who connected their players to their own ES9018-based DACs made their independent experiments on the play of DSD256 upsampled sources and they reported they felt a break through excellence in the played music of the upsampled sources.

I am really surprised with superior potentiality of the DAC chip Dustine and his co-workers in ESS Tech produced.

Totally six SDTrans384 users in Japan those who connected their players to their own ES9018-based DACs made their independent experiments on the play of DSD256 upsampled sources and they reported they felt a break through excellence in the played music of the upsampled sources.

I am really surprised with superior potentiality of the DAC chip Dustine and his co-workers in ESS Tech produced.

Three tips to exploit potential performance of ES9018

These three tips are based on my and co-workers' actual experiences.

1. Providing synchronous master clock of 90.3168 MHz(for 44.1kHz series) or 98.304 MHz(for 48kHz series) for I2S/DSD

2. Applying a high-quality AVCC power supply as much as possible

The type of bypass capacitors included there may effect severely.

3. Playing DSD256 upsampled sources

Even if your original sources are of lower sampling frequencies of PCM or DSD, DSD converted and upsampled DSD256 sources sound better.

These three tips are based on my and co-workers' actual experiences.

1. Providing synchronous master clock of 90.3168 MHz(for 44.1kHz series) or 98.304 MHz(for 48kHz series) for I2S/DSD

2. Applying a high-quality AVCC power supply as much as possible

The type of bypass capacitors included there may effect severely.

3. Playing DSD256 upsampled sources

Even if your original sources are of lower sampling frequencies of PCM or DSD, DSD converted and upsampled DSD256 sources sound better.

>1. Providing synchronous master clock of 90.3168 MHz(for 44.1kHz series) or 98.304 MHz(for 48kHz series) for I2S/DSD

Is the 90MHz/98MHz clock frequency prior to phase noise performance?

>2. Applying a high-quality AVCC power supply as much as possible

The type of bypass capacitors included there may effect severely.

From my experience, Isolation between AVCC_L and AVCC_R makes impact on channel separation.

1.2v VDD ( or 1.2v analogue VDD, maybe ) also seems to be critical.

Is the 90MHz/98MHz clock frequency prior to phase noise performance?

>2. Applying a high-quality AVCC power supply as much as possible

The type of bypass capacitors included there may effect severely.

From my experience, Isolation between AVCC_L and AVCC_R makes impact on channel separation.

1.2v VDD ( or 1.2v analogue VDD, maybe ) also seems to be critical.

>1. Providing synchronous master clock of 90.3168 MHz(for 44.1kHz series) or 98.304 MHz(for 48kHz series) for I2S/DSD

Is the 90MHz/98MHz clock frequency prior to phase noise performance?

Hi, wktk_smile,

I am afraid that I can't understand your question literally.

Therefore, I guess what your question means.

As you may think, the master clock used should have a good phase noise profile in principle.

If you don't need "OSF mode ON" for DXD, you can use a master clock of lower frequencies.

Bunpei

As you may think, the master clock used should have a good phase noise profile in principle.

If you don't need "OSF mode ON" for DXD, you can use a master clock of lower frequencies.

Bunpei

Thanks for clarification.

I have been listened various upsampled dsd256 sources these days - using SDtrans384 and ES9018 BuffaloII DAC.

Many of those dsd souces gives better textures and extended sound stage deapth.

When converted/upsampled from 16bit/44.1k pcm, sometimes I also got unignorable unnatural

emphasis in certain frequencies alng with above mentioned improvements.

I wonder it might be a difficult task for the conversion software to convert such "non - hirez files" to DSD.

... Many of those dsd souces gives better textures and extended sound stage deapth.

When converted/upsampled from 16bit/44.1k pcm, sometimes I also got unignorable unnatural emphasis in certain frequencies alng with above mentioned improvements.

I wonder it might be a difficult task for the conversion software to convert such "non - hirez files" to DSD.

I completely agree with you.

Oh, we have introduced one more unintended and complicated parameter set into DSD plays!

Bunpei

- Home

- Source & Line

- Digital Line Level

- ESS Sabre Reference DAC (8-channel)