Unfortunately Rl=0 is the solution, this means that in this topology, at 20 kHz signal and 250 kHz PWM freq 10% accuracy is barely reachable on low load impedance, and can not be reached on high impedance.

But as soon as we add an I control channel, G is increased:

G(s)=RP*Gpwm/(L*s+Rl)+1/(Ti*s)

By setting Ti=L/Rl we got an ideal integrating controller, that works exactly with the required 10 % accuracy at 20 kHz, which is a good thing, but for what load value should we do this?

Without ruining almost everything else we can optimize it for 25 ohm. At higher Rl, the error will increase further.

But at higher fpwm the situation would be better! For example at 500 kHz RP=2ohm is OK, and Rl=50 ohm can be selected for Ti optimisation.

Further gain increasement can be done with introducing a second PWM modulator with opposite phase, tied to an other inductor connected to output. L can be doubled, this leads to slower current slope, RP can be doubled again. Now you are at Rl=100 ohm.

Every doubling the number of PWMs (operating at evenly distributed phase) doubles maximal Rl.

At the same time output ripple current also drops to half at each step. (Originally it was quite high!)

Maybe this is not the most effective control method, but it is easy to design and provides rubustness. It can operate more stable with somewhat reactive, variable impedances than a highly optimized control method.

At the last step you may insert a small capacitor parallel to output to boost gain and phase a little at the highest load resistance, and to filter ripple.

But as soon as we add an I control channel, G is increased:

G(s)=RP*Gpwm/(L*s+Rl)+1/(Ti*s)

By setting Ti=L/Rl we got an ideal integrating controller, that works exactly with the required 10 % accuracy at 20 kHz, which is a good thing, but for what load value should we do this?

Without ruining almost everything else we can optimize it for 25 ohm. At higher Rl, the error will increase further.

But at higher fpwm the situation would be better! For example at 500 kHz RP=2ohm is OK, and Rl=50 ohm can be selected for Ti optimisation.

Further gain increasement can be done with introducing a second PWM modulator with opposite phase, tied to an other inductor connected to output. L can be doubled, this leads to slower current slope, RP can be doubled again. Now you are at Rl=100 ohm.

Every doubling the number of PWMs (operating at evenly distributed phase) doubles maximal Rl.

At the same time output ripple current also drops to half at each step. (Originally it was quite high!)

Maybe this is not the most effective control method, but it is easy to design and provides rubustness. It can operate more stable with somewhat reactive, variable impedances than a highly optimized control method.

At the last step you may insert a small capacitor parallel to output to boost gain and phase a little at the highest load resistance, and to filter ripple.

Thank you for big explanation.... I'm working with software for closed loop system. I'll share with you my design as soon as I can get a reasonable results.

Youre welcome!

If you use software, then you can set PI controller parameters adaptively, which is a great benefit. But will your systems latency be much lower then 6 us? Because otherwise phase shift can cause instability.

Youre welcome!

If you use software, then you can set PI controller parameters adaptively, which is a great benefit. But will your systems latency be much lower then 6 us? Because otherwise phase shift can cause instability.

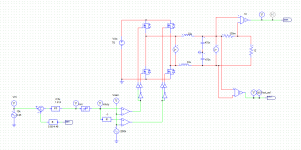

I want to share with you my design

As you can see i've to use a full bridge configuration because i need higher dynamic.

The current loop is ok from 12Ohm to 1Ohm.

Now i want, if possible, to close the voltage loop in order to mantain a stable voltage also in high impedance. It is difficult to mantainig stability with voltage feedbck and another PI controller cascaded to the "current" one.

If you could take a look to my design let me know your ideas...

Thanks

P.S. Last question: do you think is it better an analog feedback loop or implementing it with AtoD and FPGA?

I want to share with you my design

View attachment 596450

As you can see i've to use a full bridge configuration because i need higher dynamic.

You can achieve the same dynamic with single sided output and double power supply voltage, but there are some benefits of the full bridge, I used it also in some of my similar projects because the lack of supply pumping and lower rail voltage. But prepare yourself to the difficulty of current sensing on an output!

BTW: for low power (3 A 20 V) but high precision I chose ClassAB. It was fast enough to reveal the quantization and sampling error of the stimuli generator, so later I had to built a filter for the input signal generator.

You need PID to control well a 2nd order LPF. And its better to design inner (voltage) loop first, and then apply the second, current loop. But you can always find a load impedance that cause instability in this topology.The current loop is ok from 12Ohm to 1Ohm.

Now i want, if possible, to close the voltage loop in order to mantain a stable voltage also in high impedance. It is difficult to mantainig stability with voltage feedbck and another PI controller cascaded to the "current" one.

If you could take a look to my design let me know your ideas...

Thanks

P.S. Last question: do you think is it better an analog feedback loop or implementing it with AtoD and FPGA?

If you implement a simple constant feedback, then digital realisation has more drawback than benefit. But if you can figure out an adaptive control method, especially if stimulus is generated by the same digital system, therefore you can optimize control to the actual frequency, then digital realisation can be better than analog.

In my current generators there was a potentiometer for setting loop gain, scaled in load impedance, and it had to set by operator to the lowest impedance the output will see.

You need PID to control well a 2nd order LPF. And its better to design inner (voltage) loop first, and then apply the second, current loop. But you can always find a load impedance that cause instability in this topology.

Why PID?

Another question: do you know any IC (pwm controller) that could be used for my application?

Thanks.

Why PID?

Another question: do you know any IC (pwm controller) that could be used for my application?

Thanks.

Well, there are complete PWM amplifier ICs, also with BD modulation (like in your schematic). I usually build a triangle generator and use comparators as PWM. If I remember correctly there must be a TDA... PWM IC, but I never interested much.

PID, because an LC LPF has almost 180 degree phaseshift at high freq. Together with the PI controllers phase this leads to oscillation. D channel helps to reduce this. Optimally 90 degree should be the goal at cutoff freq of the whole loop.

PID, because an LC LPF has almost 180 degree phaseshift at high freq. Together with the PI controllers phase this leads to oscillation. D channel helps to reduce this. Optimally 90 degree should be the goal at cutoff freq of the whole loop.

So it is better to feedback the voltage/current before the filter or almost after the inductor. Is it right?

Today i noticed that generating the pwm signal with my fpga (open loop) at the output of the class d amplifier there is a dc offset greater than 1Volt (mean measure with oscilloscope).

How could it is possible?

In the FPGA an NCO generates a 10 bit discrete sinusoid (-511,+511). All the samples are scaled in order to compare it to triangle wave (-125,+124). Dead times are added on resulting pwm.

Seems that the dc offset is more significative for duty cycle greater than 50%.

Have you any idea? Things could be better with an IC and closing the loop?

Let me know.

So it is better to feedback the voltage/current before the filter or almost after the inductor. Is it right?

I don't know what you mean. Voltage and current feedback are 2 different quantities, for both there are different options, but voltage is on a node, while current is on a branch so they can't be defined the same way. "Almost after..." ?

For voltage the most important point of feedback is definitely on the output of LC filter. Voltage of switching node is not important, basically it is determined directly by PWM signal. But for current you have 2 options: current of inductor or current of load. Both has its purpose.

I can't tell which is the truely best combination (linear combination) of the feedback for the 3 state variables and the filter parameters, the optimalization for so many parameters in head is beyond my capabilities.

Today i noticed that generating the pwm signal with my fpga (open loop) at the output of the class d amplifier there is a dc offset greater than 1Volt (mean measure with oscilloscope).

How could it is possible?

In the FPGA an NCO generates a 10 bit discrete sinusoid (-511,+511). All the samples are scaled in order to compare it to triangle wave (-125,+124). Dead times are added on resulting pwm.

Offset of what signal? Differential output voltage of the bridge? Or common mode voltage? Or you don't have full bridge yet? What is your topology currently?

How much dead time, and exactly how? If you insert it asymmetrically, then it will cause offset naturally.

Seems that the dc offset is more significative for duty cycle greater than 50%.

Have you any idea? Things could be better with an IC and closing the loop?

Let me know.

Of course offset will be lower in closed loop. I don't know what kind of IC you think of.

Why PID?

Another question: do you know any IC (pwm controller) that could be used for my application?

Thanks.

PID? wel just read this paper, and use capacitor current feedback, but also need a voltage feedback also to get good results, as for what we know now afcourse.. PID is used here to rule out the two low pass poles of output filter. A good reading for learning new things.

https://pure.tue.nl/ws/files/46824541/573760-1.pdf

I like currrent feedback because of the bandwidth and low tim, dislike the offset problems and need a servo, for class d things are different.

regards.

Thank you. The paper seems very interesting.PID? wel just read this paper, and use capacitor current feedback, but also need a voltage feedback also to get good results, as for what we know now afcourse.. PID is used here to rule out the two low pass poles of output filter. A good reading for learning new things.

https://pure.tue.nl/ws/files/46824541/573760-1.pdf

I like currrent feedback because of the bandwidth and low tim, dislike the offset problems and need a servo, for class d things are different.

regards.

Thank you. The paper seems very interesting.

Your welcome.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Class D

- class d amplifier current output