Hey Guys,

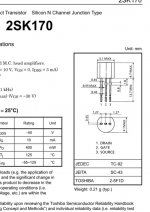

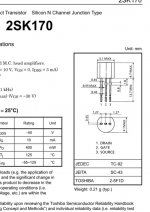

I'm looking to build a pre and I'm unclear on the toshiba datasheet pins for JFET 2sk170 BL/GR

Is the attached datasheet showing the flat section of JFET facing you or round?

If flat is facing you is it Pin 1 drain or pin 3 source??

Hard to tell from pic, appreciated if someone could confirm

Thanks heaps

I'm looking to build a pre and I'm unclear on the toshiba datasheet pins for JFET 2sk170 BL/GR

Is the attached datasheet showing the flat section of JFET facing you or round?

If flat is facing you is it Pin 1 drain or pin 3 source??

Hard to tell from pic, appreciated if someone could confirm

Thanks heaps

I'm looking to build a pre and I'm unclear on the toshiba datasheet pins for JFET 2sk170 BL/GR

Yes, with the flat facing you. Drain 1, gate 2, source 3.

Yes, with the flat facing you. Drain 1, gate 2, source 3.

Cheers Rayma, it's terrible pic of it hard to tell, also seems to be conflicting info

I'll go with left to right 1. Drain, 2. Gate and 3 source

Last edited:

Cheers Rayma, it's terrible pic of it hard to tell, also seems to be conflicting info

It's a two view orthographic drawing, front and bottom.

First Angle Orthographic Projection

The good thing is, that even if you get it reversed, with a 2sk170 it does not matterThey are symmetric and will work either way around.

Tony.

Hey Tony,

Yeh I had heard that to be case but wasn't sure as it seems to be differing views based on capacitance causing issues wasn't sure if those views were JFETs generally or specifically relating to 2sk170s

Or if it was based on application for which the JFET is used.

the drawing is standard as explained in the next post.Cheers Rayma, it's terrible pic of it hard to tell, also seems to be conflicting info

I'll go with left to right 1. Drain, 2. Gate and 3 source

the drawing is standard as explained in the next post.

I was never good with IKEA flat packs either

The nice thing about a DGS pin out is that it makes it easy to test Idss.

The gate of a jFET is not susceptible to damage from stray electrostatic voltage, so you can touch the leads outs in any order without having to be concerned about damage.

Attach a croc lead to the -ve terminal of your 10Vdc supply.

Attach the other croc lead to the +ve of your 10Vdc suppy.

Clip the negative crocodile clip across the two G & S pins.

Clip the positive lead to the D pin.

The jFET now passes Idss until it warms up above 25°C

If you add in a monitoring resistor that drops 100mV at the Idss, then by setting your supply to 100mV above the 10Vds required for the Idss test, you can read off the current, i.e. set the Supply to 10.1Vdc and the jFET will see 10V across it's D & S pins when the Vdrop across the monitoring resistor uses up the 100mV of excess voltage.

a 10r resistor passing an Idss of 10mA drops 100mV. If the Idss is 12mA then you will see a 120mV drop. You turn the supply up to 10V+120mV = 10.12Vdc and take the cold current reading. Thats is a pretty close approximation to Idss. As the jFET heats up, the current increases to an Id value that is higher than Idss.

The gate of a jFET is not susceptible to damage from stray electrostatic voltage, so you can touch the leads outs in any order without having to be concerned about damage.

Attach a croc lead to the -ve terminal of your 10Vdc supply.

Attach the other croc lead to the +ve of your 10Vdc suppy.

Clip the negative crocodile clip across the two G & S pins.

Clip the positive lead to the D pin.

The jFET now passes Idss until it warms up above 25°C

If you add in a monitoring resistor that drops 100mV at the Idss, then by setting your supply to 100mV above the 10Vds required for the Idss test, you can read off the current, i.e. set the Supply to 10.1Vdc and the jFET will see 10V across it's D & S pins when the Vdrop across the monitoring resistor uses up the 100mV of excess voltage.

a 10r resistor passing an Idss of 10mA drops 100mV. If the Idss is 12mA then you will see a 120mV drop. You turn the supply up to 10V+120mV = 10.12Vdc and take the cold current reading. Thats is a pretty close approximation to Idss. As the jFET heats up, the current increases to an Id value that is higher than Idss.

Last edited:

In my limited experience I have found IKEA's pictorial instructions to be among the best in the industry.I was never good with IKEA flat packs either

The nice thing about a DGS pin out is that it makes it easy to test Idss.

The gate of a jFET is not susceptible to damage from stray electrostatic voltage, so you can touch the leads outs in any order without having to be concerned about damage.

Attach a croc lead to the -ve terminal of your 10Vdc supply.

Attach the other croc lead to the +ve of your 10Vdc suppy.

Clip the negative crocodile clip across the two G & S pins.

Clip the positive lead to the D pin.

The jFET now passes Idss until it warms up above 25°C

If you add in a monitoring resistor that drops 100mV at the Idss, then by setting your supply to 100mV above the 10Vds required for the Idss test, you can read off the current, i.e. set the Supply to 10.1Vdc and the jFET will see 10V across it's D & S pins when the Vdrop across the monitoring resistor uses up the 100mV of excess voltage.

a 10r resistor passing an Idss of 10mA drops 100mV. If the Idss is 12mA then you will see a 120mV drop. You turn the supply up to 10V+120mV = 10.12Vdc and take the cold current reading. Thats is a pretty close approximation to Idss. As the jFET heats up, the current increases to an Id value that is higher than Idss.

Thanks for info Andrew appreciated handy to know for roughly matching them

In my limited experience I have found IKEA's pictorial instructions to be among the best in the industry.

Which says a lot about my spatial awareness

You mean school as in, school? Haha, that's a good one. Yours truly managed to get through 20 years worth of eduction without once being explicitly taught stuff about technical drawings, though you do pick up a few basic things here and there. Nope, never had anything to do with mechanical engineering up until the point where I was confronted with CAD / PCB layout apps (10th semester or so at uni?).

In any case, pictorials are all good and well, but usually would be about 1000 times more effective with some textual description to go with them - but companies are too cheap for having those translated into a gazillion languages. Recently I was fighting with the drawings for installing photoconductor units in a Lexmark colour laser. Basically it's dead easy once you know how it's done, but the drawing was (a) printed way too small and (b) not clear in what it was pointing at.

OK, enough OT for now.

In any case, pictorials are all good and well, but usually would be about 1000 times more effective with some textual description to go with them - but companies are too cheap for having those translated into a gazillion languages. Recently I was fighting with the drawings for installing photoconductor units in a Lexmark colour laser. Basically it's dead easy once you know how it's done, but the drawing was (a) printed way too small and (b) not clear in what it was pointing at.

OK, enough OT for now.

You mean school as in, school? Haha, that's a good one. Yours truly managed to get through 20 years worth of eduction without once being explicitly taught stuff about technical drawings.

All of the freshman engineering students were required to take a full semester of engineering drawing at my university.

UK does it differently.

I started technical drawing at 14 so that I could take the two year course and the exam before leaving school at 16. But I stayed on to take the Higher grade exams.

At university we did not do a specific Drawing class. But drawing was a big part of two first year subjects.

I recall when in industry and our department was starting to get involved with CADrawing, the dept took on two school leavers that had not done any hand drawing and went straight to computerised drawing. They did not know about, nor understand, basic drawing techniques (a simple thing like knowing where tangent points were between two part circles, or even that these points could help them towards a drawing solution). The Engineers had to repeatedly show these two "draughtsmen" how to create the shape that had been sketched for them.

The two did get better, but I never considered them true draughtsmen. The manual draughtsmen and the engineers were all far better at producing drawings that could be handed over to contractors to build the object.

I started technical drawing at 14 so that I could take the two year course and the exam before leaving school at 16. But I stayed on to take the Higher grade exams.

At university we did not do a specific Drawing class. But drawing was a big part of two first year subjects.

I recall when in industry and our department was starting to get involved with CADrawing, the dept took on two school leavers that had not done any hand drawing and went straight to computerised drawing. They did not know about, nor understand, basic drawing techniques (a simple thing like knowing where tangent points were between two part circles, or even that these points could help them towards a drawing solution). The Engineers had to repeatedly show these two "draughtsmen" how to create the shape that had been sketched for them.

The two did get better, but I never considered them true draughtsmen. The manual draughtsmen and the engineers were all far better at producing drawings that could be handed over to contractors to build the object.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Analog Line Level

- Pin Confirmation