Not aware of published perceptual research on that. Possible to demonstrate though. Should be measurable since in the analog domain the perception of L/R location is related to phase stability between channels. You already mentioned how angle changes with timing. If the timing is between channels is noisy then the angle must be blurred across space.

Hard to understand what you replied to....

//

andrea, you are forming your own reality I see. It's hard to debate.

//

No, it's just you.

The backstage coming out from the DAM0121 is far form the reality, but if you like its representation I'm happy for you.

I'm not so happy.

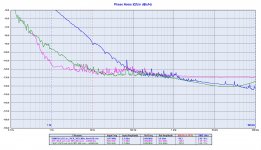

Then this is the measured result: the DAM1021 LRCK is 34dB worse than the RPI LRCK. And the jitter has not been reduced, it has been added as you can clearly see from the plot.

It does not matter?

Well, let me know about your experience and your results.

I'm very curious.

Attachments

Last edited:

"When the only thing you have is a hammer, everything looks like a nail."

Do you seriously think that everything you hear from the DAM is clock driven?

I will refrain for discussing SQ because it's to personal and subjective. What I don't like is that you spread false info about the relation between clock behaviour and analog side impact - with no measurements and obvious a lack of understanding about the relations.

You claim that something was rather added jitter wise - I wont believe that before I see a measurement without changes to the Si - and that wont happen - we both know that - but it doesn't make your claim a fact. It's probably just a guess or wishful hope - right?

I have stated many times that the DAM fifo don't let jitter pass, only wonder - it's technology and its defined by the fifo time constant for changing the clock. That has been shown by zfe measurements - if you don't understand them, ask.

//

Do you seriously think that everything you hear from the DAM is clock driven?

I will refrain for discussing SQ because it's to personal and subjective. What I don't like is that you spread false info about the relation between clock behaviour and analog side impact - with no measurements and obvious a lack of understanding about the relations.

You claim that something was rather added jitter wise - I wont believe that before I see a measurement without changes to the Si - and that wont happen - we both know that - but it doesn't make your claim a fact. It's probably just a guess or wishful hope - right?

I have stated many times that the DAM fifo don't let jitter pass, only wonder - it's technology and its defined by the fifo time constant for changing the clock. That has been shown by zfe measurements - if you don't understand them, ask.

//

"When the only thing you have is a hammer, everything looks like a nail."

Do you seriously think that everything you hear from the DAM is clock driven?

I will refrain for discussing SQ because it's to personal and subjective. What I don't like is that you spread false info about the relation between clock behaviour and analog side impact - with no measurements and obvious a lack of understanding about the relations.

You claim that something was rather added jitter wise - I wont believe that before I see a measurement without changes to the Si - and that wont happen - we both know that - but it doesn't make your claim a fact. It's probably just a guess or wishful hope - right?

I have stated many times that the DAM fifo don't let jitter pass, only wonder - it's technology and its defined by the fifo time constant for changing the clock. That has been shown by zfe measurements - if you don't understand them, ask.

//

I have measured the jitter, it's a fact, there is no reduction while it even increases.

I don't spread any false information.

I believe the front-end of the DAM is not properly designed, this is my opinion.

You don't agree. Well, I'm sorry, that is.

Would you measure the impact of the jitter on the analog side?

Well, buy the gear or build it yourself.

Do you trust the relevance of the long term stability in digital to analog conversion?

Well, you are confused, but it's your problem not mine.

And finally I see you have not yet explain your experiments.

Maybe you have not yet experiment?

I think so.

...and I suspect speaker system would generally distort more than that physically...

Yet, listening tests indicate that speaker distortion is one thing, amplifier distortion is something different and digital distortion is still something else entirely

Narrow minded engineers, insisting that thd measurements reveal all are to blame for this unfortunate confusion.

Reading up on earlier posts I think I'm beginning to grasp -- but correct me if I'm wrong.

The reclocking on the dam isn't really reclocking, rather FIFO with an *adaptive clock*. The Si514/Si570 continuously tracks the input bit clock. First with a fast filter -- obviously to lock on -- then with a slow filter with a 0,1 Hz time constant.

Now for the RPi or any other source without a dedicated XO for sample frequencies, 44,1 kHz in this case, the "adaptive clocking" is continuously shifting as it is tracking the RPi's uneven clock. (This 44,1 kHz RPi output has been documented before -- I think on Archimago's excellent blog.)

So the dam would really benefit from being fed a stable bit clock. (Which is supported by Andrea's findings on source dependence, refer to the 44,1/48 kHz parts.)

Now as the Si514 or Si570 are latching the FIFO buffer, the performance will eventually be limited by those clocks. Meaning that you can select an input clock at or just over the jitter specifications of the Si clocks. Anything better will just be put to waste.

With all this I'm about to pull the trigger on a Kali reclocker to put before my dam1121.

Am I making sense with this?

The reclocking on the dam isn't really reclocking, rather FIFO with an *adaptive clock*. The Si514/Si570 continuously tracks the input bit clock. First with a fast filter -- obviously to lock on -- then with a slow filter with a 0,1 Hz time constant.

Now for the RPi or any other source without a dedicated XO for sample frequencies, 44,1 kHz in this case, the "adaptive clocking" is continuously shifting as it is tracking the RPi's uneven clock. (This 44,1 kHz RPi output has been documented before -- I think on Archimago's excellent blog.)

So the dam would really benefit from being fed a stable bit clock. (Which is supported by Andrea's findings on source dependence, refer to the 44,1/48 kHz parts.)

Now as the Si514 or Si570 are latching the FIFO buffer, the performance will eventually be limited by those clocks. Meaning that you can select an input clock at or just over the jitter specifications of the Si clocks. Anything better will just be put to waste.

With all this I'm about to pull the trigger on a Kali reclocker to put before my dam1121.

Am I making sense with this?

Last edited:

I have measured the jitter, it's a fact, there is no reduction while it even increases.

I don't spread any false information.

I believe the front-end of the DAM is not properly designed, this is my opinion.

You don't agree. Well, I'm sorry, that is.

Would you measure the impact of the jitter on the analog side?

Well, buy the gear or build it yourself.

Do you trust the relevance of the long term stability in digital to analog conversion?

Well, you are confused, but it's your problem not mine.

And finally I see you have not yet explain your experiments.

Maybe you have not yet experiment?

I think so.

You are correct. You can't measure jitter on the analog side of DAC - only on the clock, jitter is defined /Yoda style/ Jitter has impact in analog side and you think-wish that it is "timing" but you really don't seem to have an engineering idea about what happens - you seem to think that it is also timing here, but kind-of different timing.

I own the Ian FIFO since long and have tried with different clocks. I also made mechanical isolation trails.

That's All I Have To Say About That. /Forrest style/

//

You are correct. You can't measure jitter on the analog side of DAC - only on the clock, jitter is defined /Yoda style/ Jitter has impact in analog side and you think-wish that it is "timing" but you really don't seem to have an engineering idea about what happens - you seem to think that it is also timing here, but kind-of different timing.

I own the Ian FIFO since long and have tried with different clocks. I also made mechanical isolation trails.

That's All I Have To Say About That. /Forrest style/

//

You really don't understand.

The timing errors occur during the conversion, when the latch of the 595 is clocked (on the rising edge).

At that time the ladder changes to generate the voltage corresponding to the new digital word (since the DAM is a voltage output DAC).

The jitter causes a timing error in the above transiction so the ladder is updated before or after the predicted time.

Does this generate THD?

Maybe, I dont know and also I don't care.

If you care build your gear and try to measure the THD.

But I think I do. Yes on the latch. I know.

OK - there you go, you admit it in the end - good for you : "Does this generate THD? Maybe, I don't know and also I don't care."

Do you think jitter generates a timing fault in the analog signal? If yes, describe this timing error - what is time shifted and how much - on the analog side - not clock, not registers... - on the analog signal!! What?

//

OK - there you go, you admit it in the end - good for you : "Does this generate THD? Maybe, I don't know and also I don't care."

Do you think jitter generates a timing fault in the analog signal? If yes, describe this timing error - what is time shifted and how much - on the analog side - not clock, not registers... - on the analog signal!! What?

//

Last edited:

But I think I do. Yes on the latch. I know.

OK - there you go, you admit it in the end - good for you : "Does this generate THD? Maybe, I don't know and also I don't care."

Do you think jitter generates a timing fault in the analog signal? If yes, describe this timing error - what is time shifted and how much - on the analog side - not clock, not registers... - on the analog signal!! What?

//

I wrote "maybe", that means I have no evidence of that.

Instead what I have felt every time I have improved the clock was a better space reconstruction.

The speed of sound is a constant, so if the space was altered by the time it's mean "timing error".

Call it as you prefer, I call it "timing error".

I cannot measure this timing error in the same manner you cannot measure the THD related to the jitter.

I can measure the phase noise and the jitter, you cannot measure anything.

You say: "The speed of sound is a constant, so if the space was altered by the time it's mean "timing error""

I have never claimed to be measuring anything. I'm talking with You about how technical concepts work and it's impact on results. When I ask you "Do you think jitter generates a timing fault in the analog signal?" I'm not asking if you can measure it - I'm asking about your technical understanding of the concept. You have now answered this question: Less jitter gives you perceived better space reconstruction.

I'm curious - do you have an own idea how "timing errors" (there aren't any!) in the analog realm hides space queues or suppresses reverb?

I believe we have come to an end to this. You make fantastic clocks and wonderful HW - really, that is what I think. But you don't seem to know why, in your experience, it improves the sound and you cant produce measurement evidence in the analog domain to prove the claims. So maybe you should not advertise with technical merits.

//

I have never claimed to be measuring anything. I'm talking with You about how technical concepts work and it's impact on results. When I ask you "Do you think jitter generates a timing fault in the analog signal?" I'm not asking if you can measure it - I'm asking about your technical understanding of the concept. You have now answered this question: Less jitter gives you perceived better space reconstruction.

I'm curious - do you have an own idea how "timing errors" (there aren't any!) in the analog realm hides space queues or suppresses reverb?

I believe we have come to an end to this. You make fantastic clocks and wonderful HW - really, that is what I think. But you don't seem to know why, in your experience, it improves the sound and you cant produce measurement evidence in the analog domain to prove the claims. So maybe you should not advertise with technical merits.

//

Last edited:

I alos like to express my sincere apology to the forum for this very long an inappropriate discussion that I have contributed to in this thread - sorry. It is as miss-placed as a purchase of a product for the sole purpose to show how bad it is because the customer do not "agree" on the design and how clever one can be in improving it. Especially as noting can be proved by the "improvement" - its the most silly but also insulting thing I have encountered on a form I think...

//

//

You say: "The speed of sound is a constant, so if the space was altered by the time it's mean "timing error""

I have never claimed to be measuring anything. I'm talking with You about how technical concepts work and it's impact on results. When I ask you "Do you think jitter generates a timing fault in the analog signal?" I'm not asking if you can measure it - I'm asking about your technical understanding of the concept. You have now answered this question: Less jitter gives you perceived better space reconstruction.

I'm curious - do you have an own idea how "timing errors" (there aren't any!) in the analog realm hides space queues or suppresses reverb?

I believe we have come to an end to this. You make fantastic clocks and wonderful HW - really, that is what I think. But you don't seem to know why, in your experience, it improves the sound and you cant produce measurement evidence in the analog domain to prove the claims. So maybe you should not advertise with technical merits.

//

I can't produce measurement evidence in the analog domain to prove the claims in the same manner you can't produce measurement evidence that jitter alters THD.

So my claims have the same technical value of yours.

I can measure the jitter while you can't measure anything.

I have published my measurements, please publish yours.

You care about long term stability while I care about short term stability.

Opposite opinions?

Surely.

Last edited:

I alos like to express my sincere apology to the forum for this very long an inappropriate discussion that I have contributed to in this thread - sorry. It is as miss-placed as a purchase of a product for the sole purpose to show how bad it is because the customer do not "agree" on the design and how clever one can be in improving it. Especially as noting can be proved by the "improvement" - its the most silly but also insulting thing I have encountered on a form I think...

//

There is no insult buying a product offered on an diy audio forum to modify it as I see fit.

This is just the spirit of diy.

There is no insult saying I don't agree with the design choice.

It's a diy product so is quite logical debating about the projectual choices in a diy forum.

The insults are what I have got in reply to my posts for expressing my free opinion.

Yet, listening tests indicate that speaker distortion is one thing, amplifier distortion is something different and digital distortion is still something else entirely

Narrow minded engineers, insisting that thd measurements reveal all are to blame for this unfortunate confusion.

[emoji108]

Boooring!

It looks like Soeren has long clocked out here...

@soekris: Would you please provide us with an estimate regarding the update of the firmware that will use smaller steps to match the incoming clock? Also, would you consider to give us an option to change more settings, e.g. how oftern the clock gets updated, how long it takes to analyze before latching onto the incoming clock etc.? Thanks!

It looks like Soeren has long clocked out here...

@soekris: Would you please provide us with an estimate regarding the update of the firmware that will use smaller steps to match the incoming clock? Also, would you consider to give us an option to change more settings, e.g. how oftern the clock gets updated, how long it takes to analyze before latching onto the incoming clock etc.? Thanks!

I finally put together my multichannel (32 DA channels) converter today. From what I could tell so far two channels on the same RME sound card (16 channel DA) were exactly in sync. Sounds great, too.

Here's a preliminary picture:

I used an old AVID case for it. Put the active cooling back with the fans running at a very low voltage. 16 DAM1021 together in a case do produce some warmth.

I still don't understand how the output op amps in the DAM1021 are powered. It appears the voltage is always only slightly below the incoming DC voltage. That would be fine with a quality PSU powering the DAM, but how can there be clean DC with AC input only?

Here's a preliminary picture:

An externally hosted image should be here but it was not working when we last tested it.

I used an old AVID case for it. Put the active cooling back with the fans running at a very low voltage. 16 DAM1021 together in a case do produce some warmth.

I still don't understand how the output op amps in the DAM1021 are powered. It appears the voltage is always only slightly below the incoming DC voltage. That would be fine with a quality PSU powering the DAM, but how can there be clean DC with AC input only?

- Home

- Vendor's Bazaar

- Reference DAC Module - Discrete R-2R Sign Magnitude 24 bit 384 KHz