Hi!

Datasheet says 200mW, but is this per jfet or for the whole package? If it's per jfet, I assume 400mW per device is safe then?

Zen Mod once suggested that it's 200mW per jfet, but better to stay at 300mW for the whole package?

What's correct and safe?

Better to know for sure before I start cooking precious parts ;-))

All the best, Hannes

Datasheet says 200mW, but is this per jfet or for the whole package? If it's per jfet, I assume 400mW per device is safe then?

Zen Mod once suggested that it's 200mW per jfet, but better to stay at 300mW for the whole package?

What's correct and safe?

Better to know for sure before I start cooking precious parts ;-))

All the best, Hannes

h_a said:Datasheet says 200mW, but is this per jfet or for the whole package? If it's per jfet, I assume 400mW per device is safe then?

This is per FET.

It is NEVER safe to run ANY component at full rated power.

For a board mounted (un-heat-sinked) plastic case transistor with no metal tabs (eg, TO-126, TO-220, TO-247, TO-264), about half rated power is a good starting point for MAX power dissipation.

If it has a metal tab, then it all depends on what heatsink you are using. I never try to have more than 30 - 40 Celsius temperature rise, and 20 is preferable.

One additional remark -- the rating refers to ambient temperature of 25 degC. If the trasistor sits inside an enclosure of a Class A amp running at 60 degC, it needs further derating.

Of course one can always thermal glue a heatsink to a dual FET. As an indicator, a TO92 has a thermal resistance of 200 degC/W junction to ambient, but only 83 degC/W junction to case. A TO220 heatsink has typically 10-20 degC/W.

Patrick

Of course one can always thermal glue a heatsink to a dual FET. As an indicator, a TO92 has a thermal resistance of 200 degC/W junction to ambient, but only 83 degC/W junction to case. A TO220 heatsink has typically 10-20 degC/W.

Patrick

Thank you very much for your replies!

Good to have a rule of thumb.

Mr. Hansen, maybe you could take a short moment and please help me with your following statement that I've problems to understand:

In the K389V group buy thread you made the argument that a V-grade part with larger source resistor is fully equivalent to a BL-grade part (with lower or no source resistor).

Well, if you calculate the gain of the Pearl/Ono-MC-frontend (4x K170 cascoded, single ended), the following formula for the gain is given:

gain=<number of jfets> x output resistor/(source resistor+inverse transconductance of jfet)

If that regurlarly used equation is true, it does matter wether you use a BL or V grade part, since the source resistor for the V would be larger to get the same current, thus reducing gain.

Since BL and V are working at the same drain current, transconductance is also for both the same.

In the worst case one would reduce gain by half, so that is certainly not equivalent behaviour then.

What am I missing here?

It would be really great if you could shortly comment on that to help me understand.

Thank you very much! All the best, Hannes

Good to have a rule of thumb.

Mr. Hansen, maybe you could take a short moment and please help me with your following statement that I've problems to understand:

In the K389V group buy thread you made the argument that a V-grade part with larger source resistor is fully equivalent to a BL-grade part (with lower or no source resistor).

Well, if you calculate the gain of the Pearl/Ono-MC-frontend (4x K170 cascoded, single ended), the following formula for the gain is given:

gain=<number of jfets> x output resistor/(source resistor+inverse transconductance of jfet)

If that regurlarly used equation is true, it does matter wether you use a BL or V grade part, since the source resistor for the V would be larger to get the same current, thus reducing gain.

Since BL and V are working at the same drain current, transconductance is also for both the same.

In the worst case one would reduce gain by half, so that is certainly not equivalent behaviour then.

What am I missing here?

It would be really great if you could shortly comment on that to help me understand.

Thank you very much! All the best, Hannes

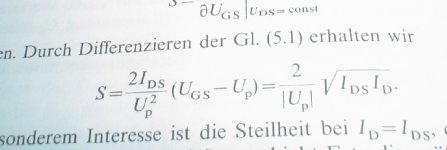

h_a said:gain=<number of jfets> x output resistor/(source resistor+inverse transconductance of jfet)

If that regurlarly used equation is true, it does matter wether you use a BL or V grade part, since the source resistor for the V would be larger to get the same current, thus reducing gain.

Since BL and V are working at the same drain current, transconductance is also for both the same.

The gain formula you gave is correct for a common-source circuit. And the transconductance is essentially just a function of Id.

And yes, if you used a large enough resistor to reduce the value of the Id to be the same in both devices, then the V part would have a slightly lower gain as a higher value of R would be required.

But what if you used both devices with NO source resistor? Which would have higher gain? See if you can figure out a way to have both devices have the same gain.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Solid State

- max dissipation of 2SK389