Prefer clock division to drive DAC MCLK. e.g if RCK is 200MHz then use a /2 to 100MHz clock for DAC.

sure theoretically, but...

that depends, i'm not aware of any readily available 200MHz XOs that are better (particularly for close in phase noise) than the clocks available in the lower range and multiplication is a pretty simple job with parts available that are very low jitter. its my feeling that its best to have the highest quality clock on the dac, dividing a higher speed clock to get the dac clock will reduce the period jitter of the signal itself, but it will add a small amount from the additional flip flop, I feel pretty sure that this would outweigh any reduction from the division.

I dont believe RCK is more important than MCK... MCK will have the last say with ESS and i'm not convinced the higher speed the better for RCK due to added demands on the PCB and supply. so compromising the dac MCK in order to gain a theoretical improvement from RCK earlier in the chain seems odd to me.

for instance the si570 could probably have its second clock buffer changed for a x2 for RCK, or it could I suppose be set to the higher speed natively for RCK and change one of the buffers to a div/2 for MCK, no additional part on either scheme

Last edited:

Just solder wires to the pads? the small centre-top u.fl pad is the signal, the other two are ground.

ouch!

too small for me.

too small for me.Or, if you do not wish to solder wires on the pads just mount U.FL connectors. Then get suitable U.FL lead assembly and on the other ends cut off the 'heads', extract the wires and dovetail connections to the DAC pin headers. Keep lengths as short as possible.

mmm... what a pitty cutting these "cool"

sure theoretically, but...

that depends, i'm not aware of any readily available 200MHz XOs that are better (particularly for close in phase noise) than the clocks available in the lower range and multiplication is a pretty simple job with parts available that are very low jitter. its my feeling that its best to have the highest quality clock on the dac, dividing a higher speed clock to get the dac clock will reduce the period jitter of the signal itself, but it will add a small amount from the additional flip flop, I feel pretty sure that this would outweigh any reduction from the division.

I dont believe RCK is more important than MCK... MCK will have the last say with ESS and i'm not convinced the higher speed the better for RCK due to added demands on the PCB and supply. so compromising the dac MCK in order to gain a theoretical improvement from RCK earlier in the chain seems odd to me.

for instance the si570 could probably have its second clock buffer changed for a x2 for RCK, or it could I suppose be set to the higher speed natively for RCK and change one of the buffers to a div/2 for MCK, no additional part on either scheme

Thanks Qusp, points noted but no harm trying.

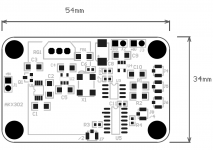

I have updated the Clock board with div/2 and div/4 output options for MCK and in snyc with RCK.

You could something similar with si570 but how do you sync them?

Attachments

Last edited:

Thanks Qusp, points noted but no harm trying.

no of course not, try what you like, thats the point of tyhese little boards, it just doesnt make sense to me to prioritize RCK jitter over MCK and I think thats what the setup above does.

sync what to what? the si570 module has 2 buffered outputs to cater for dual mono, if you divide one and steal the reference clock from the higher speed output, wouldnt both be in sync?I have updated the Clock board with div/2 and div/4 output options for MCK and in snyc with RCK.

You could something similar with si570 but how do you sync them?

too much? no, more? yes and total noise RMS will of course be higher with higher speed.hochopeper said:For a 200MHz RCLK clock I don't think we've really stressed this PCB or the parts too much.

... the si570 module has 2 buffered outputs to cater for dual mono, if you divide one and steal the reference clock from the higher speed output, wouldnt both be in sync?

Ok thanks got it. From the same output, of course.

But

you will need additional parts like FFs..... div/2 for MCK, no additional part on either scheme

This is what my own clock module is doing. However, I am not really warming to the idea of Si570 with its PLL synthesized output being any better than a native cut XO. Has any one tried Si570 with ESS DAC (for MCK) and compared results e.g with CCHD950 or similar?

Last edited:

To save confusion, is there a better word than synch that we can use when the MCLK is in synch with all signals, but also a direct multiple of the sample rate? I can see that some would easily get confused between the two different modes that we're using the same word for. I think this is why you used the psynch term in your docs Acko, I can see already there is some mixing up of the terms here, though the use of synch in the recent posts is all technically correct, if read by people who're on the ball. I am, however, worried a touch that some in this thread aren't all at the same level of understanding and the mix and match vocab perhaps doesn't make it easy.

Acko, Ian developed an Si570 board and tested it, he prefers it I've put together a wiki page compiling links to different parts of Ian's projects - his posts on his Si570 experiments are all here - Ian's I2S FIFO Project - diyAudio - his comment was that he preferred the final revision of the Si570 using the TPS7A4700 regulator that I linked - when the Si570 is operating at 95/98Mhz. He previously used his DualXO board with CCHD957 @ 45/49MHz clocks. He posted some measurements too, from memory both arrangements are below the noise floor of his equipment.

Acko, Ian developed an Si570 board and tested it, he prefers it I've put together a wiki page compiling links to different parts of Ian's projects - his posts on his Si570 experiments are all here - Ian's I2S FIFO Project - diyAudio - his comment was that he preferred the final revision of the Si570 using the TPS7A4700 regulator that I linked - when the Si570 is operating at 95/98Mhz. He previously used his DualXO board with CCHD957 @ 45/49MHz clocks. He posted some measurements too, from memory both arrangements are below the noise floor of his equipment.

Last edited:

Thanks Qusp, points noted but no harm trying.

I have updated the Clock board with div/2 and div/4 output options for MCK and in snyc with RCK.

You could something similar with si570 but how do you sync them?

Ok thanks got it. From the same output, of course.

But

you will need additional parts like FFs

This is what my own clock module is doing. However, I am not really warming to the idea of Si570 with its PLL synthesized output being any better than a native cut XO. Has any one tried Si570 with ESS DAC (for MCK) and compared results e.g with CCHD950 or similar?

I was suggesting that you could replace one of the buffer positions on the board, not nessecarily add one, but even if it meant adding one I think adding some small amount of jitter to RCK vs MCK is not a big deal anyway, since MCK will have the final say.

the si570 uses a pure crystal at its heart. check Ians measurements out, they are very impressive, not quite as good as crystek, but still VERY low, insignificantly low given the flexibility it gives. I dare say lower than any of the 200MHz clocks youve mentioned. actually from memory it was objectively better than chhd950, but not as good as 957. theoretically anyway, because as chris mentions, its performance is buried below Ians 2ps measurement noise floor, but the output is VERY clean

Last edited:

Last edited:

How'd I miss that??

Quick searching effort returns this - http://www.diyaudio.com/forums/digi...mate-weapon-fight-jitter-233.html#post3359311

I will add that to the FIFO wiki too for future reference.

Quick searching effort returns this - http://www.diyaudio.com/forums/digi...mate-weapon-fight-jitter-233.html#post3359311

I will add that to the FIFO wiki too for future reference.

LMFAO

also to be clear, in addition to the 2ps noise floor, these measures are at the actual output of the clock buffer, not of the si570 itself, so the small jitter added by the potato FF is included. also note the cool speed i'd say the board would need a bit of software hacking to enable higher than 98.304MHz, but its most certainly capable of it

i'd say the board would need a bit of software hacking to enable higher than 98.304MHz, but its most certainly capable of it

also to be clear, in addition to the 2ps noise floor, these measures are at the actual output of the clock buffer, not of the si570 itself, so the small jitter added by the potato FF is included. also note the cool speed

Thank Guys, helps a lot! I started to spin of this Clock module because of the 100Mhz limit of Ian module and the re-clocker can take higher speeds. Anyway it is all good to experiment. I will check out Ian's design. Trying to avoid duplication and wasting time... My own DACs have no XO on-board so welcome anything favourable.

Chris, you are right. Confusion with the term Sync can creep in quickly and can be a fine line at times. e.g. if RCK is clocked at 98.304Mhz or 196.608MHz instead (and linked to DAC MCK) then it becomes in "True" sync with some of the higher Sampling Frequencies. So "Pseudo" Sync at other RCK frequencies even if DAC MCK is linked to RCK. Hope this clarifies

Chris, you are right. Confusion with the term Sync can creep in quickly and can be a fine line at times. e.g. if RCK is clocked at 98.304Mhz or 196.608MHz instead (and linked to DAC MCK) then it becomes in "True" sync with some of the higher Sampling Frequencies. So "Pseudo" Sync at other RCK frequencies even if DAC MCK is linked to RCK. Hope this clarifies

Last edited:

....

dividing a higher speed clock to get the dac clock will reduce the period jitter of the signal itself, but it will add a small amount from the additional flip flop, I feel pretty sure that this would outweigh any reduction from the division.

.....

... in addition to the 2ps noise floor, these measures are at the actual output of the clock buffer, not of the si570 itself, so the small jitter added by the potato FF is included.

...

I see from Ian's results the additive jitter from the FFs themselves are minimal

sure I know, I didnt mean it was significant overall, but its very likely more significant than the reduction by dividing and dividing will only reduce period jitter I would think, not phase jitter. the impact of the FF will depend on which FF and the interconnection/load line I would think. I wonder if we can expect the same performance from a division circuit vs a straight buffer. interesting questions that can only really be answered by measuring

It also relies on you being able to find a 200MHz clock that is lower jitter (close in jitter) than the 50-100MHz clocks that are fairly readily available, i'm not aware of any, the si570 itself will do much more than that though.

It also relies on you being able to find a 200MHz clock that is lower jitter (close in jitter) than the 50-100MHz clocks that are fairly readily available, i'm not aware of any, the si570 itself will do much more than that though.

Last edited:

...

It also relies on you being able to find a 200MHz clock that is lower jitter (close in jitter) than the 50-100MHz clocks that are fairly readily available,

...

Yes, of course, boils down to intrinsic phase jitter of the XOs mainly

Thanks!

....

e.g. if RCK is clocked at 98.304Mhz or 196.608MHz instead (and linked to DAC MCK) then it becomes in "True" sync with some of the higher Sampling Frequencies. So "Pseudo" Sync at other RCK frequencies even if DAC MCK is linked to RCK.

....

Correction and apologies! For the AKL-AMN board simply applying 98.304MHz at RCK does not turn it into "True" Sync mode as indicated earlier as the Bit clock from transport is not exactly in sync with RCK. So still PSync.

True Sync mode is only as shown in the App Notes for "Sync Mode" but limited to Fs up to 192KHz due the Amanero Clock limitation at 24.576MHz. Appears that there is a double clock version of Amanero (49.152MHz) available and this should able to take higher Fs

High Fs True sync operation can also be realised if the clock module interacts with the transport such as the AKX701 Turbo Clock and of course Ian's Si570 Clock Module

LMFAO

also to be clear, in addition to the 2ps noise floor, these measures are at the actual output of the clock buffer, not of the si570 itself, so the small jitter added by the potato FF is included. also note the cool speedi'd say the board would need a bit of software hacking to enable higher than 98.304MHz, but its most certainly capable of it

I just had a peak at my Si570 board .. there are NXP FF on the final production boards.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Group Buys

- Amanero Isolator/Reclocker GB