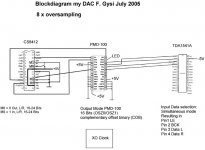

I am planning an external 8 x oversampling DAC, SPDIF input, based on CS8412 receiver, PMD100 Filter and a TDA1541A DAC.

Actually, I am preparing a block diagram about the mode setup and the interconnections of this three chips.

As I am not an EE, I have now (at least) two important questions:

1. Is the interconnect between PMD100 and TDA1541A correct?

2. I dont know, where to feed in what frequencies from the XO clock. Just know, M0 has to be 1 to set the CS8412 in "slave" mode.

Every help is very welcome!

Franz

Actually, I am preparing a block diagram about the mode setup and the interconnections of this three chips.

As I am not an EE, I have now (at least) two important questions:

1. Is the interconnect between PMD100 and TDA1541A correct?

2. I dont know, where to feed in what frequencies from the XO clock. Just know, M0 has to be 1 to set the CS8412 in "slave" mode.

Every help is very welcome!

Franz

Attachments

Sorry, I just have one PMD100 and I hope, it is still working. See here:

http://www.diyaudio.com/forums/showthread.php?postid=683268#post683268

Franz

http://www.diyaudio.com/forums/showthread.php?postid=683268#post683268

Franz

Franz G said:

1. Is the interconnect between PMD100 and TDA1541A correct?

As connected, so long as the CS8412 in fmt 0, it will work.

2. I dont know, where to feed in what frequencies from the XO clock. Just know, M0 has to be 1 to set the CS8412 in "slave" mode.

When the CS8412 is in slave mode, fmt 1, MCLK is still an output, so you will have to derive FSYNC and SCLK from your XO module.

Thanks for your answer, rfbrw!

I am still not sure about the frequencies, about the (simple?) math behind it

Let's resume my actual understanding:

I will set the CS8412 to fmt 1 (M0 = high), to have FSYNC and SCLK as input and feed them from a external clock.

Is it correct, to derive 44.1kHz to FSYNC and 5.6448MHz to SCK? Will this result in 8x oversampling?

Kind regards

Franz

P.S.

Here a foto of the future enclosure, psu, input section and display: a burned out Classé DAC-1 (with additional fuses in the psu )

)

I am still not sure about the frequencies, about the (simple?) math behind it

Let's resume my actual understanding:

I will set the CS8412 to fmt 1 (M0 = high), to have FSYNC and SCLK as input and feed them from a external clock.

Is it correct, to derive 44.1kHz to FSYNC and 5.6448MHz to SCK? Will this result in 8x oversampling?

Kind regards

Franz

P.S.

Here a foto of the future enclosure, psu, input section and display: a burned out Classé DAC-1 (with additional fuses in the psu

Attachments

Zoran said:Hi

If You like oversampling that is ok

but maybee You should leave the room for

just 2x oversampling in stand alone mode PMD100?

No 2x in standalone mode.

Zoran said:Say RFBR, is there any chance to run PMD100 in non-oversamled mode,

in state of controled the PMD100 with some processor... And for your oppinion,

is that option acceptable?

Not possible. 2x,4x and 8x only.

I tried the schematic in post #1. Unfortunately it did not work. I got VERY distorted sound.

Use XMOS SPDIF, it works. Other SPDIF such as computer sound chip, PCM2706 SPDIF will produce loud noise and music together

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Digital Source

- Questions CS8412 - PMD100 - TDA1541A