All,

A couple of questions on SPDIF mods:

1. Is it possible to reclock the SPDIF output just before it leaves the transport or after it enters the DAC using a simple 74HC74 with an asynchronous clock? What impact/benefit does this bring?

2. Sometime ago, ELSO published his SPDIF interface which uses an OPA603 driver. Excuse the ignorance, but can BUF634 be used instead? Also, does the input of the DAC need to be modded as per ELSO's original post, or does that not matter?

Thanks

Ryan

A couple of questions on SPDIF mods:

1. Is it possible to reclock the SPDIF output just before it leaves the transport or after it enters the DAC using a simple 74HC74 with an asynchronous clock? What impact/benefit does this bring?

2. Sometime ago, ELSO published his SPDIF interface which uses an OPA603 driver. Excuse the ignorance, but can BUF634 be used instead? Also, does the input of the DAC need to be modded as per ELSO's original post, or does that not matter?

Thanks

Ryan

Hi Ryan,Dr.H said:All,

A couple of questions on SPDIF mods:

1. Is it possible to reclock the SPDIF output just before it leaves the transport or after it enters the DAC using a simple 74HC74 with an asynchronous clock? What impact/benefit does this bring?

2. Sometime ago, ELSO published his SPDIF interface which uses an OPA603 driver. Excuse the ignorance, but can BUF634 be used instead? Also, does the input of the DAC need to be modded as per ELSO's original post, or does that not matter?

Thanks

Ryan

I think it can be done but as said earlier I would reclock after the DIR or after the digital filter in the DAC. I am not going to explain this again.

The AD810 seems to be a nice replacement for the obsolete OPA603. The latest scheme also works with a standard DAC input with digital transformer as it has standard SPDIF output level.

Ryan,

The cleanest possible clock in a CD drive, wouldn't that be the oscilator that clocks the drive itself?

Does your drive only have an SPDIF output available? If that is the case, I would decode it and pair it up with the oscilator clock.

If you have other options than SPDIF (I2S etc) available, see if your filter/DAC supports that format.

For my latest DAC board I actually have the option of choosing between CS8414 output and internal CD player signals (among them the crystal freqyency divided down by 2).

Greetings,

Børge

The cleanest possible clock in a CD drive, wouldn't that be the oscilator that clocks the drive itself?

Does your drive only have an SPDIF output available? If that is the case, I would decode it and pair it up with the oscilator clock.

If you have other options than SPDIF (I2S etc) available, see if your filter/DAC supports that format.

For my latest DAC board I actually have the option of choosing between CS8414 output and internal CD player signals (among them the crystal freqyency divided down by 2).

Greetings,

Børge

My PS audio transport reclocks the output with a ALS74 at the outputs. The signal is feed from Q and QNot right into the transformer, there is an impedance match their. Of course if you don't have a really good clock like Jocko or Elso it still will jitter even after it's reclocked. Ground noise in the transport can really impair the performance of the SPDIF.

I have modified the clock in my transport several time now, so the better clock the better the sound. I believe it better to remove the jitter at the cource of course you can use a sample rate converter to reclock the data in the dac. In fact I do both.

I have modified the clock in my transport several time now, so the better clock the better the sound. I believe it better to remove the jitter at the cource of course you can use a sample rate converter to reclock the data in the dac. In fact I do both.

Thanks for the responses.

Why would sonething like a BUF634 be useful to drive the coaxial cable? Why the need for a OPA633 or AD810? Cretainly OPA633 is just a buffer, like BUF634.

Jewlson: I was think more along the lines of using a simple 74HC74 fed from a separate clean clock. How do you do your reclocking? Is the ALS74 being fed from the master clock in the transport or a seperate clock (with its own power supply...)

FYI, I have a Proceed PDT3, which drives a Theta DAC. The Theta has extensive post CS8412 reclocking.

Thanks

Ryan

Why would sonething like a BUF634 be useful to drive the coaxial cable? Why the need for a OPA633 or AD810? Cretainly OPA633 is just a buffer, like BUF634.

Jewlson: I was think more along the lines of using a simple 74HC74 fed from a separate clean clock. How do you do your reclocking? Is the ALS74 being fed from the master clock in the transport or a seperate clock (with its own power supply...)

FYI, I have a Proceed PDT3, which drives a Theta DAC. The Theta has extensive post CS8412 reclocking.

Thanks

Ryan

Using an high speed opamp would not be my first choice. I used the ALS part because of it's low ground bounce noise.

All HC parts can under shoot the ground do to the output design which can lead to noise.

The ALS is feed from a modifed master clock, I stongly recomend you purchasing a after market one from Jocko Homo. The are some other good one too.

The 8412 is only marginal good at removing jitter from the incoming signal. The power for the receiver has to be very low noise for it to work well. The PLL in side the chip is not so great.

All HC parts can under shoot the ground do to the output design which can lead to noise.

The ALS is feed from a modifed master clock, I stongly recomend you purchasing a after market one from Jocko Homo. The are some other good one too.

The 8412 is only marginal good at removing jitter from the incoming signal. The power for the receiver has to be very low noise for it to work well. The PLL in side the chip is not so great.

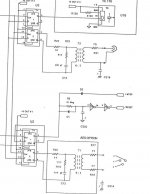

Attachments

jewilson said:Using an high speed opamp would not be my first choice. I used the ALS part because of it's low ground bounce noise.

All HC parts can under shoot the ground do to the output design which can lead to noise.

The ALS is feed from a modifed master clock, I stongly recomend you purchasing a after market one from Jocko Homo. The are some other good one too.

The 8412 is only marginal good at removing jitter from the incoming signal. The power for the receiver has to be very low noise for it to work well. The PLL in side the chip is not so great.

Hi

Are you suggesting that ALS logic does not sugffer from cross current ?

On the contrary, these gates are that fast that the excitation of the drain source capacitor induces "cross current like" currents again.....

cheers

Smoke Curtains

So, which logic family do you recommend?

Guido,Guido Tent said:

Hi

Are you suggesting that ALS logic does not sugffer from cross current ?

On the contrary, these gates are that fast that the excitation of the drain source capacitor induces "cross current like" currents again.....

cheers

So, which logic family do you recommend?

recomendation please..........

OK Guido, what are your recomendation.

Also, the only place I know of cross-currents is in the ocean, you must fill me in this idea. Maybe you’re talking about circulating ground currents?

Anyway the facts are that the push-pull outputs of the CMOS device "can" under 0 volts or ground. Of course some CMOS logic families are worst than others.

OK Guido, what are your recomendation.

Also, the only place I know of cross-currents is in the ocean, you must fill me in this idea. Maybe you’re talking about circulating ground currents?

Anyway the facts are that the push-pull outputs of the CMOS device "can" under 0 volts or ground. Of course some CMOS logic families are worst than others.

Re: Smoke Curtains

I prefer the tradeoff between required speed (slope), drive capability and cross current.

Sometimes that is HC, sometimes HCU, sometimes ACT, sometimes even HEF, it depends on the application.

I was triggered because Jewilson stated that ALS would produce lees switching current......

cheers,

Elso Kwak said:

Guido,

So, which logic family do you recommend?

I prefer the tradeoff between required speed (slope), drive capability and cross current.

Sometimes that is HC, sometimes HCU, sometimes ACT, sometimes even HEF, it depends on the application.

I was triggered because Jewilson stated that ALS would produce lees switching current......

cheers,

Re: Now I know that he is pulling our leg......

Sometimes I use..........

No that is too easy........

Regular readers of the forum know my favourite logic family.

There we are, you know it's all about the spirit you know. It is all about the choice on beat you know....Put the boogie bean in there.........You are going to boogie!

PS I first wrote bogy, and made an unintentioned joke!

Jocko Homo said:ACT??

Are you serious??

No.........you can't be..........right???

Jocko

Sometimes I use..........

No that is too easy........

Regular readers of the forum know my favourite logic family.

There we are, you know it's all about the spirit you know. It is all about the choice on beat you know....Put the boogie bean in there.........You are going to boogie!

PS I first wrote bogy, and made an unintentioned joke!

Guido,

We are discussing the SPDIF and it anit all the fast. While ALS is not all the quick it’s fast enough, and it does not plow below ground. When your ACT logic switches from a high to a low it switches below ground, the effect will cause the ground potential to change for that time, that increase the systems susceptibility to jitter.

So if the master clock not stable from bit to bit over time then it's possible for ALS to increase the jitter. Heck if we talking SMD it's not a real important issue as compared with dips. I guess all my stuff was designed and built back in the dark ages.

We are discussing the SPDIF and it anit all the fast. While ALS is not all the quick it’s fast enough, and it does not plow below ground. When your ACT logic switches from a high to a low it switches below ground, the effect will cause the ground potential to change for that time, that increase the systems susceptibility to jitter.

So if the master clock not stable from bit to bit over time then it's possible for ALS to increase the jitter. Heck if we talking SMD it's not a real important issue as compared with dips. I guess all my stuff was designed and built back in the dark ages.

jewilson said:Guido,

We are discussing the SPDIF and it anit all the fast. While ALS is not all the quick it’s fast enough, and it does not plow below ground. When your ACT logic switches from a high to a low it switches below ground, the effect will cause the ground potential to change for that time, that increase the systems susceptibility to jitter.

So if the master clock not stable from bit to bit over time then it's possible for ALS to increase the jitter. Heck if we talking SMD it's not a real important issue as compared with dips. I guess all my stuff was designed and built back in the dark ages.

Hi Jim,

We agree. The point I tried to make is that ANY logic type of family generates switching current when changing state. The origina may be different, but it can all be measured back in supply (hence ground) lines.

For this reason, the type of logic used needs attention, as it should be the result of required output slope, drive current and should not be faster than required.

In addition the cross current could be examined, unfortunately not many manufacturers supply data in their sheets.....

cheers

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Digital Source

- Mods to the SPDIF output of a CD transport