Here is an idea that's been floating around in my head for a while, and I would like to get your comments on it.

The idea is to use one of the many video-DACs that runs at more than 100MHz with resolution from 8 to 16 bits. The 24-bit audio would be oversampled by a very large number, say 1024, from 48kHx to 49.152MHz. Then dither would be added, and the result truncated to the DACs width of say 8 bits. The dither would need to be noiseshaped, but since the oversampling-ratio is so high, the noiseshaping function could be first-order. Now all you need is a first-order analog filter after the DAC to remove the noise above the audioband.

This approach is different from a multi-bit delta-sigma DAC (PCM1792,AD1955), since these DACs often use very high-order noise-shaping.

Pros:

-Video-DACs have high output current, 20mA differential, ensures good SNR.

-Video-DACs are designed to be used with a simple resistor as I/V converter, no need for fancy op-amps.

-Video-DACs have an externally adjustable reference current, this can be used for volume control.

Cons:

-The extreme oversampling would require an FPGA which is expensive and not DIY friendly.

See here for an example of a video-DAC.

I used a 20Hz sinewave sampled at 48kHz to illustrate what a 20kHz sinewave would look like when sampled at 48MHz. A sinewave was created at -100dB with 32-bit resolution, then converted to 8-bits with 1-bit TPD dither with noiseshaping-function A. The result is over 130dB dynamic range in the audioband. This would improve even more if a 12-bit DAC was used.

What I would like to hear is: Do you know if somebody is already doing something like this? Have I overlooked something that would make this not work?

What I don't want to hear is: "Why don't you just use a PCM1738,TDA1541,<insert favorite chip here> instead?"

The idea is to use one of the many video-DACs that runs at more than 100MHz with resolution from 8 to 16 bits. The 24-bit audio would be oversampled by a very large number, say 1024, from 48kHx to 49.152MHz. Then dither would be added, and the result truncated to the DACs width of say 8 bits. The dither would need to be noiseshaped, but since the oversampling-ratio is so high, the noiseshaping function could be first-order. Now all you need is a first-order analog filter after the DAC to remove the noise above the audioband.

This approach is different from a multi-bit delta-sigma DAC (PCM1792,AD1955), since these DACs often use very high-order noise-shaping.

Pros:

-Video-DACs have high output current, 20mA differential, ensures good SNR.

-Video-DACs are designed to be used with a simple resistor as I/V converter, no need for fancy op-amps.

-Video-DACs have an externally adjustable reference current, this can be used for volume control.

Cons:

-The extreme oversampling would require an FPGA which is expensive and not DIY friendly.

See here for an example of a video-DAC.

I used a 20Hz sinewave sampled at 48kHz to illustrate what a 20kHz sinewave would look like when sampled at 48MHz. A sinewave was created at -100dB with 32-bit resolution, then converted to 8-bits with 1-bit TPD dither with noiseshaping-function A. The result is over 130dB dynamic range in the audioband. This would improve even more if a 12-bit DAC was used.

What I would like to hear is: Do you know if somebody is already doing something like this? Have I overlooked something that would make this not work?

What I don't want to hear is: "Why don't you just use a PCM1738,TDA1541,<insert favorite chip here> instead?"

Attachments

Actually the more interesting idea is to use 10-12 bit flash or pipelined video ADCs in a recording system that is much less oversampled/noisehaped than your average audio ADC, running at 176kHz, no anti-aliasing filters, and then show the recording industry (and the SACD-sect) a thing or two.

Konnichiwa,

I have been thinking about something somewhat similar, but rather using tripple 12-Bit DAC's and "stacking" them with added interleaving to average out any errors. But I think a semi-discrete R2R DAC is more worth spending time on.

Sayonara

ojg said:No takers? Or are you all still ROTFLYAO?

I have been thinking about something somewhat similar, but rather using tripple 12-Bit DAC's and "stacking" them with added interleaving to average out any errors. But I think a semi-discrete R2R DAC is more worth spending time on.

Sayonara

Werner said:Actually the more interesting idea is to use 10-12 bit flash or pipelined video ADCs in a recording system that is much less oversampled/noisehaped than your average audio ADC, running at 176kHz, no anti-aliasing filters, and then show the recording industry (and the SACD-sect) a thing or two.

I completely agree, but unfortunately they don't give us DIY'ers access to the recording sessions. I wonder why... So all we are left with is trying to improve the decoding end.

Kuei Yang Wang said:I have been thinking about something somewhat similar, but rather using tripple 12-Bit DAC's and "stacking" them with added interleaving to average out any errors. But I think a semi-discrete R2R DAC is more worth spending time on.

Yes I have been thinking about a discrete R-2R DAC as well, and you could ofcourse substitute the video-DAC with a discrete version. The interleaving is more tricky though. I assume this would be similar to how the dCS ring-dac works? Do you have any detailed information on it?

I have been toying with the idea of building a DAC around video DAC chips (AD768 in particular) for a while too... Not a first order Delta-Sigma though, but a straightforward non-oversampled design (which are in fashion nowadays). That needs some glue logic to do serial to parallel conversion and data retiming, which I was planning to stuff into a single CPLD, if I ever got around to it. Using FPGA will give the design flexibility to switch upsampling algorithms at will, with the downside that somebody will need to write the software.

It might be a fun thing to do . Maybe I should get one of those FPGA evaluation boards and read up on VHDL...

. Maybe I should get one of those FPGA evaluation boards and read up on VHDL...

It might be a fun thing to do

One big problem is that the audio dac's are designed to run from the timming and data format that provided by the current crop of digital filters. So that means you would have to add a lot of logic to this dac to get to work.

So even if you could find one with the same low level resolution and linearity the data format would be different. Also, what the point the we have no requirements for 1 Mhz sampling .

So even if you could find one with the same low level resolution and linearity the data format would be different. Also, what the point the we have no requirements for 1 Mhz sampling .

The AD768 and the AD9752 are NOT video dacs. Video dacs accept data in specified formats with wordlengths between 8 and 10 bits, though the internal wordlengths are often longer for processing,and none of them that bear any relation to the format of digital audio. They are also often loaded with video specific add-ons and not all of them can be disabled.

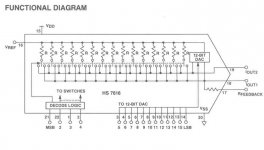

This is actually what dCs does in their Elgar series. The digital signal is oversampled a lot, noise-shaped, and fed to a 8 bits or so DAC which is (I think) implemented in discrete parts.

I have never heard these products though.

I have thought of similar things, using a high-frequency DAC (most of which, but not all, are video dacs) and oversampling. But you'd need to use something incredibly fast to pump out these samples, and the only thing which comes to mind is a FPGA. It would have potential, though.

However I'd advise against using 1LSB dither, rather use dither over several LSB's ; you'll get more noise (won't matter anyway) but more spreading of the LSB nonlinearities in the DAC (which is better).

"Multibit" sigma delta DACs have so few bits they still seem suspicious to me...

I have never heard these products though.

I have thought of similar things, using a high-frequency DAC (most of which, but not all, are video dacs) and oversampling. But you'd need to use something incredibly fast to pump out these samples, and the only thing which comes to mind is a FPGA. It would have potential, though.

However I'd advise against using 1LSB dither, rather use dither over several LSB's ; you'll get more noise (won't matter anyway) but more spreading of the LSB nonlinearities in the DAC (which is better).

"Multibit" sigma delta DACs have so few bits they still seem suspicious to me...

peufeu said:This is actually what dCs does in their Elgar series. The digital signal is oversampled a lot, noise-shaped, and fed to a 8 bits or so DAC which is (I think) implemented in discrete parts.

While the dCs ringDAC does oversample it is at a relatively low 64x and the dac is only around 5bits and the current sources all have the same weight unlike a normal multibit dac.

using a high-frequency DAC (most of which, but not all, are video dacs)

Wrong. The high MHz/low GHZ end of the market is occupied by communications and data acquistion ADC/DACs. These speeds are not needed for video.

andrei said:I have been toying with the idea of building a DAC around video DAC chips (AD768 in particular) for a while too... Not a first order Delta-Sigma though, but a straightforward non-oversampled design (which are in fashion nowadays). That needs some glue logic to do serial to parallel conversion and data retiming, which I was planning to stuff into a single CPLD, if I ever got around to it.

If you are into non-OS DACs then this could be interesting. Converting the audio data to parallel is fairly simple and can even be done with discrete logic. From the top of my head you would need 4 8-bit serial-in parallel-out shift registers, one 4-bit counter and some inverters.

rfbrw said:The AD768 and the AD9752 are NOT video dacs.

Yeah, I was probably wrong there, seems like they are intended for communication like VDSL.

peufeu [/i][B] However I'd advise against using 1LSB dither said:While the dCs ringDAC does oversample it is at a relatively low 64x and the dac is only around 5bits and the current sources all have the same weight unlike a normal multibit dac.

I believe you are right, but then how is this different from being just a discrete implementation of a PCM1738/1792?

Thanks for everybodys input!

You know that some of the DACs that are on the market have multiple internal ladder DAC's inside already. I mean what you really need to make this fly are DACs that that allow you to use your own voltage reference. Then you can scale the bits accordingly.

The other day I saw that TI now has a 16 bit video DAC, I kfor got the speed of the device.

The other day I saw that TI now has a 16 bit video DAC, I kfor got the speed of the device.

ojg said:

I believe you are right, but then how is this different from being just a discrete implementation of a PCM1738/1792?

Thanks for everybodys input!

A normal multibit dac has a bit weight that scales with the position of the bit i.e. the weighting of the lsb of a 16 bit dac is 1/65536.

As the wordlength increases the values required for the current sources get increasing smaller and more difficult and expensive to fabricate.

The dCs ringdac has unitary weighted current sources ie. they all have the same value. The output current is formed by selecting the appropriate number of current sources and this is governed the control software.

The dCs ringdac has unitary weighted current sources ie. they all have the same value

And the used current sources are "rotated" hence the name "ring-dac". With 5 current sources, you can make any value from 0 to 5 (by activating 0 to 5 sources), but the value 1 does not always correspond to the same source because of the rotation. This helps balancing any inconsistencies between the sources.

Anyway, this still is around 2.5 bits (=log2 (6)) times 64x oversampling, and I find it hard to believe that it can reproduce the full information contained in 16 bits samples...

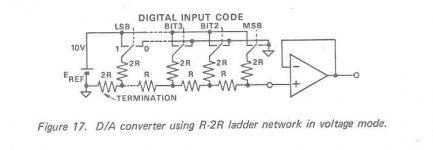

If your looking to build a accurate high speed DAC you can do this discretely using the R2R ladder approach. I have found the controlling charge injection and current source to limit the accuracy in the design of Delta Sigma DAC.

The problem with building a R2R DAC is scaling the R2R ladders and producing a voltage reference that is stable with very low noise and low impedance. However, with S102 Vishay resistors the ladder not a big deal it just becomes costly. So building a DAC in this method is normally out of the question for the Burr Brown and Analog Devices due to cost, hence cheap Delta Sigma converters. There use to be several companies that made Hybrids DAC but they seem to have bit the dust; Hybrid Systems, MicroNetworks and Analogic were some of these companies.

In addition, there use to be a number of resistor companies making R2R network on thin film substrate. Anyway, I have found during design and testing that the accuracy of these DAC's to be far superior to the Delta Sigma's since low level accuracy is compromised. So with a little effort multiple R2R DAC’s can be series together with a summing junction.

The problem with building a R2R DAC is scaling the R2R ladders and producing a voltage reference that is stable with very low noise and low impedance. However, with S102 Vishay resistors the ladder not a big deal it just becomes costly. So building a DAC in this method is normally out of the question for the Burr Brown and Analog Devices due to cost, hence cheap Delta Sigma converters. There use to be several companies that made Hybrids DAC but they seem to have bit the dust; Hybrid Systems, MicroNetworks and Analogic were some of these companies.

In addition, there use to be a number of resistor companies making R2R network on thin film substrate. Anyway, I have found during design and testing that the accuracy of these DAC's to be far superior to the Delta Sigma's since low level accuracy is compromised. So with a little effort multiple R2R DAC’s can be series together with a summing junction.

Could you post a simple schematic for a R2R dac ? I know I'm looking stupid, but I don't know whats that

I know it's a ladder with many times R and 2R, I saw stepped attenautors like this, but what is used for switching ? CMOS switches as usual ? (charge injection etc) or something else ?

I know it's a ladder with many times R and 2R, I saw stepped attenautors like this, but what is used for switching ? CMOS switches as usual ? (charge injection etc) or something else ?

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Digital Source

- Using Video-DACs for audio