Hi Koldby.(6K8 resistor is from DEM to +5V)

Koldby

I hope you are wrong because I have these from DEM to -15 ??

Rgds,

Hello Ceglar.

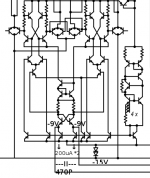

I don't know if you still read this thread, but if you do (or somebody else knows) - what is the purpose of the 56uF capacitor over the I/V resistor in your schematic?

Vidar

Hi Vidar

This value is actually 56nF from what i can make sense of. 56uF is totally way too high a value to have any practical purpose in this position.

As many of you are probably aware, this cap limits bandwidth into the output stage by providing a low impedance to ground for the fast transient of the square wave coming out of the DAC.

Hi Koldby.

I hope you are wrong because I have these from DEM to -15 ??

Rgds,

Hi niamex,

Koldby is indeed incorrect. 2 x 6k8 resistors go to the DEM pins from -15 not +5.

No problem,

Probably not necessary to go with a value lower than 6k8 but i guess it wont hurt, although ive had great results with this value.

56pf is too small a value to be using for this purpose. You should be in the range of 50 to 120nF.

Sure, mistype. Not easy to get the exact value - it is always 6K8 written on it but

Hi Vidar

This value is actually 56nF from what i can make sense of. 56uF is totally way too high a value to have any practical purpose in this position.

As many of you are probably aware, this cap limits bandwidth into the output stage by providing a low impedance to ground for the fast transient of the square wave coming out of the DAC.

I wasn't aware. Thank you for that.

Hi Koldby.

I hope you are wrong because I have these from DEM to -15 ??

Rgds,

Yep my wrong. It is -15V

Hi niamex,

Koldby is indeed incorrect. 2 x 6k8 resistors go to the DEM pins from -15 not +5.

On the distinction-1541 i putted this one : manufacter part number : RG2012P-682-B-T5 (Sussumu low noise resistor RG serie)... You can't go wrong with it... (maybe too small for tweaking EBAY kits

Did you check the waveform with a scope? I don't doubt that 10K works too...2 x 10k works for me. I don't think the actual value is particularly important (within some range).

I remember once asking the question how the 6K8 was determined, but unfortunately I got no answer... Your post is a bit of an answer to that question.

Hello Ceglar.

I don't know if you still read this thread, but if you do (or somebody else knows) - what is the purpose of the 56uF capacitor over the I/V resistor in your schematic?

Vidar

Hi Vidar,

56nF//R forms low pass filter.. at higher frequencies the cap represents the lowest impedance path to/from signal common whilst the resistor has a fixed impedance (within reason).

Shane.

The waveform is the same as John's in post #5060. My DEM capacitor is 510 pF, the frequency is 172 kHz. My goal was to achive auto-lock to 4x sample frequency, but it did not occur.Did you check the waveform with a scope? I don't doubt that 10K works too...

I remember once asking the question how the 6K8 was determined, but unfortunately I got no answer... Your post is a bit of an answer to that question.

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A