So i've been fighting this part for a couple weeks now.

I have an application where I need to clear the non-audio and validity bits in an SPDIF bitstream. I'm using the wm8804 in 3-wire i2c mode.

It was easy enough to get the wm8804 to passthrough SPDIF from RX0 to TX0 internally, I can passthrough SPDIF perfectly. I am successfully monitoring SPDIF stream parameters.

But TXSTATSRC and TXVAL_OVWR appear to be completely non functional. Nothing I do ever changes a single status bit. I have tried hundreds of combinations of settings. The bitstream is completely untouched.

cirrus have not responded to technical questions.

I am beginning to suspect TXSTATSRC / TXVAL_OVWR were never implemented, perhaps someone at wolfson got nervous at the idea of someone possibly using the wm8804 as an scms stripper and yanked the functionality completely.

Has anyone ever successfully used TXSTATSRC / TXVAL_OVWR to modify the channel status data of passthrough SPDIF on this part?

I have an application where I need to clear the non-audio and validity bits in an SPDIF bitstream. I'm using the wm8804 in 3-wire i2c mode.

It was easy enough to get the wm8804 to passthrough SPDIF from RX0 to TX0 internally, I can passthrough SPDIF perfectly. I am successfully monitoring SPDIF stream parameters.

But TXSTATSRC and TXVAL_OVWR appear to be completely non functional. Nothing I do ever changes a single status bit. I have tried hundreds of combinations of settings. The bitstream is completely untouched.

cirrus have not responded to technical questions.

I am beginning to suspect TXSTATSRC / TXVAL_OVWR were never implemented, perhaps someone at wolfson got nervous at the idea of someone possibly using the wm8804 as an scms stripper and yanked the functionality completely.

Has anyone ever successfully used TXSTATSRC / TXVAL_OVWR to modify the channel status data of passthrough SPDIF on this part?

This may sound like a silly suggestion, compared to what it seems like you have already tried, but you have changed the status of the TXVAL_SF0/SF1 registers right?

well since the data sheet says TXVAL_OVWR uses the value of TXVAL_SF0 and TXVAL_SF1, I have of course changed them, to no effect whatsoever. They are completely ignored

and of course I have used SPDTX1 - 5 with TXSTATSRC as well.

do you have a wm8804 and have you successfully used this functionality?

According to the datasheet, when the TX is taking feed from the s/pdif receiver the validity bits recovered from the incoming s/pdif stream get forwarded to the transmitted s/pdif stream, regardless register values of TXVAL_OVWR, TXVAL_SF0, and TXVAL_SF1. What is required by your application could be done with a second WM8804 working as a s/pdif TX taking feed from the first wm8804 via the digital audio interface. Just a thought.

wonder if I can route RX0 -> AIFTX -> AIFRX -> TX0 ?

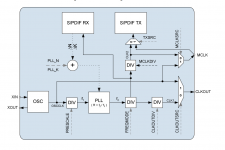

Smart one! Didn't think of that. However, there seems to be a problem with the master clock. When the s/pdif TX is taking feed from the AIF it anticipates a MCLK feed at the MCLK pin, that would require a clock signal of suitable frequency/phase (meaning associated with the incoming s/pdif stream) be sourced out of the WM8804 and be routed to the MCLK pin. The CLKOUT pin could be a souce of such clock signal but I have not gone far enough to make certain it will serve purpose.

Attachments

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.