I tried the single buffer by blocking the contact of pin10~13 on 7404 and there is definitely some improvement on the sound. The high & extreme high is more smooth now. I think the parallel output somehow impacts the performance of the clock. I have no equipment to prove it, but I can hear it.

Poting

Hi Poting ... thanks for the feedback. It would also be my guess that it somehow affects the sound - I just haven't had the time to make a listening setup so helpful with your feedback ;-)

Cheers,

Jesper

Hi Poting ... thanks for the feedback. It would also be my guess that it somehow affects the sound - I just haven't had the time to make a listening setup so helpful with your feedback ;-)

Cheers,

Jesper

Hi Jasper,

In my case, single buffer sounds better. I wish to hear more feedback from others. Before Andrea released his board, there was a discussion on this matter. I proposed PO74G38072A as the buffer. If you are about to design your clock board, you may consider a good clock buffer. It should have enough power to drive long cable.

Poting

@poting:

This is an interesting buffer, however, my guess is that it would still show extra noise on the VCC pins because it has two outputs. Even if there is no load on the output the logic still switches and causes noise on the VCC (& likely output?). I think the best would be a suitable (low phase noise) single gate IC that is not too small.

Thanks for the suggestion but I will place it in reasonable vicinity to the DAC/ADC so high drive capability should be less of an issue.

Cheers,

Jesper

... Yes, that could be fine to hear from others as well.I wish to hear more feedback from others.

I proposed PO74G38072A as the buffer.

This is an interesting buffer, however, my guess is that it would still show extra noise on the VCC pins because it has two outputs. Even if there is no load on the output the logic still switches and causes noise on the VCC (& likely output?). I think the best would be a suitable (low phase noise) single gate IC that is not too small.

It should have enough power to drive long cable.

Thanks for the suggestion but I will place it in reasonable vicinity to the DAC/ADC so high drive capability should be less of an issue.

Cheers,

Jesper

my guess is that it would still show extra noise on the VCC pins because it has two outputs. Even if there is no load on the output the logic still switches and causes noise on the VCC (& likely output?). I think the best would be a suitable (low phase noise) single gate IC that is not too small.

Hi Jasper,

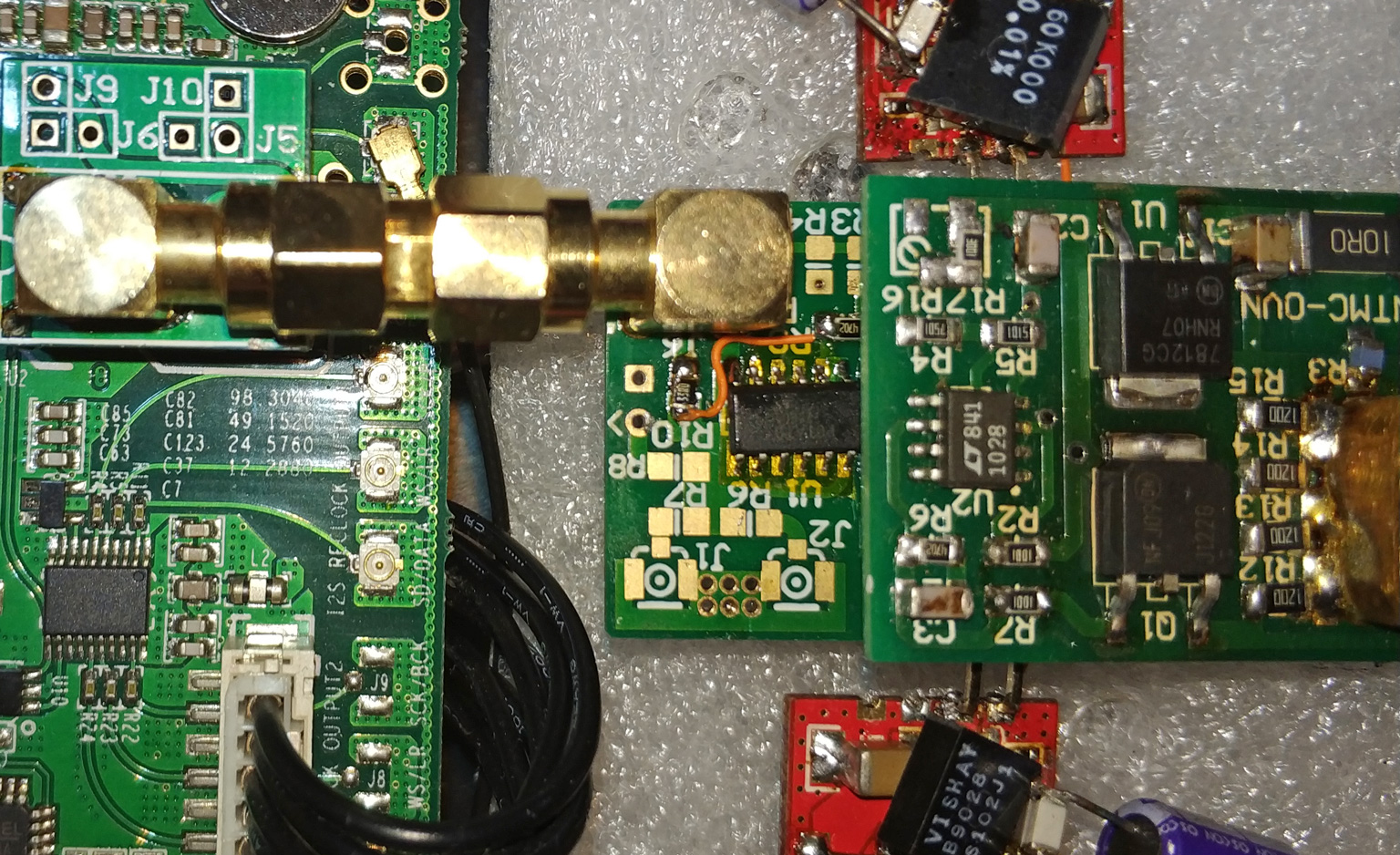

Thanks for the tip. This is my final "single buffer" mod on Andrea's Driscoll borad. Only one inverter is used. Other pins (except VCC, Gnd) are blocked by heat resistant tape underneath. My initial impression, this mod improves the sound even further. More depth, more defined layers of sound...etc. There was substantial change in sound when I listened to Adele's 21 album last night. Her voice was clearly separated from the background. There was no harsh on high and extreme high. The bass was solid and defined than before. Very interesting.

Poting

Hi Poting ... Thank you also for your feedback ... BTW - on a side note - my name is "Jesper" and not "Jasper" ... I know that in the English speaking countries it is often spelled Jasper but being Danish the spelling is different ;-)

One comment on the way you have made your modification: I personally would connect the inverter inputs that are not used to GND. It is not unusual that unused gate inputs - like inverter inputs - can shift between high and low even if there is no signal on them. This in turn would cause the outputs to also shift high & low somewhat randomly which again would lead to noise on VCC and possibly/likely the used inverter output.

BTW it looks as if you are using a Potatosemi inverter, right? Can I ask you if you are using the "GU04" or the "04"? And have you tried both?

Cheers,

Jesper

One comment on the way you have made your modification: I personally would connect the inverter inputs that are not used to GND. It is not unusual that unused gate inputs - like inverter inputs - can shift between high and low even if there is no signal on them. This in turn would cause the outputs to also shift high & low somewhat randomly which again would lead to noise on VCC and possibly/likely the used inverter output.

BTW it looks as if you are using a Potatosemi inverter, right? Can I ask you if you are using the "GU04" or the "04"? And have you tried both?

Cheers,

Jesper

Hi Jesper,

I apologized for the wrong spelling. ^_^

My picture was taken just right after I soldered the chip. The unused inputs are all connected to ground. Unfortunately, the 7404 is the buffered version. I heard that unbuffered version is better here. However, I acquired this chip more than 10 years ago from another project. Due to the small quantity and the shipping cost, I decided to use what I had in hand. Have you ever compared these two?

Poting

I apologized for the wrong spelling. ^_^

My picture was taken just right after I soldered the chip. The unused inputs are all connected to ground. Unfortunately, the 7404 is the buffered version. I heard that unbuffered version is better here. However, I acquired this chip more than 10 years ago from another project. Due to the small quantity and the shipping cost, I decided to use what I had in hand. Have you ever compared these two?

Poting

Typically the fastest gates will have the lowest additive phase noise. Adding a buffer stage will slow down the gate but may be necessary to drive the load. The Potato architecture is supposed to have significantly less noise induced into the supply. Still treat everything around these like a microwave circuit with small windows, differential signals where possible with carefully matched trace lengths and close continuous ground planes adjacent to the signals.

A common problem is supply modulation from data getting back to clock signals and buffers. Isolation is important, even a small inductor may be enough.

A common problem is supply modulation from data getting back to clock signals and buffers. Isolation is important, even a small inductor may be enough.

@Poting:

Hi Poting ... No, I have not yet compared the two. Hmmm ... when reading your post I wonder if you are aware of potatosemi's online store on ebay? Here most all of potatosemi's components can be bought at ~ 3 USD + a little less for shipping. Just FYI in case you didn't know.

Cheers,

Jesper

Unfortunately, the 7404 is the buffered version. I heard that unbuffered version is better here. However, I acquired this chip more than 10 years ago from another project. Due to the small quantity and the shipping cost, I decided to use what I had in hand. Have you ever compared these two?

Hi Poting ... No, I have not yet compared the two. Hmmm ... when reading your post I wonder if you are aware of potatosemi's online store on ebay? Here most all of potatosemi's components can be bought at ~ 3 USD + a little less for shipping. Just FYI in case you didn't know.

Cheers,

Jesper

@Demian,

Thanks for the tip on inductor. Andrea does include an inductor on VCC pin. I hope this will prevent the modulation.

@Jesper,

Yes, I found it and placed my order already. It seems they are sending the package from Taiwan, but I still have to pay the international shipping...

I will compare the two and report back. This is perhaps the most critical part of the entire audio system.

Poting

Thanks for the tip on inductor. Andrea does include an inductor on VCC pin. I hope this will prevent the modulation.

@Jesper,

Yes, I found it and placed my order already. It seems they are sending the package from Taiwan, but I still have to pay the international shipping...

I will compare the two and report back. This is perhaps the most critical part of the entire audio system.

Poting

Last edited:

Typically the fastest gates will have the lowest additive phase noise.

Where did you get this?

Because they convert the noise from DC to daylight into jitter?

Adding a buffer stage will slow down the gate but may be necessary to drive the load. The Potato architecture is supposed to have significantly less noise induced into the supply.

What do you think is the Potato architecture?

It is nothing but ordinary CMOS on a contemporary process and

a huge amount of spec massaging.

From a buffer, I would expect that the output signal is somewhat stronger

than the signal that needs buffering. Those potato chips are not even strong

enough to drive another identical buffer without failing their oh so good specs.

Just compare the input load of the buffer/inverter and the allowed load capacitance

for full speed.

They could barely drive the 0.6 pF active probes of my sampling scope if you

take the board pad capacitance into account.

That is nothing an advanced Texas Inst. 74LVC could not equal.

Just think for a moment why you cannot get them at DigiKey

but only on ebay.

Still treat everything around these like a microwave circuit with small windows, differential signals where possible with carefully matched trace lengths and close continuous ground planes adjacent to the signals.

A common problem is supply modulation from data getting back to clock signals and buffers. Isolation is important, even a small inductor may be enough.

Sigh.

Gerhard

Last edited:

RE: speed and phase noise, from https://www.researchgate.net/profil...icting-noise-and-jitter-in-CMOS-inverters.pdf

"Equation (13) shows that faster transistors will have less

jitter essentially because faster slew rates will reduce the

noise to jitter conversion. Scaling is intended to be done in

such way that speed continues to increase each new

generation and thus jitter is expected to decrease."

He goes on to say that there is a trade out with supply noise.

RE: Potato stuff. I have never tried them but the docs suggest a different layout and circuit in the chip to reduce the supply noise. The details they presented looked legit. However I don't know of any actual comparisons. The claims in the specs (.9 nS switching) is significantly faster than most CMOS but 2 pF load cap is quite a limitation if you are trying for GHz speeds. I don't think that's relevant for any audio stuff.http://www.potatosemi.com/potatosemiweb/image/Techfile2010.pdf

It looks like this http://www.ti.com/lit/ds/symlink/sn74aucu04.pdf could get you to similar speeds but not compatible with 3.3V logic and a DIY hostile package. Not sure what other stuff is available that is that fast.

"Equation (13) shows that faster transistors will have less

jitter essentially because faster slew rates will reduce the

noise to jitter conversion. Scaling is intended to be done in

such way that speed continues to increase each new

generation and thus jitter is expected to decrease."

He goes on to say that there is a trade out with supply noise.

RE: Potato stuff. I have never tried them but the docs suggest a different layout and circuit in the chip to reduce the supply noise. The details they presented looked legit. However I don't know of any actual comparisons. The claims in the specs (.9 nS switching) is significantly faster than most CMOS but 2 pF load cap is quite a limitation if you are trying for GHz speeds. I don't think that's relevant for any audio stuff.http://www.potatosemi.com/potatosemiweb/image/Techfile2010.pdf

It looks like this http://www.ti.com/lit/ds/symlink/sn74aucu04.pdf could get you to similar speeds but not compatible with 3.3V logic and a DIY hostile package. Not sure what other stuff is available that is that fast.

I don't think transistors speed is that important in a squarer made with an unbuffered inverter. Unbuffered means a single stage, voltage gain is not very high, output dv/dt is input dv/dt x voltage gain and input is low dv/dt sinus.

The switching speed limit is not the transistor.

The input dv/dt should as high as possible, so should be the input voltage swing. Stop just before protective diodes conduction. Step up transformer is a good option.

Power supply noise is very important because of voltage dependant parasitic capacitor and because output voltage is just the switched power voltage. The squarer should have is own low noise supply

I haven't tested potato's inverter but both input voltage increase and power supply noise can give good sound improvements.

Joël

The switching speed limit is not the transistor.

The input dv/dt should as high as possible, so should be the input voltage swing. Stop just before protective diodes conduction. Step up transformer is a good option.

Power supply noise is very important because of voltage dependant parasitic capacitor and because output voltage is just the switched power voltage. The squarer should have is own low noise supply

I haven't tested potato's inverter but both input voltage increase and power supply noise can give good sound improvements.

Joël

Second option: you could replace C1 and C3 with trimmer capacitors (2-15pF) and then you have to tune these to see if the oscillator starts correctly. Finally you can measure the capacitance of the trimmer capacitors and replace them with fixed type.

Third option: keep all original component values and place an inductor with a value around 1 or 1.2 uH in series between C2 and ground.

Anyway take care to set R11 to get half VCC at Q1 collector.

Hi Andrea,

Instead of 45.1584Mhz, I'm building the 49.152Mhz SC-Cut Droscoll this time. The recommended value yields the strange 17.xx Mhz on my crystal. (Isn't it supposed to be the third-overtone mode?) I tried the second option, no help. The third option didn't work at all. It won't oscillate. Playing with C3, and it will only affect the Vpp. BTW, my Q1 is BFR182. Any suggestions?

Poting

Hi Andrea,

Instead of 45.1584Mhz, I'm building the 49.152Mhz SC-Cut Droscoll this time. The recommended value yields the strange 17.xx Mhz on my crystal. (Isn't it supposed to be the third-overtone mode?) I tried the second option, no help. The third option didn't work at all. It won't oscillate. Playing with C3, and it will only affect the Vpp. BTW, my Q1 is BFR182. Any suggestions?

Poting

Hi Poting,

if you have one on the shelf, please replace the BFR182 with the MMBT5179.

Andrea

Hi Poting,

if you have one on the shelf, please replace the BFR182 with the MMBT5179.

Andrea

Hi Andrea,

Tried MMBT5179 (Mouser) already. Just like before. No oscillation at all. There are few components which are not from the BOM or Mouser. They are SMD resistors, 1N5711, BFR182, and 100nf NP0/C0G MLCCs. I just ordred the NE85633 from eBay, but I have a feeling that Q1 may not be the cause. It seems I am the only one having this issue. Very strange.

Poting

Hi Andrea,

Tried MMBT5179 (Mouser) already. Just like before. No oscillation at all. There are few components which are not from the BOM or Mouser. They are SMD resistors, 1N5711, BFR182, and 100nf NP0/C0G MLCCs. I just ordred the NE85633 from eBay, but I have a feeling that Q1 may not be the cause. It seems I am the only one having this issue. Very strange.

Poting

It seems that teh MMBT5179 had not enough gain to evercome the losses of the crystal. BTW, it's very strange that it oscillates at 17MHz, since the Driscoll is tuned around the 3rd overtone frequency. It could be oscillate at B-Mode (10% over the tuned frequency) but not at fundamental.

Did you set Q1 collector at half Vcc?

Did you set Q1 collector at half Vcc?

Yes, I was using a pot at first. The required resistance is 63.5K, but I put a 62K SMD which is the closest I have at hand. I got same 17.xx Mhz frequency before and after. I will try to de-solder every part and measure them on my LCR meter. BTW, the max Vpp set by C3 is about 600mv only which is much less than my 24M version.

Poting

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Line Level

- The Well Tempered Master Clock - Building a low phase noise/jitter crystal oscillator