> As the sim showed even variations of 5% in hfe didn´t increase THD considerably.

Unless we have made some very stupid mistakes.......

We have tried all combinations bu changing each of Q1 to Q4 by 5%. Irrespective of what Q2 & Q3 does, every time when we change Q4 by 5% and keep Q1 unchanged, or vice versa, we get THD 0.019%. I also find it difficult to understand, but I have no time to figure it out right now.

Patrick

Unless we have made some very stupid mistakes.......

We have tried all combinations bu changing each of Q1 to Q4 by 5%. Irrespective of what Q2 & Q3 does, every time when we change Q4 by 5% and keep Q1 unchanged, or vice versa, we get THD 0.019%. I also find it difficult to understand, but I have no time to figure it out right now.

Patrick

Hi,

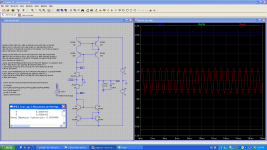

for a higher precision of the THD analysis the command .plotwinsize=0 should be set.

This switches off the data compression feature of LTspice.

EUVLs sim missed on this command and I was able to verify his high THD-figures by removing this command from my simulation.

In #62 I included the LTspice file to verify or falsify the sims. As one can see, I used the same models and variations.

Funny thing... with the plowinsize command set and Q1 (or Q4 in EUVLs schematic) varyed, the THD-figures were the lowest of all transistor combinations (0.000314% -110dB).

jauu

Calvin

for a higher precision of the THD analysis the command .plotwinsize=0 should be set.

This switches off the data compression feature of LTspice.

EUVLs sim missed on this command and I was able to verify his high THD-figures by removing this command from my simulation.

In #62 I included the LTspice file to verify or falsify the sims. As one can see, I used the same models and variations.

Funny thing... with the plowinsize command set and Q1 (or Q4 in EUVLs schematic) varyed, the THD-figures were the lowest of all transistor combinations (0.000314% -110dB).

jauu

Calvin

Last edited:

We can send them all to Jan Didden for audition.....

Patrick

I have an even better idea. I will be at Stuarts' house with a few more very critical and accomplished listeners mid-October. We can do an informal (or even formal) listening session then. If Stuart has time, of course. Never know with those VP's

jan

We have spiced a modified version of Joachim's circuit with complementary input FETs, Wilson current mirrors and fixed rails.

With 1mA input and 2.7k R_iv, THD is 0.039%.

The model used identical BJTs in both current mirrors (i.e. perfect match).

We'll test hardware when proto PCB is ready.

Patrick

.

With 1mA input and 2.7k R_iv, THD is 0.039%.

The model used identical BJTs in both current mirrors (i.e. perfect match).

We'll test hardware when proto PCB is ready.

Patrick

.

Attachments

Last edited:

- Home

- Source & Line

- Digital Line Level

- Zen -> Cen -> Sen, evolution of a minimalistic IV Converter