here's your best friend when dealing international:

Google Translate

Although I do suspect that he is fluent in her majesty's language...

Google Translate

Although I do suspect that he is fluent in her majesty's language...

yeah i'm aware of the google service  although the other day it didnt seem to be working properly on that site it was today though, in that particular google translate way.

although the other day it didnt seem to be working properly on that site it was today though, in that particular google translate way.

However I was joking, sometimes, some Europeans respond better to those who can speak the language

However I was joking, sometimes, some Europeans respond better to those who can speak the language

Thanks GeorgeI posted mechanicals for the S/PDIF Board on the Group Buy thread. It's post #632 on September 9, 2012. Please use these with caution. I am not an ME; not even close. When I used these to make my case, I had to make liberal use of a file to get things to fit properly. Whatever you do, don't send them to Front Panel Express and expect joy. My suggestion would be to use the drawings to make a mock-up out of heavy paper, test it, and make adjustments before a drill bit touches metal.

Best regards,

George

Your are really helpful here.

With some files and a cup of beer, here is what i got

Attachments

Off topic: FooMote- Control Foobar2000 from your Android phone or tablet

I have been looking for Foobar2000 remote control for a long time. I’m not happy with all the stuffs I’ve tried including some remote desktops until yesterday I found this FooMote.

FooMote Banamalon

To set up it is very easy

1. Go to Foobar2000 official website download the foo-httpcontrol plug-in, copy the extracted .dll into foobar2000 component folder.

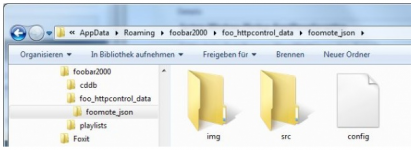

2. Download foomote_json template, create foomate_json folder in the foobar2000 foo_httpcontrol_data folder, than copy the extracted xx folder into that folder

Please note the foo_httpcontrol_data is a system hiden folder, to located it you have to find it by searching %APPDATA%/foobar2000 at Windows7 search

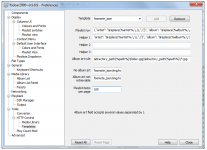

3. Run foobar2000 and configure the plug-in as picture below, confirm to allow win7 firewall not to block it. You have to input the IP of the foobar2000 computer

5. At your Android, go to google play find and download foomote, it’s free! Open it. It will locate your foobar2000 server. OK, now you can enjoy your super remote control from your Android phone or big screen tablet.

Some basic requirements,

1, WIFI

2, Both Android and foobar2000 computer have to access network form same router or within same LAN segment

Please refer this link for details:

FooMote - Banamalon

Have fan!

Ian

I have been looking for Foobar2000 remote control for a long time. I’m not happy with all the stuffs I’ve tried including some remote desktops until yesterday I found this FooMote.

FooMote Banamalon

To set up it is very easy

1. Go to Foobar2000 official website download the foo-httpcontrol plug-in, copy the extracted .dll into foobar2000 component folder.

2. Download foomote_json template, create foomate_json folder in the foobar2000 foo_httpcontrol_data folder, than copy the extracted xx folder into that folder

Please note the foo_httpcontrol_data is a system hiden folder, to located it you have to find it by searching %APPDATA%/foobar2000 at Windows7 search

3. Run foobar2000 and configure the plug-in as picture below, confirm to allow win7 firewall not to block it. You have to input the IP of the foobar2000 computer

5. At your Android, go to google play find and download foomote, it’s free! Open it. It will locate your foobar2000 server. OK, now you can enjoy your super remote control from your Android phone or big screen tablet.

Some basic requirements,

1, WIFI

2, Both Android and foobar2000 computer have to access network form same router or within same LAN segment

Please refer this link for details:

FooMote - Banamalon

Have fan!

Ian

Attachments

Last edited:

Hi Ian

After elevating my DAC thanks to Your amazing FiFo into level I never expected... I have started to look at ways of improving rest of my system

and now I'm fighting with my speakers....

To make long story short, have question.

Any chance to have 2 of Your FiFo-Reclock set-ups running the same input I2S data but with ability to delay one FiFo output at some time, like 50-250us. Some way to run second FiFo in kind of "slave mode" with fixed time delay to "master".

Then of cause the same, but just time delayed I2S data goes to 2 DACs and 2 Amps.

I'm thinking about possibility of using Your FiFo to delay Tweeter to Midwoofer in loudspeaker.

Getting nice XO slopes and crossing points in loudspeakers are pretty easy, but getting "time coherent" is usually bit problematic in most loudspeaker designs.

Any possibility that this could be done with current FiFo hardware?

Best Regards

Rosendorfer

After elevating my DAC thanks to Your amazing FiFo into level I never expected... I have started to look at ways of improving rest of my system

and now I'm fighting with my speakers....

To make long story short, have question.

Any chance to have 2 of Your FiFo-Reclock set-ups running the same input I2S data but with ability to delay one FiFo output at some time, like 50-250us. Some way to run second FiFo in kind of "slave mode" with fixed time delay to "master".

Then of cause the same, but just time delayed I2S data goes to 2 DACs and 2 Amps.

I'm thinking about possibility of using Your FiFo to delay Tweeter to Midwoofer in loudspeaker.

Getting nice XO slopes and crossing points in loudspeakers are pretty easy, but getting "time coherent" is usually bit problematic in most loudspeaker designs.

Any possibility that this could be done with current FiFo hardware?

Best Regards

Rosendorfer

Rosendorfer,

I'm sure Ian will respond in time, but I just want to mention that there has been machinations for a fully multichannel capable FIFO, begging from a few. I believe there is technical hurdles in making the master/slave.

I wouldn't recommend using the FIFO delay as a delay between two speakers for time alignment of drivers. The delay is dependent on the sample rate of the playback media so the delay is less for 192kHz than 44.1kHz for example. Also the delay is actually fluctuating within tolerances of the memory buffer due to long term variance of the clocks on either side of the FIFO. For this reason I don't think the FIFO delay is appropriate for that application.

A DSP module, followed by a multichannel FIFO reclocker and multichannel DACs would acheive what you want though. There are still technical details to be managed, including the need to have filter coefficients at every sample rate or re-sample the input to a fixed sample rate for use inside the DSP.

I'm sure Ian will respond in time, but I just want to mention that there has been machinations for a fully multichannel capable FIFO, begging from a few. I believe there is technical hurdles in making the master/slave.

I wouldn't recommend using the FIFO delay as a delay between two speakers for time alignment of drivers. The delay is dependent on the sample rate of the playback media so the delay is less for 192kHz than 44.1kHz for example. Also the delay is actually fluctuating within tolerances of the memory buffer due to long term variance of the clocks on either side of the FIFO. For this reason I don't think the FIFO delay is appropriate for that application.

A DSP module, followed by a multichannel FIFO reclocker and multichannel DACs would acheive what you want though. There are still technical details to be managed, including the need to have filter coefficients at every sample rate or re-sample the input to a fixed sample rate for use inside the DSP.

As far as I can see, the solution could be a simple shift register on the Data stream of the I2S AFTER the fifo. It should not jeopardize the jitter reduction of the FIFO as it is Wclk and Bclk (depending on the DAC chip) that must be held jitter free as far as possible.

Koldby

Koldby

Dear Hochopeper

I know that my English sometimes could be not very easy to understand,

so I will try to refresh my "idea"..

Well first, I'm fully aware that in current firmware state FiFo delay is dependant on many factors and it is not my intention to use uncontrolled FiFo delay to achieve anything...

This what I'm thinking about is "idea" of using second FiFo hardware, means current gen PCB, memory and FPGA controller, but with new! firmware to delay I2S stream but in controlled and defined way.

Well I'm just thinking about: First FiFo with no changes, is doing all of hard job it is doing now and second "FiFo hardware" with new firmware just delays at programmable! time I2S stream taken from output of First FiFo and sends it to second Reclock board.

Well of cause we would need to have a way of being able to program the delay, as different speaker arrangements needs different delays,

This what I'm looking into is probably bit strange mix of traditional analogue speaker XO's with "good old caps" and inductors to get the crossing points and slopes and have the freedom of being able play "time alignment" of speakers in digital domain.

I have been playing with my speakers for last few months, and seems to me that this could be pretty interesting solutions.

And as for waiting for "planed" multichanel FiFo to be working with DSP..... I'm sure that this is extremely interesting stuff, and probably many guys using DSP's are waiting for that....

But my idea is much simpler and fundamentally different thing.

I'm looking for some help with "time" in digital domain but do not want go full blown DSP.

And there are not that many ways to have programmable time delay, bit perfect! and "jitter free" second I2S stream.

So maybe this possibly could be interesting and just new Ian FiFo feature.

And as for Koldby idea of simple buffer or shift register.

Well, been thinking about that and again not an expert, but for me it seems that "simple shift register on the Data stream" would be OK if we were not into all of that HiRes stufff and different Fs like: 44,1k ; 48k, 88,2k, 96k, and so on, That makes simple shift register bit tricky, our buffer have to be aware what frequency we are playing and have to adjust buffer length to keep delay constant for all frequencies.

But again, maybe all we need is something much simpler than FiFo and Ian in his free time

could come out with some small Add On card that could be doing simple time delay job.

could come out with some small Add On card that could be doing simple time delay job.

Anyway not sure if that could be interested for anyone, but well why not ask.

Best Regards

Rosendorfer

I know that my English sometimes could be not very easy to understand,

so I will try to refresh my "idea"..

Well first, I'm fully aware that in current firmware state FiFo delay is dependant on many factors and it is not my intention to use uncontrolled FiFo delay to achieve anything...

This what I'm thinking about is "idea" of using second FiFo hardware, means current gen PCB, memory and FPGA controller, but with new! firmware to delay I2S stream but in controlled and defined way.

Well I'm just thinking about: First FiFo with no changes, is doing all of hard job it is doing now and second "FiFo hardware" with new firmware just delays at programmable! time I2S stream taken from output of First FiFo and sends it to second Reclock board.

Well of cause we would need to have a way of being able to program the delay, as different speaker arrangements needs different delays,

This what I'm looking into is probably bit strange mix of traditional analogue speaker XO's with "good old caps" and inductors to get the crossing points and slopes and have the freedom of being able play "time alignment" of speakers in digital domain.

I have been playing with my speakers for last few months, and seems to me that this could be pretty interesting solutions.

And as for waiting for "planed" multichanel FiFo to be working with DSP..... I'm sure that this is extremely interesting stuff, and probably many guys using DSP's are waiting for that....

But my idea is much simpler and fundamentally different thing.

I'm looking for some help with "time" in digital domain but do not want go full blown DSP.

And there are not that many ways to have programmable time delay, bit perfect! and "jitter free" second I2S stream.

So maybe this possibly could be interesting and just new Ian FiFo feature.

And as for Koldby idea of simple buffer or shift register.

As far as I can see, the solution could be a simple shift register on the Data stream of the I2S AFTER the fifo. It should not jeopardize the jitter reduction of the FIFO as it is Wclk and Bclk (depending on the DAC chip) that must be held jitter free as far as possible.

Koldby

Well, been thinking about that and again not an expert, but for me it seems that "simple shift register on the Data stream" would be OK if we were not into all of that HiRes stufff and different Fs like: 44,1k ; 48k, 88,2k, 96k, and so on, That makes simple shift register bit tricky, our buffer have to be aware what frequency we are playing and have to adjust buffer length to keep delay constant for all frequencies.

But again, maybe all we need is something much simpler than FiFo and Ian in his free time

Anyway not sure if that could be interested for anyone, but well why not ask.

Best Regards

Rosendorfer

Rosendorfer,

Your english is great, really! But thank-you for re-iterating and clarifying a few of your thoughts, an interesting idea.

The idea is to duplicate each L/R signal, produce a 4ch i2s output from 2ch, with two of the channels delayed. ie L, L-delay, R, R-delay?

The problem is that re-clocking still needs to be the final stage, any delay and other functions need to happen before that, the same way as the I2S to PCM adapter is added to the chain prior to reclocking. The solution you're suggesting needs 4channels of i2s reclocking, which I don't think is possible without redesign of the clock board(s).

Cheers,

Chris

Your english is great, really! But thank-you for re-iterating and clarifying a few of your thoughts, an interesting idea.

The idea is to duplicate each L/R signal, produce a 4ch i2s output from 2ch, with two of the channels delayed. ie L, L-delay, R, R-delay?

The problem is that re-clocking still needs to be the final stage, any delay and other functions need to happen before that, the same way as the I2S to PCM adapter is added to the chain prior to reclocking. The solution you're suggesting needs 4channels of i2s reclocking, which I don't think is possible without redesign of the clock board(s).

Cheers,

Chris

the fifo doesnt know what time it is in an absolute sense, only that time is passing, there is also no means of syncing 2 boards, I asked about this possibility long ago, but with them synced and me doing crossover and phase alignment on the computer. they need to be able to be synchronized in order to delay one a specific/constant amount.

it seems like a LOT of trouble to go to for something that would really IMO be better done in DSP anyway, in fact it would be trivial. I would certainly prefer the multichannel fifo done first

it seems like a LOT of trouble to go to for something that would really IMO be better done in DSP anyway, in fact it would be trivial. I would certainly prefer the multichannel fifo done first

the fifo doesnt know what time it is in an absolute sense, only that time is passing, there is also no means of syncing 2 boards, I asked about this possibility long ago, but with them synced and me doing crossover and phase alignment on the computer. they need to be able to be synchronized in order to delay one a specific/constant amount.

The point here is that you could duplicate L/R. The problem is that you need a new reclocking board to enable that.

A single delay board could be programmed to have delay with time represented as number of samples at each sample rate, and sit in the system like the I2S to PCM board, I can see how that could work. The problem with Rosendorfer's variation is the re-clocking stage, it would need a multichannel re-clocking stage.

I think it would need either a mutlichannel FIFO+Reclock, or a new intermediate board and new multichannel reclock board.

it seems like a LOT of trouble to go to for something that would really IMO be better done in DSP anyway, in fact it would be trivial. I would certainly prefer the multichannel fifo done first

I agree!

maybe you should read my post again  I know very well what he could do, if we had the power t just pretend that hardware exists, I asked about doing it more than a year ago... my dacs are duplicated L/R, pretty logical progression to want to duplicate fifo L/R, but I didnt want to use delay, just access to 4 channels of buffer/reclock, which brings us to...

I know very well what he could do, if we had the power t just pretend that hardware exists, I asked about doing it more than a year ago... my dacs are duplicated L/R, pretty logical progression to want to duplicate fifo L/R, but I didnt want to use delay, just access to 4 channels of buffer/reclock, which brings us to...

The problem with Rosendorfer's variation is the re-clocking stage, it would need a multichannel re-clocking stage.

maybe you should read my post againI know very well what he could do, if we had the power t just pretend that hardware exists, I asked about doing it more than a year ago... my dacs are duplicated L/R, pretty logical progression to want to duplicate fifo L/R, but I didnt want to use delay, just access to 4 channels of buffer/reclock, which brings us to...

I'll open a new thread for the multi-channel DSD/I2S FIFO project soon. It would be totally a different project because of the architecture.

I'm super busy recently to release a new product line for my boss...

Ian

I'll open a new thread for the multi-channel DSD/I2S FIFO project soon. It would be totally a different project because of the architecture.

I'm super busy recently to release a new product line for my boss...

Ian

Wow, I knew you had been thinking about it Ian, I didn't realise it was so close. Work is important, please make sure you're able to keep your hobby projects fun and without pressure or rush!!

I'll open a new thread for the multi-channel DSD/I2S FIFO project soon. It would be totally a different project because of the architecture.

I'm super busy recently to release a new product line for my boss...

Ian

Ian, I hope you didnt read that the wrong way, I know it'll come when it comes, i'm in no huge rush, but this news does make me happy

my reference to bringing it up a year ago was not a hurry up, just reminding that i've covered pretty much this exact scenario before long ago

- Home

- Source & Line

- Digital Line Level

- Asynchronous I2S FIFO project, an ultimate weapon to fight the jitter