I have another solution which I’m using right now to power the dual XO board: Remove the two on board LDO and short the input and output with two 0 ohm 0805 jumpers (resistor). Then power the dual xo clock board with one 3.2V LiFePO4 battery cell (I’m having a passive battery management board now) from J5 DC input port, but you need an isolator board to avoid short with the FIFO power otherwise you have to remove L11.

Ian

I will implement this mod when I receive the isolator board. Ian, you always have great idea!!!

The new designed Si570 clock board has an optional 3P 2.54 (diyAudio standard J )power supply port which could bypass the on-board LDO and hookup a customized external low noise regulator or a battery based power supply to achieve better performance.

Ian

Is there any output headers on the new clock board for sampling frequencies?

Ian

Is there any output headers on the new clock board for sampling frequencies?

I'm trying to add something to the Si570 driver to make it open to third party software accessing the frequency control via a USART. That port could also be isolated by the optional isolator reserved on the isolator PCB.

That interface port already been left on PCB. Protocol will be provided once I'm done.

Ian

Last edited:

I'm trying to add something to the Si570 driver to make it open to third party software accessing the frequency control via a USART. That port could also be isolated by the optional isolator reserved on the isolator PCB.

That interface port already been left on PCB. Protocol will be provided once I'm done.

Ian

Ian,

I am waiting with excitement to a new clock board. If I could suggest / ask - it would be great to have an output buffer included with several outputs. If one wants to send clock signal to two DAC boards and to the source, that is already three, plus one to S/PDIF board, that is four. I do not know what is the effect on jitter, I am sure it does add some, but it seems that our contemporary systems will dramatically benefit if your clock is feeding all of the units. In the ideal system, in my mind, all units will work in a synchronous mode to your Big Ben

Also, I am assuming / hoping to see a group buy for new units - battery management board, isolation board and new clock board. I will patiently wait.

that request is already covered afaik =)

Not quite, Ian's covered isol and battery boards being ready for next GB after some other officework is completed, no mention of Si570 GB though yet, I've asked in the other thread about that though

Not quite, Ian's covered isol and battery boards being ready for next GB after some other officework is completed, no mention of Si570 GB though yet, I've asked in the other thread about that though

thats not what I mean, I refer to the request for more than one output buffer channel for MCLK, which was one of my first requests.

I saw your post over there, with the usual surface level analysis from the peanut gallery

thats not what I mean, I refer to the request for more than one output buffer channel for MCLK, which was one of my first requests.

Ah, now I get it. Yeah, I'm not sure if there was quite that many mclk outputs from memory, Ian did cover it for dual mono though.

Actually, now you've made me think about it qusp, you've made my brain hurt and in the process have an idea.

AR2, there is little point in making the source an i2s slave with this FIFO I'd think. Also it would kill the benefit of having the isolator board in the system too

i'm only referring to the 2 main outputs for dual dacs. yes i've already had that brain explosion explaining this to others in the past so left it to you, thanks!

yes the source slaving is, as we've mentioned before in here; counter-productive...it doesnt work, we have a buffer and its necessitated delay AR2 remember? =) there is no benefit to syncing a transport etc.

clock outputs from the fifo in current form are

1 sent back to the spdif input board from the fifo board directly over the ribbon

1 from the main clock board, which has 2 outputs

I requested a second buffered clock output from the main clock board on the si570, not sure its been done, but i'd say so I think.. cant remember; I followed up on that a few weeks back but cant remember the response.

yes the source slaving is, as we've mentioned before in here; counter-productive...it doesnt work, we have a buffer and its necessitated delay AR2 remember? =) there is no benefit to syncing a transport etc.

clock outputs from the fifo in current form are

1 sent back to the spdif input board from the fifo board directly over the ribbon

1 from the main clock board, which has 2 outputs

I requested a second buffered clock output from the main clock board on the si570, not sure its been done, but i'd say so I think.. cant remember; I followed up on that a few weeks back but cant remember the response.

The Dual XO Clock Board already has the XO standby control logic included. If you are running two CCHD951, one is working and the other one will be put into standby mode. Tentclock is the only one exception which doesn’t come with a disable control.

Ian

Hi Ian

Just silly me....

I will not try to be that "smart" again....

Rosendorfer

Hi Ian

Just silly me....

I will not try to be that "smart" again....

Rosendorfer

Hi Rosendorfer, please keep your good job, no need worry about the board, I can fix it anyway

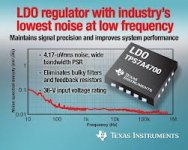

If it is possible, try this one, TPS7A4700, it's the best low noise LDO so far. glt also recomended on his website.

Ian

Attachments

Ian,

I am waiting with excitement to a new clock board. If I could suggest / ask - it would be great to have an output buffer included with several outputs. If one wants to send clock signal to two DAC boards and to the source, that is already three, plus one to S/PDIF board, that is four. I do not know what is the effect on jitter, I am sure it does add some, but it seems that our contemporary systems will dramatically benefit if your clock is feeding all of the units. In the ideal system, in my mind, all units will work in a synchronous mode to your Big Ben. Would love to have your opinion.

Also, I am assuming / hoping to see a group buy for new units - battery management board, isolation board and new clock board. I will patiently wait.

Hi AR2,

You will have three u.fl MCLK output sockets from the new Si570 clock board. All of them come from a dedicate clock fan out buffer with only 29fs additive jitter. Furthermore, there will be three additional u.fl socket footprints for another group of I2S signals, which will work for your dual mono setup

Si570 is the best solution so far I could touch to drive the ESS9018 DAC at sync mode with frequencies up to 90.xxx and 98.xxx MHz. I have been running the new designed 570 clock board for a whole week. I know CCHD957 is 4dB better at close in phase noise(@100Hz), but I almost couldn't come back to CCHD957 45.xxx and 49.xxx MHz on my system. (will share the result later on

I'm not sure if I have chance running a GB for the Si570 clock board. It will be up to how many people are interested in it. Si570 will be very expensive if purchases quantity below 50 (I'm using free samples now

Ian

Last edited:

I'm not sure if I have chance running a GB for the Si570 clock board. It will be up to how many people are interested in it. Si570 will be very expensive if purchases quantity below 50 (I'm using free samples now). I noticed some people predicted Si570 is not suitable for digital audio applications. I pay respect to their point. Just feel a little bit unfair, they even didn’t ever try it. [/FONT][/COLOR]

Ian

Ian

Shall we start a list showing our interest in the Si570 clock board?

1. bigpandahk

Si570 Clock Board interesting list

Thank bigpandahk, glad you are interested in the Si570 clock board. I'd like to give a try, you can put your name on the list now. I'll try my best to make the the GB running.

1. bigpandahk

Ian

Shall we start a list showing our interest in the Si570 clock board?

Thank bigpandahk, glad you are interested in the Si570 clock board. I'd like to give a try, you can put your name on the list now. I'll try my best to make the the GB running.

1. bigpandahk

Thank bigpandahk, glad you are interested in the Si570 clock board. I'd like to give a try, you can put your name on the list now. I'll try my best to make the the GB running.

1. bigpandahk

2. tagheuer

Si570 interest list:

1. bigpandahk

2. tagheuer

3. hochopeper

I have also put an index in the Si570 thread refering to the posts that are most relevant to demonstrating Ian's development of this device, hopefully this lets people avoid need to ask questions that already have answers buried in this thread.

1. bigpandahk

2. tagheuer

3. hochopeper

I have also put an index in the Si570 thread refering to the posts that are most relevant to demonstrating Ian's development of this device, hopefully this lets people avoid need to ask questions that already have answers buried in this thread.

- Home

- Source & Line

- Digital Line Level

- Asynchronous I2S FIFO project, an ultimate weapon to fight the jitter