Yes please -I think your FIFO right justified 24bit output plan will be widely appreciated.

......

If you can add USB input it would be perfect for me?

Thanks for your amazing work so far.

Kazap said it perfect, I was just going to post the same things

Hi Ian,

can I use your FIFO kit from CD PRO I2S to a pair (stereo) of PCM63?

If yes, what I need? 1 I2S FIFO KIT and 1 DUAL XO CLOCK BOARD?

Also, can I interface I2S FIFO with NPC SM5843?

Andrea

Hi Andrea,

You can feed I2S signal from CD PRO into I2S FIFO. But the output is still I2S. PCM63s do not accept I2S, You need a little converter board which we are talking about. I didn't go deep into SM5843, does it support I2S input?

Regards,

Hi Andrea,

You can feed I2S signal from CD PRO into I2S FIFO. But the output is still I2S. PCM63s do not accept I2S, You need a little converter board which we are talking about. I didn't go deep into SM5843, does it support I2S input?

Regards,

Oops.. I wrote SM5843 but I meant SM5842, a digital filter 8-times oversampling (384fs for SM5842AP). I read from datasheet about data format:

Input data format

• 2s complement, MSB first

- LR alternating, 16/18/20/24-bit serial, trailing

data

- LR alternating, 24-bit serial, leading data

- LR simultaneous, 24-bit serial, leading data

Do you think that I2S FIFO can feed it directly?

BTW if I decide to make non oversampling DAC with a pair of PCM63 I'm interesting to directly interface them.

About CD PRO: I'm planning to build 2 separate box, one for transport and one for DAC, so you say that I can take I2S signal directly from CD PRO. right?

One more question: taking directly I2S data from CD PRO, do I need any reclocking in transport to avoid jitter? Would it be redundant?

Andrea

Oops.. I wrote SM5843 but I meant SM5842, a digital filter 8-times oversampling (384fs for SM5842AP). I read from datasheet about data format:

Input data format

• 2s complement, MSB first

- LR alternating, 16/18/20/24-bit serial, trailing

data

- LR alternating, 24-bit serial, leading data

- LR simultaneous, 24-bit serial, leading data

Do you think that I2S FIFO can feed it directly?

BTW if I decide to make non oversampling DAC with a pair of PCM63 I'm interesting to directly interface them.

About CD PRO: I'm planning to build 2 separate box, one for transport and one for DAC, so you say that I can take I2S signal directly from CD PRO. right?

One more question: taking directly I2S data from CD PRO, do I need any reclocking in transport to avoid jitter? Would it be redundant?

Andrea

Hi Andrea,

1. For sure, you can take I2S signals from CD Pro and you don't need any re-clocking before feeding into FIFO. It is 'redundant'

2. Interfacing I2S with PCM63, you have to use a little converter board. PCM63 do not directly support i2S.

3. From 5842 doc, I found it do not support i2S input. It's kind of 'SONY' format. In this case, maybe you need a special version of FIFO to output that format.

Hi Andrea,

3. From 5842 doc, I found it do not support i2S input. It's kind of 'SONY' format. In this case, maybe you need a special version of FIFO to output that format.

I think the 5842 outputs a sony version but inputs I2s. I say this because I built a DAC with CS8412 to 5842 with the cs8412 configured with M0,M2,M3 grounded and M1+5V which is the I2s output mode of the CS8412 ?

..... with 128Fs MCLK, theoretically it could go up to 768Khz, but I don't have anything to test so far. Do you know which USB could go up to 768Khz?....

That's an impressive indication of potential high performance for your FIFO. Thanks!

..... Do you know which USB could go up to 768Khz?....

I believe the Phasure is the trail blazer in this area:

Phasure NOS1 24/768 async USB DAC

with 24/768 async USB DAC interface to PCM1704 and a special software filter to reduce artefacts its a brilliant design.

I think your timing diagram for the AD DAC's look good, Ian.

If I might suggest one more thing:

Would it be possible to create a second DATA line per channel, which has the bits inverted?

Would be cool...easening a balanced DAC design. PCM1704 adopters don't need it though....

If I might suggest one more thing:

Would it be possible to create a second DATA line per channel, which has the bits inverted?

Would be cool...easening a balanced DAC design. PCM1704 adopters don't need it though....

Hi Andrea,

1. For sure, you can take I2S signals from CD Pro and you don't need any re-clocking before feeding into FIFO. It is 'redundant'. Because FIFO will isolate all the input jitter.

2. Interfacing I2S with PCM63, you have to use a little converter board. PCM63 do not directly support i2S.

3. From 5842 doc, I found it do not support i2S input. It's kind of 'SONY' format. In this case, maybe you need a special version of FIFO to output that format.

Can you implement that format?

I would like to buy the kit to feed SM5842, in oversampling PCM63 DAC.

Andrea

I think your timing diagram for the AD DAC's look good, Ian.

If I might suggest one more thing:

Would it be possible to create a second DATA line per channel, which has the bits inverted?

Would be cool...easening a balanced DAC design. PCM1704 adopters don't need it though....

Hi my friend. We got same idea! I was planning to include inverted data signals for both of the channel just in case somebody need running the DAC at mono mode. I'll use a 8 bit low jitter GHZ flip-flop for re-clocking which will have enough lines for all the signals.

Cheers,

Can you implement that format?

I would like to buy the kit to feed SM5842, in oversampling PCM63 DAC.

Andrea

Hi Andrea,

I'm thinking about out how to upgrade the verilogHDL software of my FIFO. Which will include the optional left-justify(sony format) output for working with some digital filter. The optional left-justify and right-justify input, maybe. Just hope it could catch up with the second GB run. Hardware will keep no change.

Regards,

Great![...]I was planning to include inverted data signals for both of the channel just in case somebody need running the DAC at mono mode.[...]

Isn't that a bit dangerous regarding cross coupling of the signals, and introducing jitter this way?[...]I'll use a 8 bit low jitter GHZ flip-flop for re-clocking which will have enough lines for all the signals.[...]

For the data lines, i see no problem at all, but for LE and BCK perhaps?

Hi Andrea,

I'm thinking about out how to upgrade the verilogHDL software of my FIFO. Which will include the optional left-justify(sony format) output for working with some digital filter. The optional left-justify and right-justify input, maybe. Just hope it could catch up with the second GB run. Hardware will keep no change.

Regards,

Ian,

I would like to order FIFO kit, but I'm a bit confused.

As I said I want to feed FIFO kit directly from CD PRO I2S, then I would like to take I2S output and MCLK and feed digital filter NPC SM5842.

You tell me that SM5842 do not accept I2S format data, while Rregal in a previous post said that it can do it.

I found on the web the attached schematics that interface I2S with 5842, so I believe you're right.

BTW do you think that I can feed 5842 using this schematics?

If yes, do I need FIFO board only?

What frequency oscillator?

Anyone can help me?

Thanks in advance

Andrea

Attachments

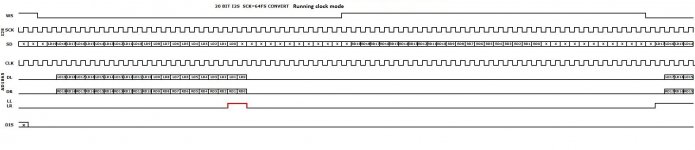

They look good to me.I attatched the updated timing plots, taking example for both AD1865 and PCM17xx. Let me know for any problem.

*please don't care about the LL,LR signals at the next word, I forgot changing them on the plots.

I don't want to split hairs about stop clock mode of PCM17XX but during conversion of a PCM1704 the clock will still run. To have a non-plus-ultra converter another stop clock timing is needed where the bit clock is stopped 2 cycles after the latch goes down, I think.

One more note: for the running clock mode I think the attached timing is good for all the mentioned DACs. What do you think?

I almost forgot I would also need and inverted data signal as the single ended preamp after my I/V inverts the phase. Nice idea to support it

Thanks.Zsolt

Attachments

Some hair splitting to prevent confusion about formats: the sony format is right-justified format (aka LSB-Jusitifed). I checked several digital filters and at least the Nippon Precision's SM58XX, DF1704 and PMD100 support this right-justified format.Hi Andrea,

I'm thinking about out how to upgrade the verilogHDL software of my FIFO. Which will include the optional left-justify(sony format) output for working with some digital filter. The optional left-justify and right-justify input, maybe. Just hope it could catch up with the second GB run. Hardware will keep no change.

Regards,

I wish I know Verilog/VHDL; it would had helped me alot

Not sure what you mean with running clock mode. The timing is OK, if you use right justified data.[...]One more note: for the running clock mode I think the attached timing is good for all the mentioned DACs. What do you think?[...]

But...for AD1865 and AD1862, I really would advise to stop the clock in any case before the LE line goes low. It will improve jitter performance and would be the preferred method when this logic is feeded with left justified I2S data (as is output from FIFO).

I meant a format with a continuously running bit clock, which is the basic operation mode of the DACs we discussed so far - that's why I think we should have it.Not sure what you mean with running clock mode. The timing is OK, if you use right justified data.

But...for AD1865 and AD1862, I really would advise to stop the clock in any case before the LE line goes low. It will improve jitter performance and would be the preferred method when this logic is feeded with left justified I2S data (as is output from FIFO).

- Home

- Source & Line

- Digital Line Level

- Asynchronous I2S FIFO project, an ultimate weapon to fight the jitter