yeah then the cap is not for the ADP151, but if you check the BOM (right next to the schematic), that position its also optionally a placement for TPS79333, for which pin 4 is the noise reduction/reference bypass pin. if you look at the schematic its also marked as NR, which gives us a clue.

I would have been very surprised if something like that got through Ians workflow, as annoying as that may be for us mere mortals haha

haha

I would have been very surprised if something like that got through Ians workflow, as annoying as that may be for us mere mortals

Last edited:

some useful link:

Techniques for Measuring Phase Noise

Converts an oscillator phase noise curve to jitter information

For a 22.5792 CCHD-957 crystal oscillator from its phase noise showed in the datasheet, the calculated RMS phase jitter is around 0.3ps. Assuming the theorical -6dB for half the frequency we get around 0.15ps at 11.2896MHz.

From the HCD661 11.2896MHz OCXO specs the calculated RMS phase jitter is

around 0.03ps.

That's the reason to feed directly the DAC chip from the MCLK.

For those who have not yet understood, no difference if the DAC chip is fed from the source rather than the FIFO buffer, feeding the DAC BCK directly from MCLK you reach the best performance in jitter reduction.

This way can be implemented both if you run the DAC directly from the source either if you use an asynchronous re-clocking such as the FIFO buffer.

qusp,

you are right, I meant "Steinway", and I don't own this piano, I can't afford it

BTW, not very difficult to listen to a live performance in a theatre, at least in my land

Techniques for Measuring Phase Noise

Converts an oscillator phase noise curve to jitter information

For a 22.5792 CCHD-957 crystal oscillator from its phase noise showed in the datasheet, the calculated RMS phase jitter is around 0.3ps. Assuming the theorical -6dB for half the frequency we get around 0.15ps at 11.2896MHz.

From the HCD661 11.2896MHz OCXO specs the calculated RMS phase jitter is

around 0.03ps.

That's the reason to feed directly the DAC chip from the MCLK.

For those who have not yet understood, no difference if the DAC chip is fed from the source rather than the FIFO buffer, feeding the DAC BCK directly from MCLK you reach the best performance in jitter reduction.

This way can be implemented both if you run the DAC directly from the source either if you use an asynchronous re-clocking such as the FIFO buffer.

qusp,

you are right, I meant "Steinway", and I don't own this piano, I can't afford it

BTW, not very difficult to listen to a live performance in a theatre, at least in my land

yeah then the cap is not for the ADP151, but if you check the BOM (right next to the schematic), that position its also optionally a placement for TPS79333, for which pin 4 is the noise reduction/reference bypass pin. if you look at the schematic its also marked as NR, which gives us a clue.

I would have been very surprised if something like that got through Ians workflow, as annoying as that may be for us mere mortalshaha

Thank you

I presumed that unconnected pin4 conceal some undocumented noise reduction function and never presumed some mistake made by Ian

some useful link:

Techniques for Measuring Phase Noise

Converts an oscillator phase noise curve to jitter information

For a 22.5792 CCHD-957 crystal oscillator from its phase noise showed in the datasheet, the calculated RMS phase jitter is around 0.3ps. Assuming the theorical -6dB for half the frequency we get around 0.15ps at 11.2896MHz.

From the HCD661 11.2896MHz OCXO specs the calculated RMS phase jitter is

around 0.03ps.

That's the reason to feed directly the DAC chip from the MCLK.

For those who have not yet understood, no difference if the DAC chip is fed from the source rather than the FIFO buffer, feeding the DAC BCK directly from MCLK you reach the best performance in jitter reduction.

This way can be implemented both if you run the DAC directly from the source either if you use an asynchronous re-clocking such as the FIFO buffer.

qusp,

you are right, I meant "Steinway", and I don't own this piano, I can't afford it

BTW, not very difficult to listen to a live performance in a theatre, at least in my land

same here, we have classical music performances 'down under' as well.... but the suggestion that it has anything to do with our discussion of a home audio system is the confusing part, especially since its plain you have never played one, or even seen one close up, or you would know how it was spelled.

One does not come close to replacing the other, you are listening to one now? you can listen while reading, while eating, while talking with friends, while relaxing with your cat, or other feline type obsession? ;p it can spit out a righteous distorted bassline? my desires are sometimes, but definitely not always so civilised.

the rest, I really dont know what you are getting at, or what relevance it has to this thread. it really seems as if its you that is struggling to understand the subtleties of the post you objected to, what the strict definition of synchronised is, or what your 'solution' implies that is simply not very interesting to most of us. many who chose the fifo, did so in order to avoid the very topology you are describing. I want that performance level with ALL of my sources

As you admit, its the same, yet you are stuck with a single transport, playing CDs.... and CD's only. or you are suggesting some sort of slave clock MUX? No...

you can hear the difference between 0-0.5ps?, that would cause giggles from my direction. At this level, the differences are academic and we all (should) know it.

anyway look can we please stop this, I shouldnt have replied to you, i'm being civil (or as much as I can manage while you are having these somewhat condescending overtones in your posting) but its really off topic and nobody wants to read it and the 'tit for tat' aspect is apparently what I was warned for just before.... it can go on forever and we will never agree, so lets agree to disagree yes?

StasioPe: speeds up to 384kHz are already supported with the right dac/clocks

Last edited:

Test1: WM8805 output MCLK jitter

....

Test2: MCLK jitter after FIFO

Hi Ian,

thanks for doing this, appreciate it. Got a question though -

Do you think doing the test on the bit or word clock would be more valuable than on the mclk ? Reason being mclk doesnt even pass through the fifo and fifo is like the "dut" of this test. Comapring the bit/word clock before and after would tell how much jitter it removed on those lines.

Right now its like comparing just the "good" clock (the actual clock) on the fifo board with the mclk coming out of wm8805.

Not that I am expecting any drastic difference in the result, but thinking maybe thats a more scientifically correct test ?

Just a thought...

Was browsing through the Cirrus site when I tripped across Cobra Net!

Why not use cobra net to stream audio rather than USB ??

There's a 2ch, an 8ch and a 16ch version available!

And samples are available on request!

because USB, ethernet etc has more than enough bandwidth, I already do 8 channel hires async on USB. cobranet is not a standard of any kind as yet, we need another fractured 'standard' like we need cancer to become contagious.

cobranet has been mentioned a few times here already, cant remember the issues, but there were a few besides the proprietary nature. having only the ability to connect devices you built yourself would be a pita.

no thanks

S/PDIF receiver SCK jitter measurement report:WM8805 vs. FIFO

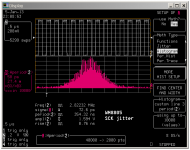

Test3: WM8805 output SCK jitter

Testing setup:

Jitter display: 50ps/DIV

see the first picture for details

Testing result:

Period jitter RMS:72.6ps

Period jitter peak-to-peak:+-250ps

Jitter distribution: Gaussian

frequency: 2.82232MHz

Please see the second screen shot picture for details

Test4: SCK jitter after FIFO

Testing setup:

Feeding WM8805 I2S output into FIFO, and then measure the output SCK of the asynchronized I2S stream.

Oscillators on the dual xo clock board: onboard generic 11.2896MHz XO

FIFO running at *256Fs

Jitter display: 10ps/DIV

Please see the third picture for details

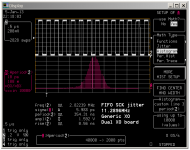

Testing result:

Period jitter RMS:5.988 ps

Period jitter peak-to-peak:+-21ps

Jitter distribution: Gaussian

frequency: 2.82239MHz

Please see the fourth screen shot picture for details

Test3: WM8805 output SCK jitter

Testing setup:

Jitter display: 50ps/DIV

see the first picture for details

Testing result:

Period jitter RMS:72.6ps

Period jitter peak-to-peak:+-250ps

Jitter distribution: Gaussian

frequency: 2.82232MHz

Please see the second screen shot picture for details

Test4: SCK jitter after FIFO

Testing setup:

Feeding WM8805 I2S output into FIFO, and then measure the output SCK of the asynchronized I2S stream.

Oscillators on the dual xo clock board: onboard generic 11.2896MHz XO

FIFO running at *256Fs

Jitter display: 10ps/DIV

Please see the third picture for details

Testing result:

Period jitter RMS:5.988 ps

Period jitter peak-to-peak:+-21ps

Jitter distribution: Gaussian

frequency: 2.82239MHz

Please see the fourth screen shot picture for details

Attachments

Test3: WM8805 output SCK jitter

...

Test4: SCK jitter after FIFO

Great! Did you by any chance happen to catch the spectral content of the jitter in both cases ? Was it random ? or periodic ? In band ? Out of band ?

Ian, very nice Results!

Do you think you can do better than 5 ps RMS? Isn't the jitter dominated by the flip flop?

Both CCHD957 and Si570 show less then 5ps RMS jitter on my scope, some times they can go below 4ps after long time run in. But I couldn't tell how good they are because of the 2ps jitter floor and other factors. Actually testing on a good clock is very difficult. But on a bad one is very easy

I've never seen jitter specs for flip flops, just people saying figures here and there with figures higher than jitter values of clocks.

flip-flop does add jitter to the secondary generation clock which is the output of the flip-flop. But not as much as I thought. Remember a RF engineer mentioned it add 6dB on phase noise each time going through a flip-flop. By figuring out from the added jitter number, I roughly estimated, on time domain, it adds no more than 1ps additive jitter reference to the father clock if using a decent flip-flop fast than 200Mhz with good power decoupling.

But the driving current and the load will make some change to the number.

To get more accuracy result, higher grade scope is required, such as 10G bandwidth with jitter package, or a signal analyzer

Regards,

Ian

What you need for more accuracy with you scope i describe in previous post. High bandwidth is not needed for jitter measurement (for audio equipment) at all.To get more accuracy result, higher grade scope is required, such as 10G bandwidth with jitter package,

PS And wm8804 MCLK output not designet to work on 50ohm load.

Last edited:

Ian, Your previous measurement with the generic 11.2896MHz XO showed jitter RMS to be 5.13 ps. Above, You state that with Si570 show less then 5ps and some times they can go below 4ps.

This does not seem like a big diff!? Or is Your measurement rig exhausted?

Can You do spectrum analysis?

A measurement comparing s/pdif in with s/pdif out using Your s/pdif board would be very interesting.

Really enjoying the sound coming out with the generic clock - "stability" kind of summarize it. (fed by a SB Touch)

- "stability" kind of summarize it. (fed by a SB Touch)

/

This does not seem like a big diff!? Or is Your measurement rig exhausted?

Can You do spectrum analysis?

A measurement comparing s/pdif in with s/pdif out using Your s/pdif board would be very interesting.

Really enjoying the sound coming out with the generic clock

/

come on man, keep up  did you read the post that contained that measurement or any of the subsequent posts? hell even the post those numbers were in. the measurement rig has a 2ps noise floor, so predictably the si570 has ~1.5-2ps jitter as expected plus the output buffer (or maybe with, Ian may clarify that if the output clock buffer on the si570 board was included in that measurement

did you read the post that contained that measurement or any of the subsequent posts? hell even the post those numbers were in. the measurement rig has a 2ps noise floor, so predictably the si570 has ~1.5-2ps jitter as expected plus the output buffer (or maybe with, Ian may clarify that if the output clock buffer on the si570 board was included in that measurement

I dont know what you would expect to learn from a spdif in and out comparison. the spdif TX will completely dominate the jitter, telling almost nothing about the fifo

I dont know what you would expect to learn from a spdif in and out comparison. the spdif TX will completely dominate the jitter, telling almost nothing about the fifo

Last edited:

OK qusp... but Ians statement about that he sometimes see 4 ps is unclear wrt if this is the meas rig in extra good condition or a happy moment for the DUT. Really, I'm trying to understand the difference between the si570 and the generic osc I'm listening to (ok, via s/pdif!) now.

I'm just curious what I'm feeding my DAC with, thats all.

/

I'm just curious what I'm feeding my DAC with, thats all.

/

OK qusp... but Ians statement about that he sometimes see 4 ps is unclear wrt if this is the meas rig in extra good condition or a happy moment for the DUT. Really, I'm trying to understand the difference between the si570 and the generic osc I'm listening to (ok, via s/pdif!) now.

I'm just curious what I'm feeding my DAC with, thats all.

/

Using s/pdif, I could probably not make use of a si570 based clock board...

But I'm planning to build me a new DAC. I would like a simple, balanced out 2 channel, ESS based with their dig. level control.

The question is just which one?

/

yeah if just using spdif, forget the si570, just stick a crystek in the clock board and be happy. the main benefits of the si570 are covering the full range of sample rates from 44.1->384 with nice low jitter as well as clean way to drive dual mono dacs.

he simply meant it measures 5ps but sometimes 4ps, maybe environmental or even thermal noise was higher when he got 5ps, but I think it has to be the si570 board in total, so that means the jitter is made up of 2ps noise floor plus the si570, plus the clock buffer. so I think its pretty much to spec, 1.5-2ps maybe lower for the si570 itself.

but one things for sure, these generic XOs are a surprise, totally useless for my purposes, but jeez not bad at all if you are playing 44.1

he simply meant it measures 5ps but sometimes 4ps, maybe environmental or even thermal noise was higher when he got 5ps, but I think it has to be the si570 board in total, so that means the jitter is made up of 2ps noise floor plus the si570, plus the clock buffer. so I think its pretty much to spec, 1.5-2ps maybe lower for the si570 itself.

but one things for sure, these generic XOs are a surprise, totally useless for my purposes, but jeez not bad at all if you are playing 44.1

Ian!

I sit here and enjoy the best sound I have ever had in my system. It improved even more after I took the leap and robbed my aTV from it's Toslink cable, exchanged the connection between the SB and your fifo. The cable change was inspired from one of your pictures of your DAC setup and it makes perfect sense with the fifo. I'm still on 44,1 and s/pdif but I have to say my system sounds lovely.

I just played Chopin, Krystian Zimerman – 4 Balladen • Barcarolle • Fantasie (DG 00289 477 9198)...

thanks and hats off Ian!

/

I sit here and enjoy the best sound I have ever had in my system. It improved even more after I took the leap and robbed my aTV from it's Toslink cable, exchanged the connection between the SB and your fifo. The cable change was inspired from one of your pictures of your DAC setup and it makes perfect sense with the fifo. I'm still on 44,1 and s/pdif but I have to say my system sounds lovely.

I just played Chopin, Krystian Zimerman – 4 Balladen • Barcarolle • Fantasie (DG 00289 477 9198)...

thanks and hats off Ian!

/

- Home

- Source & Line

- Digital Line Level

- Asynchronous I2S FIFO project, an ultimate weapon to fight the jitter