Two solutions even beginners should be able to manage. Although it may take a bit of luck to find two pairs with 1 % match from only six resistors.

Most multi-meters measure better in the upper region of each measuring range. Bringing the expected voltage drop into that range should yield even better results. The usual recommendation is to use the upper third of each measuring range for exact data.

Most multi-meters measure better in the upper region of each measuring range. Bringing the expected voltage drop into that range should yield even better results. The usual recommendation is to use the upper third of each measuring range for exact data.

A stereo pair of parallel chipamps requires a minimum of 4 output resistors.

Buy 6 (two go into stock) and series connect them using a 317 CCS passing 500mA. Set your DMM to 200.0mVdc and measure the voltage drop (~50.0mV) across each resistor.

Pick a pair that have as near as possible the same voltage drop. Now pick a second pair.

That will give you two pairs of near +-1% tolerance 0r1 resistors.

And the point of all that work towards getting such good tolerance output resistors is what exactly?

Spice analysis of the simplest AN-1192 parallel circuit

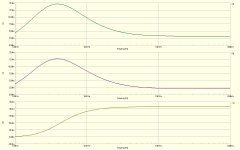

Here are some results from my analysis of the circuit given in figure 6 of AN-1192, page 8. In particular I was keen to explore how well the two amps share current at the extreme cases of all component tolerances giving the worst conditions, and at maximum output.

I ran a Spice simulation, using OP27's instead of LM3886s seeing, as far as I know, there are no official National Spice models of these amp chips. Because the OP27 model I used (provided as standard with my software package) has a current limit in keeping with the actual opamp capability, I scaled up the load impedances by a factor of 1000 so that 1mA in simulation became 1A in the real world. I didn't attempt to adjust the OP27 current limit to correspond to that on the LM3886. Unlike a real OP27, the Spice model appears to work happily at supplies of 35V I chose 0.1% gain resistors, 20% for the capacitor and 5% for the output sharing resistors, all at their extremes to make this a hideously worst case simulation.

I chose 0.1% gain resistors, 20% for the capacitor and 5% for the output sharing resistors, all at their extremes to make this a hideously worst case simulation.

Winding up the amplitude of the input source, it reached 1.55V peak just before the onset of clipping. The clipping voltage looked to be around 32V which is near enough to that on the LM3886 for a first stab. The high frequency (1kHz and above) sharing turned out about 3.4mA and 2.3mA, totalling 5.7mA into the load. Another, perhaps more helpful way of looking at this is to synthesise the equivalent resistive load each amplifier is seeing. In this condition, the higher gain amp (putting out 3.4mA) sees 6700ohms, the lower gain one, 9800 ohms (6.7 and 9.8 ohms in the real world). I consider this a reasonable match in the worst case for the higher frequencies even with 5% output sharing resistors.

In the real world this 5.7mA into the sim load corresponds to 5.7A and therefore, with a 4ohm load, 130WRMS. I doubt that a real pair of LM3886s would be able to achieve this continuously due to inadequate heatsinking, but in short bursts it might be quite feasible. The sharing resistors are dissipating 1.2W and 0.5W respectively under these conditions, so it looks as though 2W types will be adequate.

What happens at lower frequencies though is far from satisfactory. Due to the 20% capacitor tolerance, the gains deviate more strongly as the frequency drops from 1kHz, until at 20Hz, the currents in the sharing resistors become 5.9mA and 5mA. It seems at this point, with real LM3886s, the protection will certainly be activated - the amps are busy fighting each other. Put another way, the loads the two amps are now seeing are 3.8 ohms and 4.5 ohms - the benefits of adding a second paralleled amp have been completely lost. As the frequency descends still further, the amps will certainly go into total thermal shutdown - if they had unlimited current capability, a maximum output of 14A would be reached at the peak of 4Hz.

I'll go on to propose a fix for this problem in a subsequent post

Here are some results from my analysis of the circuit given in figure 6 of AN-1192, page 8. In particular I was keen to explore how well the two amps share current at the extreme cases of all component tolerances giving the worst conditions, and at maximum output.

I ran a Spice simulation, using OP27's instead of LM3886s seeing, as far as I know, there are no official National Spice models of these amp chips. Because the OP27 model I used (provided as standard with my software package) has a current limit in keeping with the actual opamp capability, I scaled up the load impedances by a factor of 1000 so that 1mA in simulation became 1A in the real world. I didn't attempt to adjust the OP27 current limit to correspond to that on the LM3886. Unlike a real OP27, the Spice model appears to work happily at supplies of 35V

Winding up the amplitude of the input source, it reached 1.55V peak just before the onset of clipping. The clipping voltage looked to be around 32V which is near enough to that on the LM3886 for a first stab. The high frequency (1kHz and above) sharing turned out about 3.4mA and 2.3mA, totalling 5.7mA into the load. Another, perhaps more helpful way of looking at this is to synthesise the equivalent resistive load each amplifier is seeing. In this condition, the higher gain amp (putting out 3.4mA) sees 6700ohms, the lower gain one, 9800 ohms (6.7 and 9.8 ohms in the real world). I consider this a reasonable match in the worst case for the higher frequencies even with 5% output sharing resistors.

In the real world this 5.7mA into the sim load corresponds to 5.7A and therefore, with a 4ohm load, 130WRMS. I doubt that a real pair of LM3886s would be able to achieve this continuously due to inadequate heatsinking, but in short bursts it might be quite feasible. The sharing resistors are dissipating 1.2W and 0.5W respectively under these conditions, so it looks as though 2W types will be adequate.

What happens at lower frequencies though is far from satisfactory. Due to the 20% capacitor tolerance, the gains deviate more strongly as the frequency drops from 1kHz, until at 20Hz, the currents in the sharing resistors become 5.9mA and 5mA. It seems at this point, with real LM3886s, the protection will certainly be activated - the amps are busy fighting each other. Put another way, the loads the two amps are now seeing are 3.8 ohms and 4.5 ohms - the benefits of adding a second paralleled amp have been completely lost. As the frequency descends still further, the amps will certainly go into total thermal shutdown - if they had unlimited current capability, a maximum output of 14A would be reached at the peak of 4Hz.

I'll go on to propose a fix for this problem in a subsequent post

Off the top of my head, no that won't work very well. It will cause a significant DC offset at the output in the worst case. Since the datasheet spec for the input offset voltage is 10mV max, multiplying this by 21 we get 210mV. Now if the two amps have opposite offsets (sods law), that's going to give us 420mV across the sharing resistors. In series they're 0.2R so that's a worst case standing current of 2.1A between the two amps - not very pleasant.

Yeah, the typical offset is 1mV according to the datasheet. However even with that low offset voltage, the quiescent dissipation in two paralleled chips isn't insignificant.

If using 35V rails, a 2mV offset between two amp chips will result in 210mA - this has to come from the 35V supplies, so each chip will be dissipating 7.4W.

I was just checking out some other 3886 paralleled designs - it seems the popular Jeff Rowland 3 * LM3886 paralleled amp (plenty of clones on eBay) uses a multiturn pot to trim the offset and dispenses with the capacitor, as you suggest. But they're using 0.2R sharing resistors, not 0.1R, so are somewhat less sensitive to offset.

You're getting 0.5mV at the output with a DC gain of 21 ? That would mean your input offset is only 24uV! Where d'you get your instrumentation grade amp chips? How does this offset vary with time and temperature?

How does this offset vary with time and temperature?

If using 35V rails, a 2mV offset between two amp chips will result in 210mA - this has to come from the 35V supplies, so each chip will be dissipating 7.4W.

I was just checking out some other 3886 paralleled designs - it seems the popular Jeff Rowland 3 * LM3886 paralleled amp (plenty of clones on eBay) uses a multiturn pot to trim the offset and dispenses with the capacitor, as you suggest. But they're using 0.2R sharing resistors, not 0.1R, so are somewhat less sensitive to offset.

You're getting 0.5mV at the output with a DC gain of 21 ? That would mean your input offset is only 24uV! Where d'you get your instrumentation grade amp chips?

Last edited:

is your intention to argue or to provide information?And the point of all that work towards getting such good tolerance output resistors is what exactly?

Are my suggestions wrong?

If so, then tell us what is wrong.

If they are helpful, then move on and tell us what we need to do.

The high frequency (1kHz and above) sharing turned out about 3.4mA and 2.3mA,

Pity that the simulation does not predict how the different current, hence different power dissipation affects the individual temperatures of the ICs, and how those different temperatures affect the circuit's performance.

at 20Hz, the currents in the sharing resistors become 5.9mA and 5mA.

At a first glance the relation 5,9:5=1,18 looks better than 3,4:2,3=1,48, though the question arises, why the current increases so much, when it should actually remain constant with resistive loads or fall slightly with a high-pass in place.

It seems at this point, with real LM3886s, the protection will certainly be activated - the amps are busy fighting each other.

Are they? So the load does not pass 10,9 mA at 20 Hz? How much current flows actually from one IC to the other then?

for a pair of parallel chipamps to give a maximum (short to medium term) power output of 130W, the current into the load must be 5.7Arms when passing a sinewave...............In the real world this 5.7mA into the sim load corresponds to 5.7A and therefore, with a 4ohm load, 130WRMS. I doubt that a real pair of LM3886s would be able to achieve this continuously due to inadequate heatsinking,

The peak current will be ~8Apk.

This is 4Apk per chipamp if the loading is equalised adequately. Well inside the 7A limit for Tc=25degC specified in the datasheet.

Keep the chips cool and they will pass that 130W to the 4r0 load in the short to medium term (1ms to 1s).

But that is not the main problem that the paralleled chipamps need to address.

It's the high peak currents that a 4ohm speaker may demand on fast starting or fast stopping transients.

These currents can approach (and even exceed) three times what the nominal resistive load would predict. Yes, a 4ohm speaker driven to 32Vpk may demand upto around 23Apk, this would need three parallel chipamps running cold to get anywhere close to meeting that transient demand if any of the chips starts to limit @~7Apk.

The 1% resistors you have on the boards are hardly matched. When you connect in parallel it's essential that the two amps are as alike as possible otherwise it will flow currents between the chips and they will get hot.Ok --

So really running the LM3886 in parallel is really a no brainer.

4 or 8 ohm speakers are fine with a 24vac transformer and really I don't see any need to change the feedback resistors that they have on the board for normal stereo operation -- I see they are 1% -- I imagine they're matched well.

Just put the .1 ohm 5 watts in series with each output and that's it.

And parallel the inputs of course.

If you have a DVM you can match 1% metal film resistors by hand pretty easily and the result will be pretty good but if you buy 0.1% resistors you don't have to think anything. They will work right away.

The value of the series resistor at the output is a trade off between current sharing and power dissipation at idle. The value should go bettween 0.2-0.3 ohms and up to 0.5 ohms if you don't care about the output impedance and power dissipation of those resistors. AN-1192 is a pretty good document after all.

pacificblue and abraxalito, shame on you guys.

Last edited:

Where d'you get your instrumentation grade amp chips?How does this offset vary with time and temperature?

Digikey standard parts

I might add that the input impedance when used this way needs to be as low as possible - I used 4.7K. Obviously this had issues with preamps preceding the amp, and that is why I now prefer to use more realistic resistor values...

I was looking at Carlos's schemes (this was four years ago, I forgot to mention that) when experimenting with resistor values, and it was not the 3886 but the 4766 (close enough). The CDP had a hell of a time into such a low input impedance, and one could hear it.

The DC gain was indeed 22-24 - 4.7K/220ohm and 2.2K/100ohm. I had issues with offset when raising input resistor beyond 10K, so we left it at 4.7K. Eventually discarded this totally and went back to 22K/1K/47uF.

is your intention to argue or to provide information?

In this particular instance, neither of your offered choices fits the bill. Got any others?

Are my suggestions wrong?

If so, then tell us what is wrong.

Not wrong as such, rather, misguided from my pov would be a more apt description. And I already have mentioned that 1% matching of the current sharing resistors isn't required in this application. Did you miss that? If you didn't miss it and you disagree then what are your reasons for disagreeing? This is a forum for such disagreements - I may well have missed something vital which renders my recommendation bunk.

If they are helpful, then move on and tell us what we need to do.

I'm always moving on, but unlike you, I'd not venture to tell you what you need to do. I'm making observations of rather suboptimal design decisions and suggestions to improve them. Its up to you whether you take on board those suggestions, but when you don't, I'm curious to learn why.

Welcome back to the fray, I thought you'd gone off in a huff.

Well thermal effects are not covered in Spice, you're quite correct. If they were, we'd need to know details about heatsinking, washers, clamps, airflows and the like, which will vary considerably from one implementation to the next. What kinds of thermal effects are you imagining might raise their ugly heads?

Yeah, I agree, the ratio current matching starts to look better at lower frequencies, but that's irrelevant. It looks better because current is now flowing between the ICs as much as flowing into the load. The current into the load does indeed remain constant, so a simple subtraction will show you what proportion of the total current is becoming a nuisance.

You're correct, the load does not pass 10.9A (in real life) at 20Hz. If it did, it would no longer be a 4R load, something closer to 2R I suspect as I found the frequency response is flat to this point. I'll leave the calculation of the current between the ICs to the reader Kirchoff's current law applies to the sharing node...

Kirchoff's current law applies to the sharing node...

Pity that the simulation does not predict how the different current, hence different power dissipation affects the individual temperatures of the ICs, and how those different temperatures affect the circuit's performance.

Well thermal effects are not covered in Spice, you're quite correct. If they were, we'd need to know details about heatsinking, washers, clamps, airflows and the like, which will vary considerably from one implementation to the next. What kinds of thermal effects are you imagining might raise their ugly heads?

At a first glance the relation 5,9:5=1,18 looks better than 3,4:2,3=1,48, though the question arises, why the current increases so much, when it should actually remain constant with resistive loads or fall slightly with a high-pass in place.

Yeah, I agree, the ratio current matching starts to look better at lower frequencies, but that's irrelevant. It looks better because current is now flowing between the ICs as much as flowing into the load. The current into the load does indeed remain constant, so a simple subtraction will show you what proportion of the total current is becoming a nuisance.

Are they? So the load does not pass 10,9 mA at 20 Hz? How much current flows actually from one IC to the other then?

You're correct, the load does not pass 10.9A (in real life) at 20Hz. If it did, it would no longer be a 4R load, something closer to 2R I suspect as I found the frequency response is flat to this point. I'll leave the calculation of the current between the ICs to the reader

for a pair of parallel chipamps to give a maximum (short to medium term) power output of 130W, the current into the load must be 5.7Arms when passing a sinewave.

The peak current will be ~8Apk.

This is 4Apk per chipamp if the loading is equalised adequately. Well inside the 7A limit for Tc=25degC specified in the datasheet.

Keep the chips cool and they will pass that 130W to the 4r0 load in the short to medium term (1ms to 1s).

Yep. Incidentally where did you get that the 7A current limit applies at Tc=25degC in the datasheet? I've looked but only see it specifies Ta=25degC above the table showing the current limit. Or are you assuming (fairly reasonably I think) that for short term pulses, Tc=Ta ?

But that is not the main problem that the paralleled chipamps need to address.

It's the high peak currents that a 4ohm speaker may demand on fast starting or fast stopping transients.

These currents can approach (and even exceed) three times what the nominal resistive load would predict. Yes, a 4ohm speaker driven to 32Vpk may demand upto around 23Apk, this would need three parallel chipamps running cold to get anywhere close to meeting that transient demand if any of the chips starts to limit @~7Apk.

Yep, I agree there's precious little margin in this design for driving real world speaker loads rather than resistors. If I was marketing a product based on this design, I'd only recommend an 8R load and quote the power into 8R only, sizing the power supply accordingly. Do you have a URL for your claim that currents can exceed 3X what the nominal resistive load may predict? I'd like to follow it up.

Is AN-1192 all its cracked up to be?

I'm intending to continue to show that its not half as good a document as you currently think.

I'm intending to continue to show that its not half as good a document as you currently think.

Hi,

I'm trying to make sense of the plots.

Top passes ~3mA, rms (ac) or pk?

Bottom passes ~2mA, rms (ac) or pk?

Are these both +ve , i.e. out to the load?

Power to the load ~100mW, requires 112mArms into 8r0.

But, 3mArms + 2mArms does not add up to 112mArms, even if both were positive.

I'm trying to make sense of the plots.

Top passes ~3mA, rms (ac) or pk?

Bottom passes ~2mA, rms (ac) or pk?

Are these both +ve , i.e. out to the load?

Power to the load ~100mW, requires 112mArms into 8r0.

But, 3mArms + 2mArms does not add up to 112mArms, even if both were positive.

pacificblue and abraxalito, shame on you guys.

Why on me? I have been defending it so far, because I think it serves its claimed purpose. For a different goal, you may certainly take different design decisions. abraxalito's ideas will be useful for those, who use turntables without rumble filter or listen to organ music or similar stuff with paralleled chipamps.

Do you have a URL for your claim that currents can exceed 3X what the nominal resistive load may predict? I'd like to follow it up.

AES E-Library: Peak Current Requirement of Commercial Loudspeaker Systems

Simulation plot discrepancies

The currents are RMS currents. As for the direction, I'm not sure that AC currents have a direction when expressed as RMS since in squaring, any sign will be lost.

Your error in calculation is to assume the load is 8 ohms, in the simulation its 4000 ohms. However the figure does not match the calculated 130W even when the correct load is used, I'm not entirely sure why this is. One possibility is that the RMS calculations used in the software are something of an approximation.

Hi,

I'm trying to make sense of the plots.

Top passes ~3mA, rms (ac) or pk?

Bottom passes ~2mA, rms (ac) or pk?

Are these both +ve , i.e. out to the load?

Power to the load ~100mW, requires 112mArms into 8r0.

But, 3mArms + 2mArms does not add up to 112mArms, even if both were positive.

The currents are RMS currents. As for the direction, I'm not sure that AC currents have a direction when expressed as RMS since in squaring, any sign will be lost.

Your error in calculation is to assume the load is 8 ohms, in the simulation its 4000 ohms. However the figure does not match the calculated 130W even when the correct load is used, I'm not entirely sure why this is. One possibility is that the RMS calculations used in the software are something of an approximation.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Chip Amps

- LM3886 x 2 in parallel