Hi Rfbrw,

thank you for reply.

i guess CDPRO2 is not so good as i think.

Can be converted in 64fs to take full advantage of octal D-I DAC?

Or better using SPDIF output?

Sorry my digital knowledge is not so good, but desire to built is strong.

Thank you in advance.

regards, Bostjan

thank you for reply.

i guess CDPRO2 is not so good as i think.

Can be converted in 64fs to take full advantage of octal D-I DAC?

Or better using SPDIF output?

Sorry my digital knowledge is not so good, but desire to built is strong.

Thank you in advance.

regards, Bostjan

Interfaces

Hi maxlorenz,

Thanks for your reply [post#471]

> I used the SPDIF interface, among I2S and USB to make the octal D-I DAC universal. I am going to use a mac with the USB to I2S converter module myself (I already received the PCM2706), this chip can be clocked externally (12MHz) for optimal performance. It uses the 16 bit I2S philips format, so I don't have to swap the timing chain module. Perhaps this is the most elegant way, just imagine many thousands of tracks can be played by the push of a button, with all information including CD cover photo on the screen, without swapping (and scratching) your CD's. When CD's are read using the "paranoia" mode, multiple reads make sure every last bit is recovered as good as possible. The CD images are stored on harddisk (Itunes) using lossless compression (approx. 250Mb/CD). A common 250Gb disc can theoretically hold about 1000 CD's this way! Back-up's can be made using a external USB / firewire disc with a similar capacity.

A number of transports are using the I2S sony format (24 bits, 48BCK / frame) this can be converted to 16 bit 48BCK / frame by using a delay circuit [post#466], thanks a333bt. The timing chain module can be swapped. So if necessary a timing-chain version based upon 48BCK with a integraded conversion circuit can be used instead. The 48BCK timing chain uses 0, 6, 12, 18, 24, 30, 36 and 42BCK delay, instead of multiples of 8BCK delay, SN74HCT164 can be used to provide these tap's. I am also looking at the possibility of using a one chip PLD based timing chain that supports both I2S formats.

> SPDIF sound quality, a remark often heared is that SPDIF degrades sound quality when compared to I2S, but there are lots of different SPDIF setups with different interface chips, cables, with or without transformers, with different loopback filter design, and then there is the critical PCB lay-out. So a realistic comparison is not that easy.

Hi maxlorenz,

Thanks for your reply [post#471]

> I used the SPDIF interface, among I2S and USB to make the octal D-I DAC universal. I am going to use a mac with the USB to I2S converter module myself (I already received the PCM2706), this chip can be clocked externally (12MHz) for optimal performance. It uses the 16 bit I2S philips format, so I don't have to swap the timing chain module. Perhaps this is the most elegant way, just imagine many thousands of tracks can be played by the push of a button, with all information including CD cover photo on the screen, without swapping (and scratching) your CD's. When CD's are read using the "paranoia" mode, multiple reads make sure every last bit is recovered as good as possible. The CD images are stored on harddisk (Itunes) using lossless compression (approx. 250Mb/CD). A common 250Gb disc can theoretically hold about 1000 CD's this way! Back-up's can be made using a external USB / firewire disc with a similar capacity.

A number of transports are using the I2S sony format (24 bits, 48BCK / frame) this can be converted to 16 bit 48BCK / frame by using a delay circuit [post#466], thanks a333bt. The timing chain module can be swapped. So if necessary a timing-chain version based upon 48BCK with a integraded conversion circuit can be used instead. The 48BCK timing chain uses 0, 6, 12, 18, 24, 30, 36 and 42BCK delay, instead of multiples of 8BCK delay, SN74HCT164 can be used to provide these tap's. I am also looking at the possibility of using a one chip PLD based timing chain that supports both I2S formats.

> SPDIF sound quality, a remark often heared is that SPDIF degrades sound quality when compared to I2S, but there are lots of different SPDIF setups with different interface chips, cables, with or without transformers, with different loopback filter design, and then there is the critical PCB lay-out. So a realistic comparison is not that easy.

mini clock upgrade

Hi tubee,

Thanks for your tip [post#463]

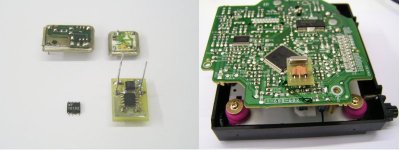

> No I didn't have enough space for a KC7 upgrade, I had to use a mini clock upgrade. Here is what I did, I gave a 20MHz crystal module (from an old network card) the EC designs demolition treatment. Inside the metal case was a small circuit board with a 8 pin WF10192 programmable SMD clock oscillator chip. So I designed a small circuit board, took the 16.9341MHz crystal from the sony and put everything together. Then I soldered the PCB very close to the CX2587Q Xtal input pin. I added some photographs. The sound quality has improved indeed, good tip.

WF10192 connections:

pin1: enable (leave open for normal operation), pin2: crystal, pin4: ground, pin5: output

pin7: crystal, pin8: +5V

only pin3 connected to ground: output divide by 2

only pin6 connected to ground: output divide by 8

both pin3 and pin6 connected to ground: output divide by 4

both pin3 and pin6 open: output equals crystal frequency.

> I2S interface, the sony has a plastic cover located exactly opposite to the chip (for service). I am going to put a 9 way sub-D connector and 3 differential RS422 drivers in that cover, so connections can be kept very short. Then I plan to run some tests with the modified timing chain for the sony I2S format.

Hi tubee,

Thanks for your tip [post#463]

> No I didn't have enough space for a KC7 upgrade, I had to use a mini clock upgrade. Here is what I did, I gave a 20MHz crystal module (from an old network card) the EC designs demolition treatment. Inside the metal case was a small circuit board with a 8 pin WF10192 programmable SMD clock oscillator chip. So I designed a small circuit board, took the 16.9341MHz crystal from the sony and put everything together. Then I soldered the PCB very close to the CX2587Q Xtal input pin. I added some photographs. The sound quality has improved indeed, good tip.

WF10192 connections:

pin1: enable (leave open for normal operation), pin2: crystal, pin4: ground, pin5: output

pin7: crystal, pin8: +5V

only pin3 connected to ground: output divide by 2

only pin6 connected to ground: output divide by 8

both pin3 and pin6 connected to ground: output divide by 4

both pin3 and pin6 open: output equals crystal frequency.

> I2S interface, the sony has a plastic cover located exactly opposite to the chip (for service). I am going to put a 9 way sub-D connector and 3 differential RS422 drivers in that cover, so connections can be kept very short. Then I plan to run some tests with the modified timing chain for the sony I2S format.

Attachments

Universal I2S interface schematics

Hi all,

Problem1: SPDIF jitters

Problem2: I2S comes in different formats (compatibility)

Problem3: How to transport I2S to a external DAC

Solution: Universal Philips I2S interface (can be added to almost every transport).

Basically SPDIF jitter occurs because both data and clock signals are mixed using Biphase Mark Code and then transported to the DAC by a optical, coax or differential interface cable of a few meters, jitter is added to the integrated clock signal by the varying data content.

So let's forget about SPDIF and move on to I2S,

What signals are present in almost every transport? SPDIF and the master clock (low jitter guido tent or elso kwak clock).

Now suppose the the audio interface chip (CS8412) was placed in, or very close to the transport instead of the DAC. It could be directly driven by the SPDIF output signal of the digital processor chip without using long cables or transformers. It would also automatically convert to philips I2S format (jumper settings). Then the icing on the cake, BCK, DATA and WS can be synchronously reclocked by the (low jitter) master clock that has a fixed phase relation to both WS and BCK. D-flipflops can be used for reclocking.

Now we have a universal very low jitter philips I2S interface in the transport. The 3 signals WS, BCK and DATA can be transported by using 3 differential RS422 interface drivers (1 X AM26LS31). On the receiving side (DAC) we use RS422 interface receivers (1 X AM26LS32), the lines can be terminated at the DAC side (54 Ohm). And why not use a standard cable available for this purpose: (screened) cat5 (4 X twisted pair) network cable. I am sure this will significantly reduce jitter as the transported clock signal is a non-modulated squarewave of a constant frequency. It will also solve I2S compatibility problems.

Oh, yes I already added a rough concept schematic diagram of this universal I2S interface. I am sure lots of improvements can be made, but it's a start.

Hi all,

Problem1: SPDIF jitters

Problem2: I2S comes in different formats (compatibility)

Problem3: How to transport I2S to a external DAC

Solution: Universal Philips I2S interface (can be added to almost every transport).

Basically SPDIF jitter occurs because both data and clock signals are mixed using Biphase Mark Code and then transported to the DAC by a optical, coax or differential interface cable of a few meters, jitter is added to the integrated clock signal by the varying data content.

So let's forget about SPDIF and move on to I2S,

What signals are present in almost every transport? SPDIF and the master clock (low jitter guido tent or elso kwak clock).

Now suppose the the audio interface chip (CS8412) was placed in, or very close to the transport instead of the DAC. It could be directly driven by the SPDIF output signal of the digital processor chip without using long cables or transformers. It would also automatically convert to philips I2S format (jumper settings). Then the icing on the cake, BCK, DATA and WS can be synchronously reclocked by the (low jitter) master clock that has a fixed phase relation to both WS and BCK. D-flipflops can be used for reclocking.

Now we have a universal very low jitter philips I2S interface in the transport. The 3 signals WS, BCK and DATA can be transported by using 3 differential RS422 interface drivers (1 X AM26LS31). On the receiving side (DAC) we use RS422 interface receivers (1 X AM26LS32), the lines can be terminated at the DAC side (54 Ohm). And why not use a standard cable available for this purpose: (screened) cat5 (4 X twisted pair) network cable. I am sure this will significantly reduce jitter as the transported clock signal is a non-modulated squarewave of a constant frequency. It will also solve I2S compatibility problems.

Oh, yes I already added a rough concept schematic diagram of this universal I2S interface. I am sure lots of improvements can be made, but it's a start.

Attachments

Re: Universal I2S interface schematics

Wrong. I2S, like I2C, comes in one format only.

The I2S Bus Specification.

-ecdesigns- said:Hi all,

Problem2: I2S comes in different formats (compatibility)

Wrong. I2S, like I2C, comes in one format only.

The I2S Bus Specification.

Hi EC, thanks for appreciating my tips about the cristal. You where offline a few days, "he's breeding and building on something again" i thought.

Well, how is sound improved?

If you want to feed the clock in a good way, its best to build a TL431 regulater with a BC5** transistor. I did this for a Tent XO, and this little circuit sounds better then the standard PS suggested by Guido (this one has a LM7808, i don't really like those 78** regs.) I searched for a schematic of it but its removed from the web. If you want to try this PS schematic, i will post a copy, have it on paper. Its very small, will fit in.

My family does like the upgrade of the 304 a lot, my wife, and later the housekeeper, turned their back when a CD of Frank Boeien, and Limb Biscuit, was playing. They said its like the instruments are in the room.

And i didn't do a lot on the 304.

We have a lot of the same thoughts: I have an old Philips 14bit CD300, it uses a 4.***Mhz cristal, i want to try an clock upgrade. So 2-3 weeks ago i have scavenged a cristal from an old PC ISA card with 16mHz freq. I grinded the top edges away on 3 sides to have a look in it. It has a chip and a cristal on a small ceramic pcb. I want to exchange the cristal eventually, not easy, it is suspended on two metal springs. My Marantz surround receiver will have a clock upgrade too in future.

Im glad you decided to go I2S, good decision

Well, how is sound improved?

If you want to feed the clock in a good way, its best to build a TL431 regulater with a BC5** transistor. I did this for a Tent XO, and this little circuit sounds better then the standard PS suggested by Guido (this one has a LM7808, i don't really like those 78** regs.) I searched for a schematic of it but its removed from the web. If you want to try this PS schematic, i will post a copy, have it on paper. Its very small, will fit in.

My family does like the upgrade of the 304 a lot, my wife, and later the housekeeper, turned their back when a CD of Frank Boeien, and Limb Biscuit, was playing. They said its like the instruments are in the room.

And i didn't do a lot on the 304.

We have a lot of the same thoughts: I have an old Philips 14bit CD300, it uses a 4.***Mhz cristal, i want to try an clock upgrade. So 2-3 weeks ago i have scavenged a cristal from an old PC ISA card with 16mHz freq. I grinded the top edges away on 3 sides to have a look in it. It has a chip and a cristal on a small ceramic pcb. I want to exchange the cristal eventually, not easy, it is suspended on two metal springs. My Marantz surround receiver will have a clock upgrade too in future.

Im glad you decided to go I2S, good decision

-ecdesigns- said:

So let's forget about SPDIF and move on to I2S,

A sentence or two later.

Now suppose the the audio interface chip (CS8412) was placed in, or very close to the transport instead of the DAC.

Do you not see the contradiction here?

It could be directly driven by the SPDIF output signal of the digital processor chip without using long cables or transformers. It would also automatically convert to philips I2S format (jumper settings). Then the icing on the cake, BCK, DATA and WS can be synchronously reclocked by the (low jitter) master clock that has a fixed phase relation to both WS and BCK. D-flipflops can be used for reclocking.

Now we have a universal very low jitter philips I2S interface in the transport. The 3 signals WS, BCK and DATA can be transported

What can you possibly want to connect to, where the above would be an advantage?

Just joined thread. kit using cdmpro2

Hi there

After reading this thread it is mouthwatering to have a setup which uses the tda1541a.. Doeas ec designs sell the boards for the following

I will get a cdm pro2 and want to use the i2s output into the dac then use a tube output stage..

WHat solution do you have to this ecdesigns, do you sell them or at least the pcb's (including the power supply boards)

Thanks

I live in Australia so USDollars will be cool and an address to send money to you if posssible

Thanks

Nick Mega

Hi there

After reading this thread it is mouthwatering to have a setup which uses the tda1541a.. Doeas ec designs sell the boards for the following

I will get a cdm pro2 and want to use the i2s output into the dac then use a tube output stage..

WHat solution do you have to this ecdesigns, do you sell them or at least the pcb's (including the power supply boards)

Thanks

I live in Australia so USDollars will be cool and an address to send money to you if posssible

Thanks

Nick Mega

Hi Nick,

If you read the earlier posts, the Octal DAC is not ready for sale yet. EC has not given an estimated date for completion or approximate cost, although you could probably assume it will be more expensive of the DIY DACs out there, given the parts and quality of the chassis involved. We're all anxiously waiting.

EC, would you be able to help Nick?

If you read the earlier posts, the Octal DAC is not ready for sale yet. EC has not given an estimated date for completion or approximate cost, although you could probably assume it will be more expensive of the DIY DACs out there, given the parts and quality of the chassis involved. We're all anxiously waiting.

EC, would you be able to help Nick?

Hi,

I think rfbrw has a good point here.

The I2S generator you specify will work, but maybe isn't the best choice.

Although you have the SPDIF converter close to the source (so less chance of errors being introduced), you're still multiplexing three signals into a single, selfclocking one, and then changing back. That will surely introduce issues?.

Wouldn't it be simpler to convert the sony format into I2S? Or better still, find a Philips based CDP for a transport?

Anyway, reclocking. I struggle to understand it at times. Is there an assumption that MCLK is greater than BCLK? Is BCLK completely divisible by MCLK. I can't get my head around what happens if the CLK that is clocking the flip flop occurs at an awkward time (like when the data or ws line is in transition to the next bit).

I'm sure this would never happen in reality, but it is possible. Am I worrying too much?

Also, I have all the bits now for the I2S RS422 driver and receiver. I've started building the driver board to go in the CD player. Need to order some DACs soon (won't be doing DI-DAC just yet, going to have a play first, but doing the differential I2S for sure).

Cheers,

Phil

I think rfbrw has a good point here.

The I2S generator you specify will work, but maybe isn't the best choice.

Although you have the SPDIF converter close to the source (so less chance of errors being introduced), you're still multiplexing three signals into a single, selfclocking one, and then changing back. That will surely introduce issues?.

Wouldn't it be simpler to convert the sony format into I2S? Or better still, find a Philips based CDP for a transport?

Anyway, reclocking. I struggle to understand it at times. Is there an assumption that MCLK is greater than BCLK? Is BCLK completely divisible by MCLK. I can't get my head around what happens if the CLK that is clocking the flip flop occurs at an awkward time (like when the data or ws line is in transition to the next bit).

I'm sure this would never happen in reality, but it is possible. Am I worrying too much?

Also, I have all the bits now for the I2S RS422 driver and receiver. I've started building the driver board to go in the CD player. Need to order some DACs soon (won't be doing DI-DAC just yet, going to have a play first, but doing the differential I2S for sure).

Cheers,

Phil

quote:

Originally posted by -ecdesigns-

So let's forget about SPDIF and move on to I2S,

A sentence or two later.

quote:

Now suppose the the audio interface chip (CS8412) was placed in, or very close to the transport instead of the DAC.

Do you not see the contradiction here?

quote:

It could be directly driven by the SPDIF output signal of the digital processor chip without using long cables or transformers. It would also automatically convert to philips I2S format (jumper settings). Then the icing on the cake, BCK, DATA and WS can be synchronously reclocked by the (low jitter) master clock that has a fixed phase relation to both WS and BCK. D-flipflops can be used for reclocking.

Now we have a universal very low jitter philips I2S interface in the transport. The 3 signals WS, BCK and DATA can be transported

What can you possibly want to connect to, where the above would be an advantage?

I'm working on a Philips CD624, it cost me £10 in a second hand shop. I also have a Marantz CD41 which (when you lift the hood) is as good as identical (which is good for spares etc).

The Marantz cost me £11 off of Ebay.

I think they both have CDM4s (the one with the swinging arm?).

The mechanics are much quieter than my later Marantz CD63 (although that's very quiet at the moment ) and they read CD-Rs very happilly.

) and they read CD-Rs very happilly.

I hope to get this diff I2S output going, and after the DAC is working, I'll fit a clock with less jitter, and one day upgrade the transport, if needs be.

Cheers,

Phil

The Marantz cost me £11 off of Ebay.

I think they both have CDM4s (the one with the swinging arm?).

The mechanics are much quieter than my later Marantz CD63 (although that's very quiet at the moment

) and they read CD-Rs very happilly.

) and they read CD-Rs very happilly.I hope to get this diff I2S output going, and after the DAC is working, I'll fit a clock with less jitter, and one day upgrade the transport, if needs be.

Cheers,

Phil

Hi Nick Mega

CDPRO-2M is a nice transport but be aware that rfbrw found that:

Here's what ecdesigns explained about D-I technique:

I hope the big brothers extend the sharing of their knowledge here

M.

PS: CDPRO has AES output also. Maybe it's better than SPDIF.

I will get a cdm pro2 and want to use the i2s output into the dac then use a tube output stage..

CDPRO-2M is a nice transport but be aware that rfbrw found that:

the CD Pro2 has an I2S option but BCK is 48Fs.

Here's what ecdesigns explained about D-I technique:

If I understood well, 48Fs is not high enough. Rfbrw commented about a way to increase it to 64Fs but I think it will be scarryTwin Direct Interpolation by parallelling DAC outputs: it uses the WS signal to split up the 64 BCK pulses long sample into two 32 BCK long samples DAC1 receives the standard signals and outputs L and R. DAC2 receives an inverted WS (wordselect) causing a 32 BCK long delay

I hope the big brothers extend the sharing of their knowledge here

M.

PS: CDPRO has AES output also. Maybe it's better than SPDIF.

philpoole said:Isn't AES/EBU just a (essentially) a differential variant of SPDIF?

I also think so...AES/EBU is a 'professional' SPDIF, think 110ohm and normally linked with XLR. But that's as far as my knowledge goes

Erik

maxlorenz said:If I understood well, 48Fs is not high enough. Rfbrw commented about a way to increase it to 64Fs but I think it will be scarry

No need to go from 48 to 64. Just use different shift register taps.

philpoole said:Isn't AES/EBU just a (essentially) a differential variant of SPDIF?

With different channel status flags, a much higher output level and balanced.

octal D-I DAC interface

Hi all,

Lots of discussions going on about interfaces and formats. I have been very busy with interface measurements and listening sessions, so I will reply to posts later. The following is very important.

Project news,

The clock upgrade and the universal I2S interface produced an improvement that really shocked me, I never expected such an improvement was even possible. The improvement was verified by other people that listened to this setup and could directly compare it with the "old" SPDIF setup. Also note that this interface outputs the PHILIPS FORMAT that is needed for the octal D-I DAC, so no further conversion is necessary. If your transport already outputs the philips format, the CS8412 is not necessary of course.

Here is what I personally can conclude from measurements and listening tests:

Never ever transport SPDIF over a longer cable (>20cm), it will have a very bad effect on sound quality. I am afraid, a similar effect would occur using USB, as this signal also carries both data and synchronization. In fact the PCM2706 datasheet already indicates a SpAct PLL circuit is used to recover a low jitter audio clock from the USB packet data.

The good news however is when the SPDIF / USB cable is kept very short and no transformers are used, things look quite different. So it's of paramount importance to put the SPDIF / USB receiver as close to the source as possible, then transport the generated I2S signal by using the differential interface. When reclocking can be applied as well, I2S performance can be obtained.

I am 100% convinced now transporting I2S using the differential interface, outperforms SPDIF by far.

Using a stable low jitter clock in the transport is a must.

Octal D-I DAC setup:

So this will have quite a impact on the octal D-I DAC setup. Now it will accept I2S with a differential interface exclusively, putting any other audio receiver in the DAC housing is useless when optimal sound quality has to be achieved, as the audio receiver now has to be placed close to the source, not close to or in the DAC.

During testing I used standard 3 meters long unshielded network cable, I also cascaded D-flipflops in the universal I2S interface (there were 3 unused). I also inverted MCK. I will post a new diagram soon, no optical isolation was used, only RS422 drivers and receivers. The DS8922 (4X) was used with 100 Ohm termination as the other chips didn't arrive today.

Hi all,

Lots of discussions going on about interfaces and formats. I have been very busy with interface measurements and listening sessions, so I will reply to posts later. The following is very important.

Project news,

The clock upgrade and the universal I2S interface produced an improvement that really shocked me, I never expected such an improvement was even possible. The improvement was verified by other people that listened to this setup and could directly compare it with the "old" SPDIF setup. Also note that this interface outputs the PHILIPS FORMAT that is needed for the octal D-I DAC, so no further conversion is necessary. If your transport already outputs the philips format, the CS8412 is not necessary of course.

Here is what I personally can conclude from measurements and listening tests:

Never ever transport SPDIF over a longer cable (>20cm), it will have a very bad effect on sound quality. I am afraid, a similar effect would occur using USB, as this signal also carries both data and synchronization. In fact the PCM2706 datasheet already indicates a SpAct PLL circuit is used to recover a low jitter audio clock from the USB packet data.

The good news however is when the SPDIF / USB cable is kept very short and no transformers are used, things look quite different. So it's of paramount importance to put the SPDIF / USB receiver as close to the source as possible, then transport the generated I2S signal by using the differential interface. When reclocking can be applied as well, I2S performance can be obtained.

I am 100% convinced now transporting I2S using the differential interface, outperforms SPDIF by far.

Using a stable low jitter clock in the transport is a must.

Octal D-I DAC setup:

So this will have quite a impact on the octal D-I DAC setup. Now it will accept I2S with a differential interface exclusively, putting any other audio receiver in the DAC housing is useless when optimal sound quality has to be achieved, as the audio receiver now has to be placed close to the source, not close to or in the DAC.

During testing I used standard 3 meters long unshielded network cable, I also cascaded D-flipflops in the universal I2S interface (there were 3 unused). I also inverted MCK. I will post a new diagram soon, no optical isolation was used, only RS422 drivers and receivers. The DS8922 (4X) was used with 100 Ohm termination as the other chips didn't arrive today.

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A