Thanks for this. It works. In order to get the expected run numbering, the .step statement for the parameter sweep has to be placed after the .step for the prb variable -- as you say, in the same text block.Seems there should be some neater way to parameterize this, so it's Tian(1) and Tian(2), but I haven't been able to make this work.

It's not clear to me exactly how and when the parameter substitutions are done but it seems arrays are after the simulation run.

And yes: I also cannot use a parameter to pass the @n specifications into the Tian function.

Matthias

Once upon a time, I implemented a simple recursive descent and also a YACC parser for a simulation tool front end. It was really fun to get a first touch on what informatics people do.

Last edited:

Hi David,

thanks again for the pointer.

This is a good comparison of the two approaches.

My impression is that our (at least my) intuitive way of thinking more corresponds to the control-centric approach. Sometimes, however, I also take the circuit analysis path, just in order to check intuition. See e.g. my two small excercises on the "integrator result" for NMC and TMC in the thread on NMC amplifier.

I see a similar issue with the analysis in Section IV. It requires some effort to correctly figure out the capacitive loading of input and output by the Miller capacitor C. To be honest, it is not obvious at all: why does C_2 appear at the left side of the transformed circuit, but C_1 doesn't appear on the right side (Figure 13)? And why does C appear twice with full value? Once this is done correctly, it is in fact easy and intuitive to draw and evaluate the loops.

Nice also to see the analysis of "our" TPC.

The trick in Figure 37 is an old friend of mine. I often tried something like that in order to squeeze some main loop phase margin out of the "VAS", without compromising the "VAS" stability too much. Both with and without TMC, I was never really content with the result. Maybe, I didn't play long enough with the three values.

Kind regards,

Matthias

thanks again for the pointer.

The best analysis of this that I have seen is >Here. "...Op-Amp Compensation, a Control-Centric Tutorial"

This is a good comparison of the two approaches.

My impression is that our (at least my) intuitive way of thinking more corresponds to the control-centric approach. Sometimes, however, I also take the circuit analysis path, just in order to check intuition. See e.g. my two small excercises on the "integrator result" for NMC and TMC in the thread on NMC amplifier.

I see a similar issue with the analysis in Section IV. It requires some effort to correctly figure out the capacitive loading of input and output by the Miller capacitor C. To be honest, it is not obvious at all: why does C_2 appear at the left side of the transformed circuit, but C_1 doesn't appear on the right side (Figure 13)? And why does C appear twice with full value? Once this is done correctly, it is in fact easy and intuitive to draw and evaluate the loops.

Nice also to see the analysis of "our" TPC.

The trick in Figure 37 is an old friend of mine. I often tried something like that in order to squeeze some main loop phase margin out of the "VAS", without compromising the "VAS" stability too much. Both with and without TMC, I was never really content with the result. Maybe, I didn't play long enough with the three values.

Kind regards,

Matthias

Last edited:

thanks...

Pleased to help. Must say I had mixed emotions when you said "It works". Did you expect otherwise?

my impression is that our (at least my) intuitive way... corresponds to the control-centric approach.

Certainly mine too.

I consider this like conservation laws in physics.

One can analyse proposed perpetual motion machines with much effort to find exactly where the mechanism won't work for each particular machine, or just use conservation of E. to reject them all at once.

A much deeper perspective.

On the topic of physics, I think that the discussion of just current gain or just volt gain in amplifier sections is incomplete, we need to consider what impedance they work into.

Maybe a simpler way is just to consider power gain at each point around the loop.

The loop gain is dimensionless so this makes sense.

Thus Paul's comment about the role of low current gain seems to miss some essential point.

It's yet another aspect that I still don't have quite clear, but I feel I move forward, even if slowly.

the trick in Figure 37 is an old friend of mine....I was never really content with the result.

I use this in my own development amp.

I believe it is theoretically "efficient", that it does not waste gain the way shunt compensation does.

There is a paper on "phantom zeros" that I believe is another name for this technique.

Unfortunately it is in some obscure(ish) IEEE conference in Scandinavia that it seems the library has not paid to access.

Are you an IEEE member? I would happily pay for the paper.

Otherwise I will try more at the university.

Best wishes

David

Last edited:

Sorry for the rather meagre answer. I was tired and just wanted to give some feedback.Pleased to help. Must say I had mixed emotions when you said "It works". Did you expect otherwise?

I'm not that euphoric here. Firstly, Lundberg's circuit transformation already requires understanding of the circuit. So the approach might be inappropriate for analysing something completely new. Secondly, he for instance had to make the important assumption that the stage's transconductance is large. When pushing things to the limits of devices, as we do here, then this might be misleading.I consider this like conservation laws in physics.

One can analyse proposed perpetual motion machines with much effort to find exactly where the mechanism won't work for each particular machine, or just use conservation of E. to reject them all at once.

A much deeper perspective.

To give an example: I'm always irritated by the influence of the base-spreading resistance in the "VAS" transistor. At high frequencies, it is basicly voltage-driven by the Miller capacitor and the buffer in the Darlington version. So, an additional low-pass is formed by base-spreading resistance and total junction capacity. It reduces stability margins in the "VAS" loop and influences the behaviour in the next-outer loop, if the ULGF there is high. [Sadly, this resistance is often not properly included in the transistor model, or it is quite high for the transistor I would like to use, e.g. BC546 for the "VAS" in a low-power amp.*] Such things cannot be understood by the simple model Lundberg proposes, and I assume that this is also the reason why I until now could not benefit from the trick of Figure 37.

The control-centric thinking is more intuitive, but in practice it relies on simplifications and has to be checked by other means.

Cannot really comment on this. I only remember that I initially had large problems to understand why a common-base configuration can make sense. Only after having tinkered with a radio-receiver front-end, I started to realise.Maybe a simpler way is just to consider power gain at each point around the loop.

The loop gain is dimensionless so this makes sense.

Thus Paul's comment about the role of low current gain seems to miss some essential point.

Kind regards,

Matthias

* I assume that the value RB=1 in the LtSpice library is more distant from reality than Bob Cordell's value of RB=150 for BC550, a figure also given in the Motorola data sheet.

Last edited:

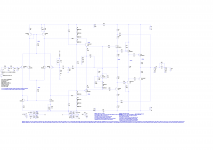

All quiet on the lunchtime front until I decided on a partial redesign.

Been trying to get stability into pure reactive loads of 1n to 100n. The first problem was the bootstrapping on the pre-drivers. This caused large phase twists that destroyed all PM and GM.

So the first change, move to a 3EF with bootstrapped pre-drivers. Bootstrapped to keep the VAS happier. There was an increase in THD without the bootstraps.

This certainly helped matters but stability was still an issue. So the next change was to work out which loop needed the most stability. Turns out to be the VAS loop (I think ) which has PM = 116 degrees and GM = 37dB.

) which has PM = 116 degrees and GM = 37dB.

Now we have a straight 3EF and now have a natural tap off point for my compensation scheme. It also allowed some simplification (component reduction).

Front end degeneration has also been reduced to increase the loop gain. Why not if you can keep good stability margins at the same time.

One interesting point is that increasing the cap across the feedback resistor actually makes the amp less stable into reactive loads. Not quite sure why... It does increase the PM of the OPS loop but when simmed into pure reactive loads the stability margins were worse overall. Even though the OPS loop had over 90 degrees PM. It's less important for the OPS loop to have massive PM. One nice thing about this amp is that it gets more stable as it heads towards the rails.

Also settled on Thermal Trak output transistors. They don't really add much complexity and I think are a neater solution.

On to the attachments:

1) Schematic

2) Loop around OPS

3) Loop stability into 100nF load as per schematic

4) Loop stability into 100nF load as per schematic with C15 = 33p

5) Loop stability into 100nF load as per schematic with C15 = 22p

6) Clipping

7) Loop around VAS

Think that's enough of an essay for now.

Paul

PS Apologies for the red trial version writing on the attachments. Sick of rebuilding this PC (haven't got a recent image) and haven't got any more patience until I get an SSD.

Been trying to get stability into pure reactive loads of 1n to 100n. The first problem was the bootstrapping on the pre-drivers. This caused large phase twists that destroyed all PM and GM.

So the first change, move to a 3EF with bootstrapped pre-drivers. Bootstrapped to keep the VAS happier. There was an increase in THD without the bootstraps.

This certainly helped matters but stability was still an issue. So the next change was to work out which loop needed the most stability. Turns out to be the VAS loop (I think

Now we have a straight 3EF and now have a natural tap off point for my compensation scheme. It also allowed some simplification (component reduction).

Front end degeneration has also been reduced to increase the loop gain. Why not if you can keep good stability margins at the same time.

One interesting point is that increasing the cap across the feedback resistor actually makes the amp less stable into reactive loads. Not quite sure why... It does increase the PM of the OPS loop but when simmed into pure reactive loads the stability margins were worse overall. Even though the OPS loop had over 90 degrees PM. It's less important for the OPS loop to have massive PM. One nice thing about this amp is that it gets more stable as it heads towards the rails.

Also settled on Thermal Trak output transistors. They don't really add much complexity and I think are a neater solution.

On to the attachments:

1) Schematic

2) Loop around OPS

3) Loop stability into 100nF load as per schematic

4) Loop stability into 100nF load as per schematic with C15 = 33p

5) Loop stability into 100nF load as per schematic with C15 = 22p

6) Clipping

7) Loop around VAS

Think that's enough of an essay for now.

Paul

PS Apologies for the red trial version writing on the attachments. Sick of rebuilding this PC (haven't got a recent image) and haven't got any more patience until I get an SSD.

Attachments

-

Schematic.jpg439 KB · Views: 272

Schematic.jpg439 KB · Views: 272 -

OPS Loop Vz0.png260 KB · Views: 260

OPS Loop Vz0.png260 KB · Views: 260 -

Stability 100nF.png305.9 KB · Views: 239

Stability 100nF.png305.9 KB · Views: 239 -

Loop Stability 100nF C15 33p.png301.6 KB · Views: 227

Loop Stability 100nF C15 33p.png301.6 KB · Views: 227 -

Loop Stability 100nF C15 18p.png299.1 KB · Views: 221

Loop Stability 100nF C15 18p.png299.1 KB · Views: 221 -

clipping.png154 KB · Views: 40

clipping.png154 KB · Views: 40 -

VAS Loop Vx.png286.3 KB · Views: 56

VAS Loop Vx.png286.3 KB · Views: 56 -

Draft1b.asc19 KB · Views: 44

Last edited:

BC327/BC337 as OPS driver?

BR, Toni

Thank you for pointing this out, it was an experiment... How could I have missed changing them back to the 2sa1930/2sc5171 pair?

Paul

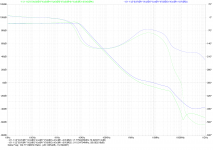

A little update...

Corrected the mistake pointed out by Tony.

Looks very stable in sims. See loop gain plots.

See loop gain plots.

Loop V(z0) PM = 88 degrees GM = 16dB

Loop V(x) PM = 112 degrees GM = 27dB

Paul

Corrected the mistake pointed out by Tony.

Looks very stable in sims.

Loop V(z0) PM = 88 degrees GM = 16dB

Loop V(x) PM = 112 degrees GM = 27dB

Paul

Attachments

Last edited:

Corrected the mistake pointed out by Tony. :

Hi Paul

Just been at the beach so I haven't had a close look at this but a few quick comments.

I think the simpler EF3 makes sense with this circuit and like the simplification it allows.

I have tried a CFP + EF but it didn't simulate as well, somewhat to my surprise.

If you plan just one pair of Thermal Traks then the 2SA1381 + 2SC3503 may be worth consideration as drivers.

They will be faster and lower capacitance, should help stability.

You need to check with your worst case load, but the smaller drivers may have adequate SOA if you don't drive the outputs into beta droop.

I think the lower LTP emitter resistors make sense for the reason you note, more loop gain, and a bit lower noise as a bonus.

It does reduce the effectiveness of the zero from the capacitor a little.

Hard to optimise this analytically, for me anyway.

What's the limitation to make it even smaller?

And what's the trade-off to increase it?

The current mirror emitter resistors probably would benefit from an increase.

Lower noise and the zero will be more effective.

Best wishes

David

Last edited:

Hi David,Hi Paul

Just been at the beach so I haven't had a close look at this but a few quick comments.

Ah the beach.

I think the simpler EF3 makes sense with this circuit and like the simplification it allows.

I have tried a CFP + EF but it didn't simulate as well, somewhat to my surprise.

I agree with using the simpler EF3. It makes sense from a design point of view. It's always nice after a period of minimal progress to have the pieces fall into place.

The idea of a CFP + EF has crossed my mind. Have tried simulating such things but as you found things weren't as good. Although I put it down to my ability. Don't really understand the CFP properly.

If you plan just one pair of Thermal Traks then the 2SA1381 + 2SC3503 may be worth consideration as drivers.

They will be faster and lower capacitance, should help stability.

You need to check with your worst case load, but the smaller drivers may have adequate SOA if you don't drive the outputs into beta droop.

Nice idea worth a closer look. Only plan on using one pair of outputs as this is only a low power amplifier. Also, multiple pairs bring extra problems that in mind were not worth the gains.

I think the lower LTP emitter resistors make sense for the reason you note, more loop gain, and a bit lower noise as a bonus.

It does reduce the effectiveness of the zero from the capacitor a little.

Hard to optimise this analytically, for me anyway.

What's the limitation to make it even smaller?

And what's the trade-off to increase it?

Have done a basic sim without the LTP emitter resistors. The result is workable after a few minor compensation changes.

An extra 3dB LG at 20kHz. Around 6dB of extra loop gain up to the pole at 10kHz.

Stability after emitter is now:

Loop V(z0) PM = 86 degrees GM = 14dB

Loop V(x) PM = 108 degrees GM = 23dB

As expected you have the classic trade off: Performance vs Stability.

It is still good into reactive loads though.

The current mirror emitter resistors probably would benefit from an increase.

Lower noise and the zero will be more effective.

Best wishes

David

Increased these a little but would it not increase the voltage headroom required by the amp?

Have attached the latest .asc

Paul

Attachments

Increased these a little but would it not increase the ... headroom required by the amp?

Yes, that's the trade-off.

But try for at least 260 mV across the emitter resistors, up to 1V.

And for future reference, even up to 2.6 V if you have elevated rails to the front end.

Best wishes

David

Yes, that's the trade-off.

But try for at least 260 mV across the emitter resistors, up to 1V.

And for future reference, even up to 2.6 V if you have elevated rails to the front end.

Best wishes

David

Gone for the full volt......

Here is another version of this amp with more loop gain and better stability into reactive loads.

Have also optimized output stage bias for lowest THD which is possibly the reason for the improved stability into reactive loads. Maybe the Gm profile is better now. Have to admit that haven't looked into this properly....

6 components lost and still got a good amp. There's probably more to come as this scheme can be optimized further...

Paul

P.S. Any comments on whether attachments are better embedded or not would be appreciated.

Attachments

Last edited:

Hi Guys

"One interesting point is that increasing the cap across the feedback resistor actually makes the amp less stable into reactive loads"

I found this to be particularly the case with CFP outputs. The problem arises with loads that are resistive too, if they are too low in value. So, I design for whatever the lowest load I expect and everything above that is happy.

Another weird thing was while compensating a simulated amp for lowest THD, the generator happened to be set at a high-ish voltage. Reducing the input signal caused the amp to oscillate. Have you encountered that?

Have fun

"One interesting point is that increasing the cap across the feedback resistor actually makes the amp less stable into reactive loads"

I found this to be particularly the case with CFP outputs. The problem arises with loads that are resistive too, if they are too low in value. So, I design for whatever the lowest load I expect and everything above that is happy.

Another weird thing was while compensating a simulated amp for lowest THD, the generator happened to be set at a high-ish voltage. Reducing the input signal caused the amp to oscillate. Have you encountered that?

Have fun

Hi Guys

"One interesting point is that increasing the cap across the feedback resistor actually makes the amp less stable into reactive loads"

I found this to be particularly the case with CFP outputs. The problem arises with loads that are resistive too, if they are too low in value. So, I design for whatever the lowest load I expect and everything above that is happy.

Another weird thing was while compensating a simulated amp for lowest THD, the generator happened to be set at a high-ish voltage. Reducing the input signal caused the amp to oscillate. Have you encountered that?

Have fun

The feedback cap (C21) is set to 1 Farad.

This amp has shown that exact behavior at times while experimenting with the compensation. Don't know why though. Need to look at this analytically, I think...

My mind is at it limits...

Last edited:

... Here is another version of this amp ...

At the risk of being completely wrong, my 2 cents on the bias spreader - I'm using a very similar spreader and I believe the ratio of R24/R22 controls the proportion of temperature coefficient contributed by Q17 and the ThermalTrak diodes, so I would not use R22 to set the bias voltage. I would use R23 to set the bias voltage, but that's problematic also if the trimmer fails open, so I paralleled a fixed resistor with a trimmer to give a range of resistance.

...6 components lost... There's probably more to come as this scheme can be optimized further...

"Less is more" as Robert B. said, so I want the most less

More comments later, need a new Internet service.

Best wishes

David

At the risk of being completely wrong, my 2 cents on the bias spreader - I'm using a very similar spreader and I believe the ratio of R24/R22 controls the proportion of temperature coefficient contributed by Q17 and the ThermalTrak diodes, so I would not use R22 to set the bias voltage. I would use R23 to set the bias voltage, but that's problematic also if the trimmer fails open, so I paralleled a fixed resistor with a trimmer to give a range of resistance.

R23/R24 ratio defines the multiplication factor for the TT diodes tempco and R22 does not influence that. Correct way to set the bias is to use variable R22.

R23/R24 ratio defines the multiplication factor for the TT diodes tempco and R22 does not influence that. Correct way to set the bias is to use variable R22.

Hi Dadod,

Could you elaborate this. My remark was based on Cordell Book p.306 (extract attached), is it one of those cases where there is an erratum in the book?

Thanks and regards.

Attachments

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Solid State

- Amp designed during lunch breaks