BBB-S03 connection update

Realised a mistake with the connections shown in previous posts. BBB P9 connector numberings!!! -apologies Wiring updated

Wiring updated

Also, when setup up this way there will no issues with power sequencing conditions that could damage the BBB. The isolators on the S03 board will effectively 'block' any voltages from going into the BBB if BBB is shutdown or unpowered while S03 is still active

For those who have BBB - connection as shown for full synchronous clocking. No cape necessary.

On-board clock of the BBB should be disabled (or removed) and use appropriately divided clock from S03 instead.

Currently BBB has single 24.576MHz clock support only so only one S03 XO (49.152MHz or 98.304MHz) needs to be mounted or enabled. If 98.304MHz used then you get 'Turbo' Sync capability to 9018 DACs. Of course other DACs like PCM1794 also possible with BCK out from S03 as MCK'

Sample frequencies are limited to 48K, 96K and 192K as result of this single clock of the BBB. If future versions allow dual audio clocks then full range of sample frequencies will be possible and then CKSEL can be used to automatically switch.

Until then upsampling 44.1k-based audio files using software utility is a suitable option

For those who wish to test S03 with BBB an update to the drivers can be found here -> http://bbb.ieero.com

Many thanks to Miero for his efforts!

Suitable setup as shown in the annex:

Realised a mistake with the connections shown in previous posts. BBB P9 connector numberings!!! -apologies

Also, when setup up this way there will no issues with power sequencing conditions that could damage the BBB. The isolators on the S03 board will effectively 'block' any voltages from going into the BBB if BBB is shutdown or unpowered while S03 is still active

Attachments

Cool, just ordered a BBB. So, we should be able to use cksel for for both 44.1 & 48 khz multiple clock freq with this setup? What would be the recommended clocks or clock frequencies for this configuration?

Thanks,

Chris

Yes, dual clock support to handle 44.1k and 48k based natively but need to configure clock support in BBB as per instruction shown here: http://bbb.ieero.com/

Scroll down to "HW and driver configuration" and then under "Clock Configuration":

Installed clocks are configurable via:

- kernel option snd_soc_botic.ext_masterclk

Examples:

0 ... no external clocks, just onboard for 48k freq (default)

1 ... external clock for 44k1 + onboard for 48k

2 ... external clock for 48k only

3 ... external clocks for 44k1 and 48k (needed for cape)

+4 ... invert polarity of clock selection switch GPIO0_15

Select option #3 above for dual clock inputs.

As for S03 clocks you can use either 45.1584MHz/49.152MHz and div/2 or 90.3168MHz/98.304MHz and div/4 to get the 22.5792/24.576MHz as required by BBB.

Probably, not directly over or under the dac pcb, with some horizontal distance but not to far because of the I2S data. This means I2S lines length with no more than 10cm, even less.Can you clarify what you mean by a sideways arrangement?

Thanks

I have a question(s) regarding Buffalo III and S03 boards. I've had removed the crystek oscillator in favor of synchronous clocking from the two oscillators on S03, in my case 90 and 98 MHz. Do we need any resistor for impedance matching when these tiny 50 ohm cables were used for the turbo clock line? Is there any better oscillators for 90 and 98 than si590?

When measuring power supply noise(with small as possible ground loop) I get about 190 mVpp on oscillator power pins. Maybe I should add few smd ceramic capacitors after the ferrite bead beside existing 10nf NP0?

Can you clarify what you mean by a sideways arrangement?

Thanks

Arrangement as shown in the diagram previously:

->here

Someone showed me a pic of his setup with everything stacked closely so as to 'shoehorn' into a compact enclosure. Nice and neat but when spaced out the system sounded much better. Whilst the digital side of SO3 switches with good swings and noise margins, the actual reference comes from the clocks that are powered by the ULN supplies and if this picks up interference then the jitter performance deteriorates. Placing SO3 board on top (or bottom) of BBB makes it susceptible to direct hits from processor noise and its switching supplies

The same goes for DAC also as pointed out by Miksi

Last edited:

BBB Support

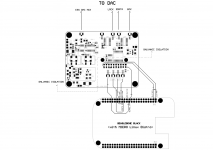

A quick preview of an add-on board for BBB that supports UPS

1. UPS kicks in when external power is removed. On-board PWR_MON will continue to power the BBB (~1hr) or options to safely shutdown BBB immediately. Same shutdown action if battery level goes below operational level

2. Automatic boot from SDCARD or internal Flash. No boot button press required.

3. Matching U.FL interfaces and PWR/CKSEL to the S03.

The above features will practically result in a reliable 'hands-free' system that can be tucked away

A quick preview of an add-on board for BBB that supports UPS

1. UPS kicks in when external power is removed. On-board PWR_MON will continue to power the BBB (~1hr) or options to safely shutdown BBB immediately. Same shutdown action if battery level goes below operational level

2. Automatic boot from SDCARD or internal Flash. No boot button press required.

3. Matching U.FL interfaces and PWR/CKSEL to the S03.

The above features will practically result in a reliable 'hands-free' system that can be tucked away

Attachments

Very nice! Any estimate on when the UPS cape will be available? And magnitude of cost?

Also consider adding an isolated I2C feed from the BBB through the S0x to the eventual DAC, that would be nice icing on the cake!

I've got a couple of S03's in my cart, have a couple of questions to you via email before I execute the order.

THANKS!

Greg in Mississippi

Also consider adding an isolated I2C feed from the BBB through the S0x to the eventual DAC, that would be nice icing on the cake!

I've got a couple of S03's in my cart, have a couple of questions to you via email before I execute the order.

THANKS!

Greg in Mississippi

If you are using short connections to the DAC MCK (which I will assume) then the impedance matching resistor (R1) on the S03 board will suffice.I have a question(s) regarding Buffalo III and S03 boards. I've had removed the crystek oscillator in favor of synchronous clocking from the two oscillators on S03, in my case 90 and 98 MHz. Do we need any resistor for impedance matching when these tiny 50 ohm cables were used for the turbo clock line?

Yes, there are better spec'd ones from NDK, SiLabs and Crystek but custom built-to-order only. Asking 50pcs min order plus thus usual export terms and all the end-user application queries. Price guide ~USD30 each. If there is sufficient interest I can arrange to supply these for DIY use.Are there any better oscillators for 90 and 98 than si590?

Alternatively, there is this new super XO from ULNOCXO (a.k.a Pulsar Clocks). Will set you back ~$1K+ for a dual XO setup but if your music is 48K based or resampled to these then single XO type will do. Needs its own board though as e.g in pic

Could you please check if this noise has the clock frequency signature or mains Hz. Additional filtering is fine hereWhen measuring power supply noise(with small as possible ground loop) I get about 190 mVpp on oscillator power pins. Maybe I should add few smd ceramic capacitors after the ferrite bead beside existing 10nf NP0?

Attachments

If you are using short connections to the DAC MCK (which I will assume) then the impedance matching resistor (R1) on the S03 board will suffice.

Yes, there are better spec'd ones from NDK, SiLabs and Crystek but custom built-to-order only. Asking 50pcs min order plus thus usual export terms and all the end-user application queries. Price guide ~USD30 each. If there is sufficient interest I can arrange to supply these for DIY use.

Alternatively, there is this new super XO from ULNOCXO (a.k.a Pulsar Clocks). Will set you back ~$1K+ for a dual XO setup but if your music is 48K based or resampled to these then single XO type will do. Needs its own board though as e.g in pic

Could you please check if this noise has the clock frequency signature or mains Hz. Additional filtering is fine here

I'll begin from the end. Noise is influenced by the clock frequency. With additional 10nF caps I've managed to lower it almost 3x. I'm talking about caps directly across oscillators. I would add some on dividers and reclock ICs.

For diyer, pulsar clocks is maybe a over kill, because one need to pay attention to the minute detail so that invested money have some(audible) sense. NDK or Crystek are far more attractive so if we can find the best candidate(for 90 and 98) then I'm in for the GB. I hope we can reach min required quantity.

Turbo MCK line is 10cm in length. Off course, on BIII there are no matching resistors. I have a separate power supply units for each power pin on S03 and there is a Ian's adapter for data lines for BIII.

... Any estimate on when the UPS cape will be available? And magnitude of cost?

Also consider adding an isolated I2C feed from the BBB through the S0x to the eventual DAC, that would be nice icing on the cake!

...

It will take ~2-4wks to firm up everything for pricing and availability. I will be a fully populated board. "Batteries not included ..."

Yes, isolated I2C will be good but prefer to be on the UPS cape rather than going through the S03 board. So no changes to the S03 board

Thanks for your input

...when is the new S04 board ready? and will you sell it without the amanero?

In design review-TBA. Plans to go up to 8CH re-clocking

Will be made available on its own. Not tied to any particular transport

I'll begin from the end. Noise is influenced by the clock frequency. With additional 10nF caps I've managed to lower it almost 3x. I'm talking about caps directly across oscillators. I would add some on dividers and reclock ICs.

For diyer, pulsar clocks is maybe a over kill, because one need to pay attention to the minute detail so that invested money have some(audible) sense. NDK or Crystek are far more attractive so if we can find the best candidate(for 90 and 98) then I'm in for the GB. I hope we can reach min required quantity.

Turbo MCK line is 10cm in length. Off course, on BIII there are no matching resistors. I have a separate power supply units for each power pin on S03 and there is a Ian's adapter for data lines for BIII.

Thanks Miksi, all noted

I am waiting for further information from Crystek.

SiLabs and NDK have submitted theirs:

SiLabs based on Si570 but without I2C. 98.304/90.3168MHz clocks by line select in a single package. See Si570 for performance specs

NDK NZ25xx series with 98.304MHz and 90.3168MHz. Phase noise performance comparable to Crystek's CCHD575, -120db @100Hz and -162db @1Mhz

<SNIP>

Yes, isolated I2C will be good but prefer to be on the UPS cape rather than going through the S03 board. So no changes to the S03 board

Thanks for your input

That makes sense. Thanks for the response!

Greg in Mississippi

I am waiting for further information from Crystek.

SiLabs and NDK have submitted theirs:

SiLabs based on Si570 but without I2C. 98.304/90.3168MHz clocks by line select in a single package. See Si570 for performance specs

NDK NZ25xx series with 98.304MHz and 90.3168MHz. Phase noise performance comparable to Crystek's CCHD575, -120db @100Hz and -162db @1Mhz

Clock GB now open:

https://docs.google.com/spreadsheet/ccc?key=0AjMtoJzE9WFgdDF6bDZMcTNDWlh1MkdnaFpMcXdROUE&usp=drive_web#gid=0

Hi Acko. Will the SO4 board be available as a bare board or only fully assembled?

Fully assembled only with choice of clocks mounted:

>3 I2S input ports, multiplexed

>2-8 Channel isolated and re-clocked outputs

Please note: S03 board will not be phased out.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Group Buys

- Amanero Isolator/Reclocker GB